锁相环性能度量标准包括品质因数、噪声基底、闪烁噪声模型。

一个理想锁相振荡器的相位噪声主要取决于以下因素:

a.VCO的频率和鉴相器;

b.VCO的灵敏度kvco、VCO和参考振荡器相位噪声曲线;

d.工作模式:整数、小数调制样式。

(1)PLL相位噪声

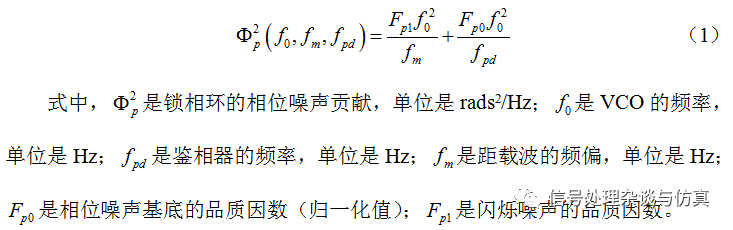

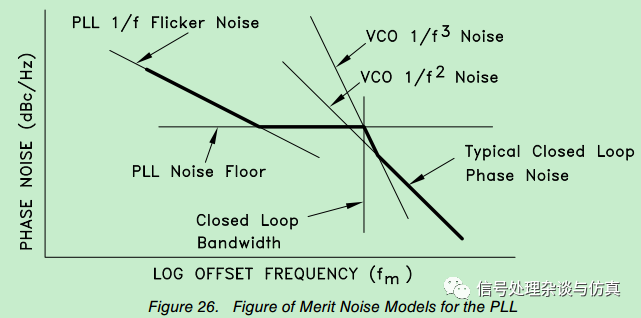

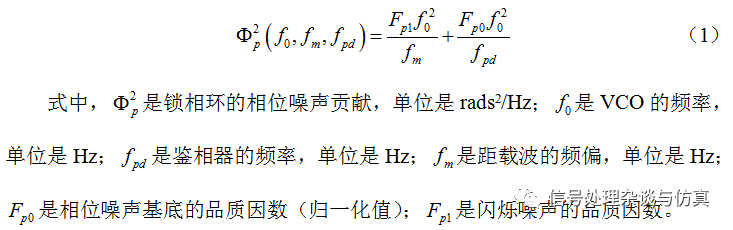

锁相环对输出相位噪声的贡献可以用PLL噪声基底及PLL闪烁噪声(又叫1/f噪声)的品质因数来表征,见下式(1):

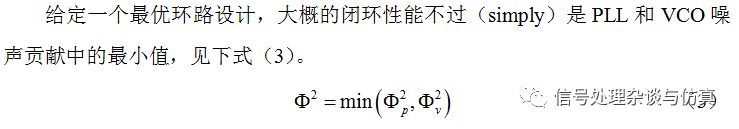

(3)品质因数的计算方法

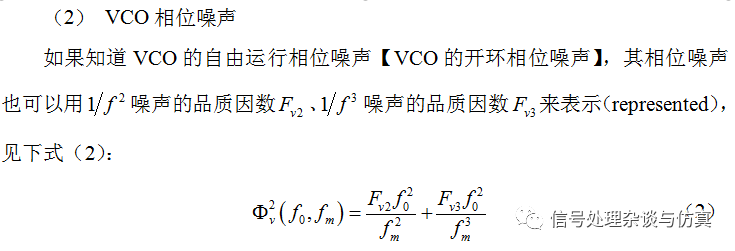

品质因数(FOM)本质上是PLL和VCO的归一化噪声参数,它有助于快速评估PLL在所要求的VCO、频偏及鉴相器频率下的性能水平。一般来说,合成器在闭环带宽内以PLL IC噪声为主;在环路带宽外(在远离载频的频偏)以VCO开环相位噪声为主。

因此,通过将环路带宽设置为PLL相位噪声曲线与VCO自由运行相位噪声曲线相交点对应的频率值【即PLL相位噪声曲线与VCO开环相位噪声曲线相交于一点,环路带宽等于该点对应的频率】,来快速评估PLL的闭环性能。

品质因数在估计噪声参数时也有用,这些噪声参数会输入到闭环设计工具(比如Hittite PLL Design),Hittite PLL Design工具能够给出关于闭环相位噪声的更准确评估,以及PLL环路滤波器的元件值。

-

锁相环

+关注

关注

35文章

590浏览量

87969 -

振荡器

+关注

关注

28文章

3861浏览量

139521 -

鉴相器

+关注

关注

1文章

61浏览量

23371 -

环路滤波器

+关注

关注

3文章

26浏览量

13216 -

PLL技术

+关注

关注

0文章

10浏览量

3700

发布评论请先 登录

相关推荐

锁相环性能度量标准

锁相环性能度量标准

评论