芯片的开发与进步构成尺寸和厚度的变化。最新的晶元封装设计需要推栈芯片或硅粘合到硅上,这会导致组件彼此的形状及其粘合强度发生变化。

三种设计使测试变得困难:

降低芯片厚度与芯片粘合面积的比率

薄芯片随芯片和基板翘曲

硅直接粘合到硅或其他类似材料上(增加粘合强度)

(1)降低芯片厚度与芯片粘合面积的比率

降低芯片厚度与芯片粘合面积的比率与剪切测试有关。 实际问题是随着芯片变薄,将测试负载区域减少到粘合区域。推刀将测试载荷施加到芯片的侧面区域。

当芯片较薄时,施加测试载荷的区域较小。随着芯片厚度的减小,会出现这一点,推刀和芯片之间的测试应力,比粘结应力更早达到峰值。芯片在粘合失效之前失效,因此不测量粘接强度。

(2)薄芯片随芯片和基板翘曲

翘曲的芯片和基板会增加芯片上的变形负载 ,从而导致其在粘合失效之前断裂

(3)硅直接粘合到硅或其他类似材料上(增加粘合强度)

由于粘接的面积远大于测试载荷的面积,因此芯片将在粘接前的测试载荷施加点失效。因此,通常无法测试这样的样品。

让测试变得so easy,多功能推拉力测试仪给你高精度的自动化体验!

推拉力测试机

推拉力测试机首先,这款推力测试仪的自动化功能真是太赞了!只需要将要测试的芯片夹入夹具,设定测试参数,然后轻轻一按按钮,就能自动完成推力测试啦!不用再手动操作,省心省力好方便!

而且不止省心省力,而且精度高!它采用了高精度传感器和先进的控制技术,可以精确地测量芯片的推力。再也不用担心测试结果出现偏差啦!

除此之外,这款推力测试仪还有一个超级棒的特点,就是它的操作非常简单易懂!即使是小白也能轻松上手哦!只需要按照说明书上的步骤操作,就能快速完成测试,真的非常友好!

还有,它的测试速度也非常快!只需几秒钟,就能得到准确的测试结果!再也不用像以前一样等上好久才能知道芯片的牢固程度了,真是太方便了!

总的来说,这款推力测试仪简直是芯片界的神器!自动化功能让测试变得轻松愉快,高精度保证了测试结果的准确性,操作简单易懂,测试速度快,真的是太完美了!千万不要错过哦!如果你也对这台芯片推力测试仪感兴趣,快来了解一下!它一定会给你的工作带来巨大的便利和效率提升!

-

芯片

+关注

关注

463文章

54422浏览量

469235 -

测试

+关注

关注

9文章

6402浏览量

131669 -

封装

+关注

关注

128文章

9330浏览量

149039

发布评论请先 登录

多功能推拉力测试机:工业测试的“全能卫士”实用知识与技能

COB元器件推拉力测试怎么做?推拉力测试机选型指南+实测演示

PCB焊接质量对比测试怎么做?推拉力测试机应用实测

电路板电阻推力测试怎么做?推拉力测试机测试方法与标准解析

电子元器件剪切强度测试怎么做?推拉力测试机方法详解

多功能推拉力测试机是集高精度、多功能于一体的力学检测设备

光学组件推力测试怎么做?推拉力测试机操作使用

PCB板焊点高低温环境下强度测试|推拉力测试机选型指南+实测演示

基于推拉力测试机的PCBA电路板元器件焊点可靠性评估与失效机理探讨

从理论到实践:推拉力测试机在微电子封装失效分析中的关键作用

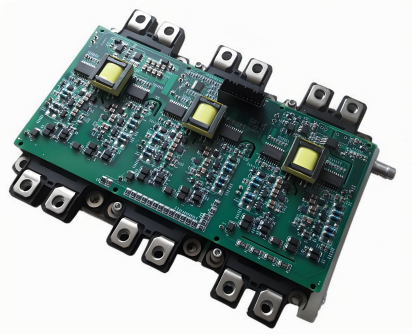

揭秘推拉力测试机:如何助力于IGBT功率模块封装测试?

AEC-Q102之推拉力测试

封装推拉力测试机解决设计使测试变困难的问题

封装推拉力测试机解决设计使测试变困难的问题

评论