”前面的文章介绍逻辑算术运算芯片(SN74181)实现4位的逻辑和算术运算,用两个芯片级连实现8位运算。目标是逐步实现一个简单的8位CPU的芯片逻辑”

01实验内容

1.1 实验内容

研究逻辑算术芯片SN74181的进位原理,用两个芯片级连实现8位的ALU(algorithm logic unit / 计算逻辑单元)。希望从现在开始能够逐步实现一个最最简单的8位CPU逻辑,具有8位的ALU是第一步。

1.2 知识点

计算机能够进行复杂的计算,其核心就是基本的逻辑运算(与、或、非等)和算术计算(加法等)。

02实验准备

2.1 实验器材

要完成本次实验,我们需要如下的元器件。

2.2 元器件解释

SN74181芯片:

接前一篇,级联的关键

2.3 芯片级联的工作原理

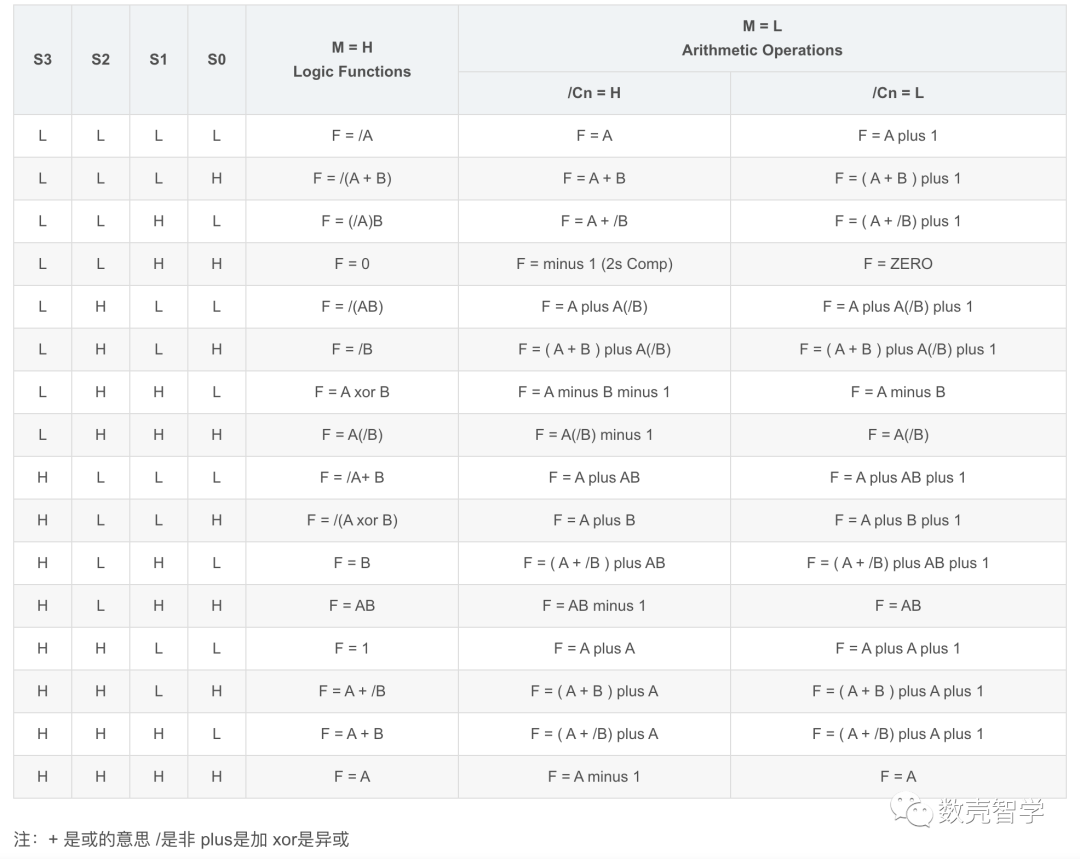

关键是将低4位芯片的Cn+4针脚连接高4位芯片的Cn针脚(如图2),观察SN7481芯片的逻辑(如图1),低4位的Cn+4输出作为高4位芯片的Cn输入

低4位芯片设置M=H Cn=H进行算术运算,当无需进位时Cn+4 = H,则高4位芯片进行如图1的“Cn=H"的操作。当低4位计算之后需要进位的时候,Cn+4 = L,则高4位芯片进行如图1的“Cn=L”的操作,实现高4位+1操作。如此完成8位的算术运算。

图1 SN74181芯片运算逻辑图

03实验过程

3.1 接线

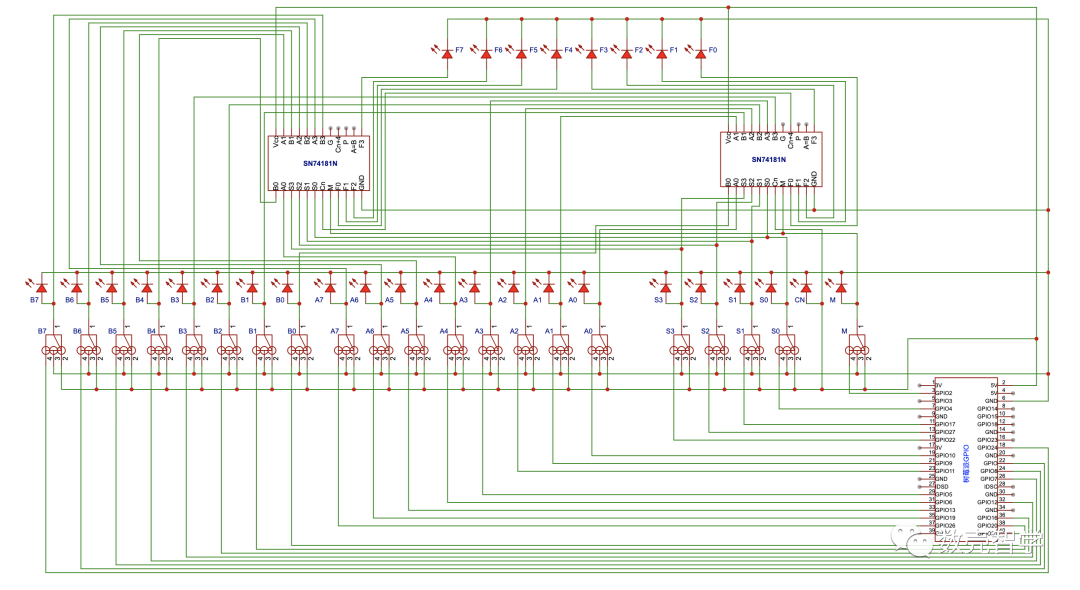

图2 SN74181芯片级联成8位ALU电路图

说明:

1、通过开关选择两种模式可以测试芯片,开关全部置4,由树莓派GPIO控制针脚电压;开关置2表示给连接针脚高电压;开关置3表示给连接针脚低电压

2、图中红色线为关键的连接线

3、请按照上图进行实际的连线,树莓派代码也按照上图针脚设置

3.2 实验步骤

3.3 实验代码

04实验展示

-

芯片

+关注

关注

458文章

51419浏览量

428636 -

cpu

+关注

关注

68文章

10929浏览量

213424 -

计算机

+关注

关注

19文章

7563浏览量

88847 -

ALU

+关注

关注

0文章

33浏览量

13150

发布评论请先 登录

相关推荐

两个4位加法器级联构成一个8位加法器 verilog怎么写啊?!!

使用Robei利用verilog语言做ALU设计

8位alu设计

两片4通道AD芯片如何级联实现8通道的模拟信号采集

am335x evm外接两个8位的nand flash

FPGA实现32位ALU软核设计

两个74ls164怎么连?74ls164联级应用电路

两个74HC595D驱动芯片控制三位数码管显示

用VHDL语言创建一个8位算术逻辑单元(ALU)

8位通用总线收发器和两个带拆分LVTTL端口反馈路径和3态输出的1位总线收发器SN74VMEH22501A-EP数据表

使用两个SN74181芯片级联实现8位ALU

使用两个SN74181芯片级联实现8位ALU

评论