CMOS器件的输入信号上升时间或下降时间统称为输入转换时间,输入转换时间过长也称为慢CMOS输入。如果输入信号上升时间过长,超过器件手册允许的最大输入转换时间,则有可能在器件内部引起大的电流浪涌,造成器件损坏或引起器件输出电平翻转(输入原本为0,输出为1;或者相反情况)。

1.慢CMOS输入或浮空CMOS输入的特征

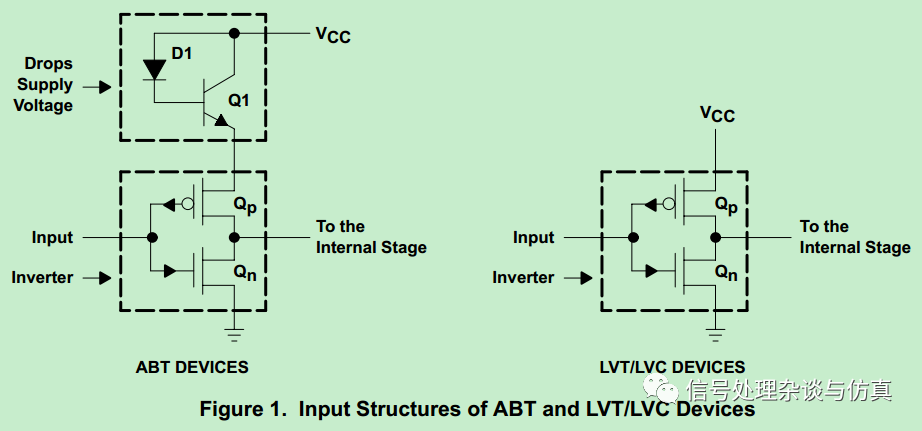

CMOS和BiCMOS系列器件都有一个CMOS输入结构。该结构是一个反相器(包括连接VCC的一个p沟道晶体管和连接GND的一个n沟道晶体管),如图1所示。

备注:图1中的ABT器件采用BiCMOS技术,Q1是双极晶体管,Qp和Qn是CMOS管子,ABT器件的输入为CMOS反相器(又叫倒相器、非门(NOT gate,非电路)和逻辑否定电路);关于CMOS反相器,参见文档《CMOS功耗和Cpd计算》。

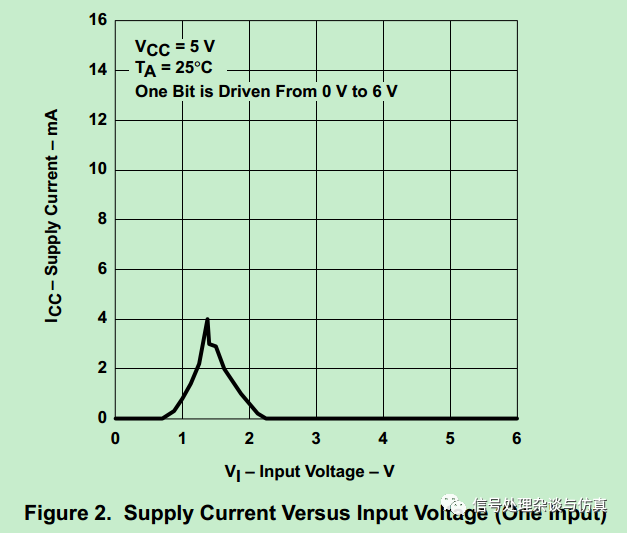

当输入为低电平,p沟道晶体管导通,n沟道晶体管截止,电流从VCC流出,节点被拉高;当输入为高电平,p沟道晶体管截止,n沟道晶体管导通,电流流入GND,节点被拉低。在两种情况下,没有电流从VCC流到GND。然而,当从一个状态转换到另一个状态时,输入穿过阈值区域,使得n沟道晶体管和p沟道晶体管同时导通,在VCC与GND之间形成电流路径。该电流浪涌可能是破坏性的,它取决于输入在阈值区域(0.8~2V)的时间长度。每个输入的供电电流(ICC)能够升到几mA,ICC在输入(VI)约为1.5V时最大,见图2。

备注:当输入穿过阈值区域,在VCC与GND之间的电流路径也叫直通电流,直通电流会造成器件的瞬态功耗,详情参见文档《CMOS功耗和Cpd计算》。从图2中看出,当输入电压在阈值区域内(0.8~2V)时,供电电流存在浪涌。

当开关状态在数据手册指定的输入转换时间限值内时,电流浪涌不是问题。对于具体器件,在数据手册的推荐工作条件表中指定输入转换时间限值,例子如图3所示。

2.慢输入沿率

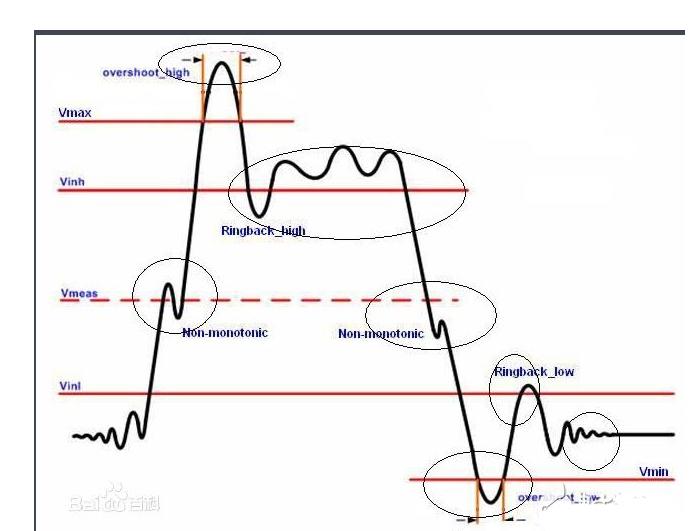

随着速度增加,逻辑器件已经对慢输入沿率更敏感。慢输入沿率与噪声(当输出开关时,在电源上产生)一起能够引起大量输出错误或振荡。如果没有用到的输入管脚悬空或者未保持在一个有效的逻辑电平值,类似现象也能够发生。

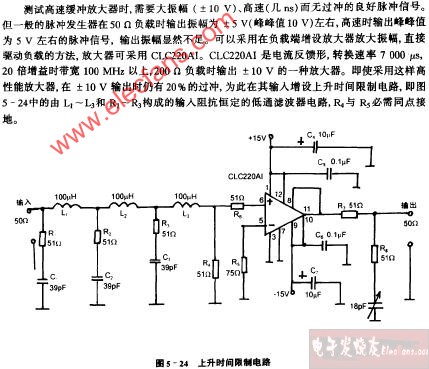

这些功能问题是由在器件电源系统引起的电压瞬态造成的,在开关过程中,当输出负载电流(IO)流过寄生引线电感时产生电压瞬态,见图4。

因为器件的内部电源节点用作整个集成电路的电压参考,感应电压尖峰VGND影响出现在内部门结构的信号方式【指VI′=VI-VGND】。例如,当器件地节点的电压升高时,输入信号VI′看起来在幅度上减小。如果发生阈值违背(指输入信号原本为高电平,由于VI′小于器件输入端高电平的阈值VIH,造成输出错判为低电平;反之亦成立),这种不期望现象随后能够错误地改变输出。

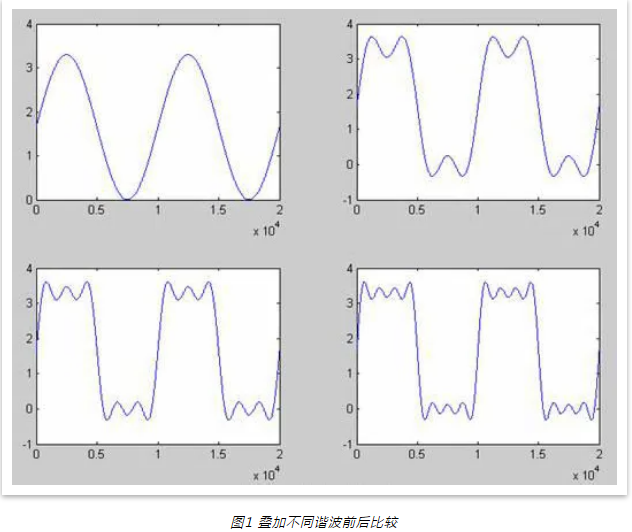

对于一个慢的输入上升沿,如果在GND的电压变化足够大【VGND】,器件的相对输入信号VI′看起来被驱动返回穿过输入阈值区(0.8~2V),输出开始从相反方向开关(指0变成1,1变成0)。如果最坏情况(所有输出同时开关,造成瞬态负载电流较大)频繁发生(参见图2和图3),慢输入沿被重复地驱动返回穿过阈值区,引起输出振荡。因此,不应该违背器件的最大输入转换时间,也就不会造成对电路或外部封装的损坏。

-

CMOS

+关注

关注

58文章

6229浏览量

243359 -

反相器

+关注

关注

6文章

332浏览量

45323 -

晶体管

+关注

关注

78文章

10434浏览量

148543 -

输入信号

+关注

关注

0文章

559浏览量

13211 -

CMOS器件

+关注

关注

0文章

75浏览量

12166

发布评论请先 登录

示波器的那些事-示波器上升时间

关于信号上升时间和传输延时的关系

BOB示波器信号上升时间的劣化

BOB示波器输入信号上升时间的测量

信号完整性分析:信号上升时间

高速pcb设计中的信号上升时间是如何定义的

浅谈振荡上升时间及影响

信号频率和上升时间的关系

信号上升时间与带宽的关系 一文看懂!!!

CMOS器件的输入信号上升时间为什么不能太长?

CMOS器件的输入信号上升时间为什么不能太长?

评论