对于PLL小白而言,往往从VCO开始,因为惯性认为VCO的噪声最难优化,有时为了简化(偷懒)会忽略Divider、Refclk、甚至PFD+CP上的噪声,但对于时钟要求很高的场合会抠每个模块的噪声,这种做法并不可取。

之前跟大家分享的PLL噪声优化技术中提到的Xilinx54fsrms Jitter带内噪声是通过16nm FinFET工艺和功耗(45mW)以及超低参考时钟Jitter(-145dBc/Hz@ 1MHz)换来的,拼的是工艺而且对参考时钟抖动要求非常高,Xilinx用在自家成熟的FPGA产品中,侧重的是性能并不care功耗甚至成本。

Samsung用在自家5G蜂窝移动通信中的PLL^[1]^,采用28nmBulk工艺Jitter做到了75fsrms,采用SamplingPhase Detector(SPD)技术实现带内噪声的优化。Xilinx在文献[2]中也采用了这种技术,SPD开启后带内噪声最大优化了13.4dB。

本期跟大家聊聊SPD如何降低带内噪声及其工作原理,希望对大家有所启发。

1. 为什么要引入SPD

PLL噪声可分为带内和带外两部分,带外噪声由VCO占主导,带内噪声由Refclk、Divider、PFD+CP占主导。传统电荷泵PLL中带内噪声主要由PFD+CP贡献,由于分频器的作用,噪声会被放大N^2^倍到输出且PFD鉴相死区的存在使PFD+CP本身噪声贡献也会比较大。所以在通常情况下,传统电荷泵PLL带内噪声一般很难优化。在超高频RFIDPLL中将环路带宽做的很小,来抑制带内噪声,但这会增加锁定时间且VCO噪声无法被充分抑制,芯片面积也会增加。

SPD即采样鉴相器,也有SSPD(Sub-SamplingPhase Detector)即亚采样鉴相器两者都是基于采样原理,区别在于SSPD是用refclk直接采样VCO输出(低采高,所以称为亚采样),SPD是用refclk采样VCO经N分频后的fbclk。

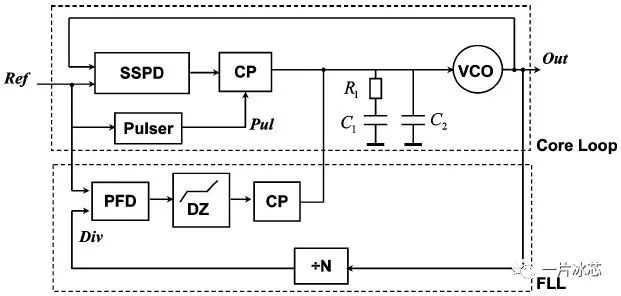

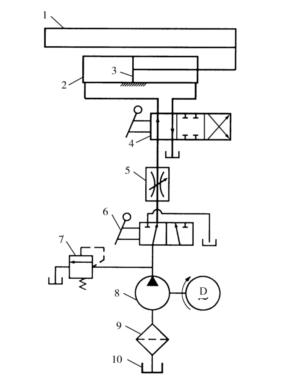

参考文献[3-5]给出的亚采样锁相环(SSPLL)结构如图1所示,可以在带宽较大时实现低带内噪声。SSPLL由采样环和锁频环(FLL)构成,在环路锁定时,仅有采样环工作,由于分频器不参与环路工作,SSPD和CP噪声不会被放大N^2^倍且鉴相器分辨率也很高。

Fig1. SSPLL结构框图

2. SPD****原理

图2给出了SPD结构及时序图,VCO输出频率被ref采样,采样后的输出电压为Vsam。假设VCO输出信号直流电平为V DC ,VCO输出信号与ref信号对齐且二者频率刚好是整数倍,采样电压Vsam恰好等于V DC ,相位锁定;VCO信号与ref有相位偏差时,Vsam就会偏离V DC 。

Fig2. SPD结构及时序图

3. SPD和SCP

**3.1 **亚采样结构

图3给出了亚采样PD和CP结构,其中sspd用于采样保持ckp和ckn在refclkp上升沿时刻的DC值,pulser产生一个小脉宽用于控制sscp开启时间,sscp将采样得到的电压差转换成电流灌入后级的滤波器。pulser中添加反相器对(图中红色方框),可以减小反相器与传输门之间的延时失配,从而得到匹配性更好的单端到差分的转换。

Fig3. 亚采样PD和CP结构

文献[4]给出了sspd和sscp的级联增益:

A ss =2g m *A VCO *T pul /Tref

其中gm为sscp输入管的跨导,Avco为VCO输出摆幅,Tpul为pul脉宽,Tref为ref周期。

isscp输出端加10pF负载时控制电压(vctrl)波形如图4所示,其中td为refclkp和ckp的相差,可见亚采样PD和CP可分辨出20fs(-500f~500f,扫描50个点)甚至更低的相差。

Fig4. 亚采样PD和CP仿真结果

3.2 Xilinx SPD****结构

Xilinx SPD结构如图5所示 ^[2]^ ,与之前结构的区别是该结构ref时钟采样的是VCO N分频后的div。

Fig5. XilinxSPD结构

PLL测试结果如图6所示,可见SPD开启后带内噪声优化了13.4dB,RMS Jitter优化了230fs。

Fig6. XilinxSPD结构RMS Jitter测试结果 @ 18GHz

3.3 Samsung SPD****结构

Samsung SPD结构如图5所示 ^[1]^ ,采用VCO N分频后的CLKFB采样refclk插值后的时钟。

Fig7. SamsungSPD结构

-

锁相环

+关注

关注

35文章

583浏览量

87733 -

VCO

+关注

关注

12文章

190浏览量

69177 -

鉴相器

+关注

关注

1文章

60浏览量

23271 -

SPD

+关注

关注

1文章

159浏览量

19669 -

PLL电路

+关注

关注

0文章

92浏览量

6402

发布评论请先 登录

相关推荐

SRAM的工作原理及其使用方法了解

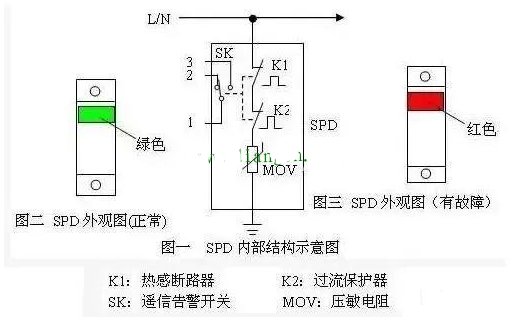

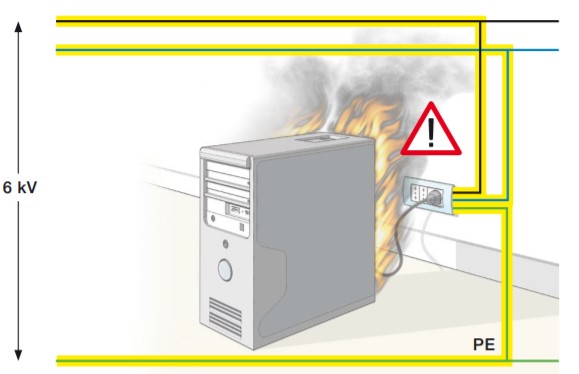

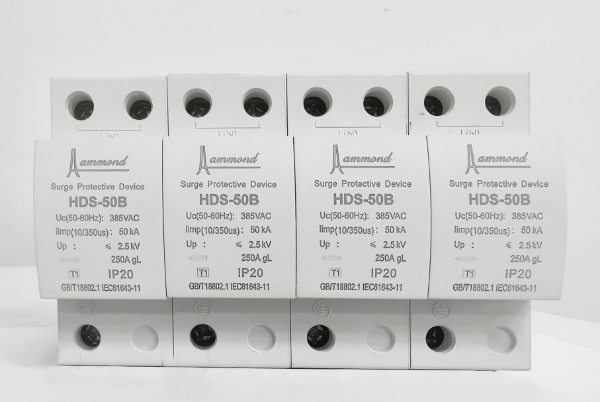

电涌保护器(SPD)的工作原理及结构

浪涌保护器SPD的工作原理

浪涌保护器的工作原理(SPD)

闪烁噪声的工作原理

什么是SPD防雷装置?SPD的工作原理及作用

聊聊SPD如何降低带内噪声及其工作原理

聊聊SPD如何降低带内噪声及其工作原理

评论