逻辑单元在FPGA器件内部,用于完成用户逻辑的最小单元

逻辑单元在ALTERA叫作(Logic Element,LE)LE,在XILNX中叫作LC(LOGIC CELL).

1.逻辑单元与逻辑阵列

逻辑单元(Logic Element,LE)在FPGA器件内部,用于完成用户逻辑的最小单元。一个逻辑阵列包含16个逻辑单元以及一些其他资源, 在一个逻辑阵列内部的16个逻辑单元有更为紧密的联系,可以实现特有的功能。

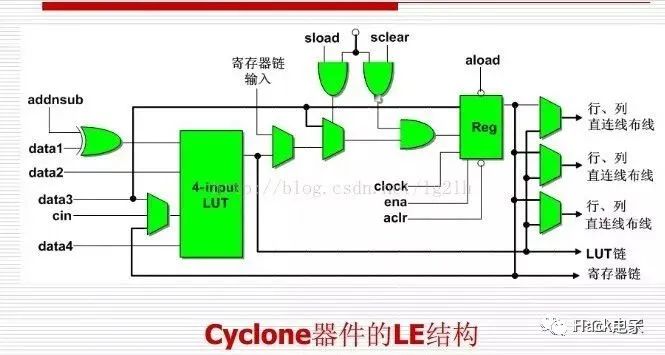

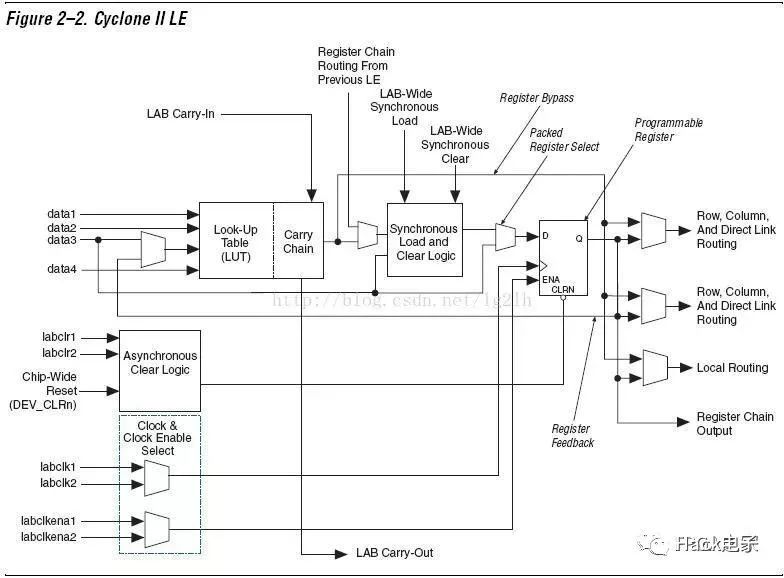

一个逻辑单元主要由以下部件组成:一个四输入的查询表(LookUp Table,LUT),一个可编程的寄存器,一条进位链,一条寄存器级连链。

1、查询表:用于完成用户需要的逻辑功能,CYCLONEⅡ系列的查询表是4输入1输出的,可以完成任意4输入1输出的组合逻辑。

2、可编程寄存器:可以配置成D触发器,T触发器,JK触发器,SR触发器。每个寄存器包含4个输入信号,数据输入、时钟输入、时钟使能、复位输入。

一个逻辑单元包含3个输出,两个用于驱动行连接、列连接、直接连接,另外一个用于驱动本地互联。这三个输出是相互独立的。输出信号可以来自于查询表也可以来自于寄存器。

一个LE主要由两部分组成:查找表LUT+可编程寄存器

1.本地互连通路

是逻辑阵列的重要组成部分,芯片级设计思路上的考虑与节省我们就不讨论,从实际运用出发,直接看看这个互连通路是干什么用的。本地互连通路提供了一种逻辑阵列内部的连接方式, 逻辑阵列内部还包含一种对外的高速连接通路,称之为直接连接通路。

直接连接通路连接的是相邻的逻辑阵列,或者与逻辑阵列相邻的M4K存储器块、乘法器、锁相环等。

CYCLONEⅡ系列FPGA的逻辑单元有两种工作模式:普通模式和算数模式。普通模式适合于一般的逻辑运算。算数模式适用于实现加法器、计数器、累加器、比较器等。

逻辑阵列的主体是16个逻辑单元,另外还有一些逻辑阵列内部的控制信号以及互连通路。前面所讲的互联通路和直接连接通路就是逻辑阵列中的部分。

逻辑阵列还包括一些控制信号:两个时钟信号,两个时钟使能信号,两个异步复位信号,一个同步复位信号,一个同步加载信号。

2.内部连接通路

在FPGA内部存在各种连接通路,连接不同的模块,比如逻辑单元之间、逻辑单元与存储器之间。FPGA内部资源是按照行列的形式排列的,所以连接通路也分为行列的。行连接又分为R4连接、R24连接和直接连接。R4连接就是连接4个逻辑阵列,或者3个逻辑阵列和1个存储块, 或者3个逻辑阵列和1个乘法器。简单地说就是连接4个模块吧。R24就是24个模块。列连接是C4,C16,含义不用说了吧,是连接4个模块和16个模块。

ALTERA的LE内部结构如图

*

*

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21742浏览量

603532 -

寄存器

+关注

关注

31文章

5343浏览量

120400 -

LUT

+关注

关注

0文章

49浏览量

12509 -

逻辑单元

+关注

关注

0文章

25浏览量

5125

原文标题:FPGA基础之逻辑单元的基本结构

文章出处:【微信号:ZYNQ,微信公众号:ZYNQ】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于BIST利用ORCA结构测试FPGA逻辑单元的方法

FPGA学习笔记汇总(7.13更新)

【案例分享】玩转FPGA必学的复杂逻辑设计

时序逻辑:FPGA/ASIC电路结构

FPGA学习笔记:逻辑单元的基本结构

FPGA学习笔记:逻辑单元的基本结构

评论