具有Cache的计算机,当CPU需要进行存储器存取时,首先检查所需数据是否在Cache中。如果存在,则可以直接存取其中的数据而不必插入任何等待状态,这是最佳情况,称为高速命中;

当CPU所需信息不在Cache中时,则需切换存取主储器,由于速度较慢,需要插入等待,这种情况称高速未命中;

在CPU存取主存储器的时候,按照最优化原则将存储信息同时写入到Cache中以保证下次可能的高速缓存命中。

因此,同一数据可能同时存储在主存储器和Cache中。同样,按照优化算法,可以淘汰Cache中一些不常使用的数据。

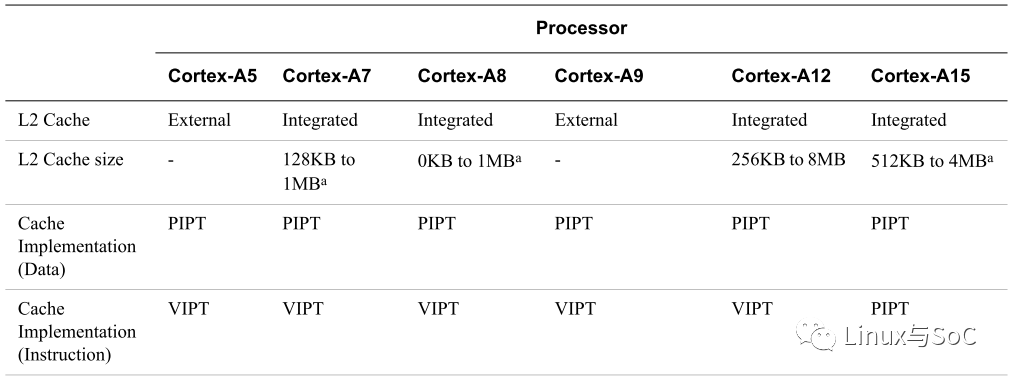

传统的Socket架构通常采用两级缓冲结构,即在CPU中集成了一级缓存(L1Cache),在主板上装二级缓存(L2 Cache),而SlotⅠ架构下的L2 Cache则与CPU做在同一块电路板上,以内核速度或者内核速度的一半运行,速度比Socket下的以系统外频运行的L2 Cache更快,能够更大限度发挥高主频的优势,当然对Cache工艺要求也更高。

•CPU首先在L1 Cache中查找数据,如找不到,则在L2Cache中寻找。

•若数据在L2 Cache中,控制器在传输数据的同时,修改L1Cache;

•若数据既不在L1 Cache中,又不在L2 Cache中,Cache控制器则从主存中获取数据,将数据提供给CPU的同时修改两级Cache。

•K6-Ⅲ则比较特殊,64KB L1 Cache,256KB Full Core Speed L2 Cache,原先主板上的缓存实际上就成了L3 Cache。

根据有关测试表明:

当512K2MB的三级缓存发挥作用时,系统性能还可以有2%10%的提高;

Tri-level成为PC系统出现以来提出的解决高速CPU与低速内存之间瓶颈最为细致复杂的方案;而且,今后Cache的发展方向也是大容。

在主存-Cache存储体系中,所有的指令和数据都存在主存中,Cache只是存放主存中的一部分程序块和数据块的副本,只是一种以块为单位的存储方式。

Cache和主存被分为块,每块由多个字节组成。

由上述的程序局部性原理可知,Cache中的程序块和数据块会使CPU要访问的内容在大多数情况下已经在Cache中,CPU的读写操作主要在CPU和Cache之间进行。

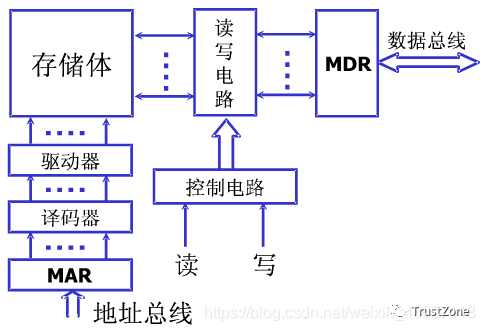

CPU访问存储器时,送出访问单元的地址,由地址总线传送到Cache控制器中的主存地址寄存器MAR,主存-Cache地址转换机构从MA获取地址并判断该单元内容是否已在Cache中存有副本,如果副本已存在于Cache中,即命中。当命中时,立即把访问地址变换成它在Cache中的地址,然后访问Cache。

•存储体由若跟个存储单元组成,存储单元由多个存储元件组成

•存储体----存储单元(存储一串二进制串)----存储元件(存储一个0/1)

•存储单元:存放一串二进制代码。

•存储字:存储单元中的二进制代码

•存储字长:存储单元中二进制代码位数。

•存储单元按照地址进行寻址

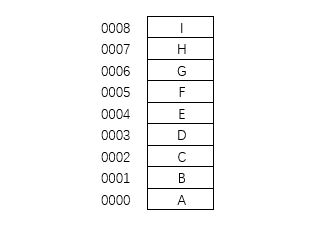

•MAR:存储器地址寄存器,反应存储单元个数。保存了存储体的地址(存储单元的编号),反应了存储单元的个数。所以MAR的位数和存储单元的个数有关。

•MDR:存储器数据寄存器,反应存储字长(存储单元长度)。保存了要送入CPU中的数据或要保存到存储体中的数据或者刚刚从存储体中取出来来的数据。这个寄存器的长度和存储单元的长度相同。

如果CPU要访问的内容不在Cache中,即不命中,则CPU转去直接访问主存,并将包含此存储单元的整个数据块(包括该块数据的地址信息)传到Cache中,使得以后的若干次对内存的访问可转化为对Cache的访问。

若Cache存储器已满,则需在替换控制部件的控制下,根据某种替换算法/策略,用此块信息替换掉Cache中原来的某块信息。

之前记得当时面试的时候让我用golang手写缓存管理算法,哈哈哈。

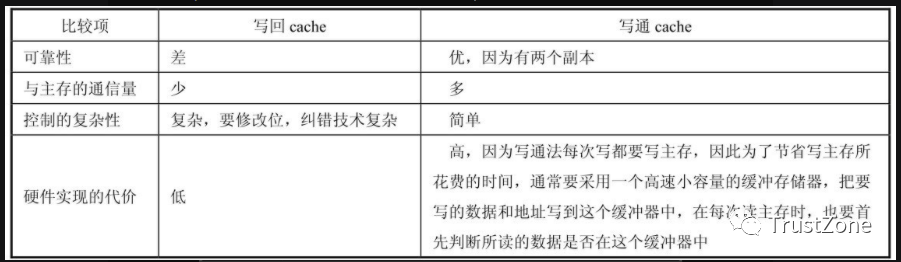

所以,要想提高系统效率,必须提高Cache命中率,而Cache命中率的提高则取决于Cache的映像方式和Cache刷新算法等一系列因素,同时Cache中内容应与主存中的部分保持一致,也就是说,如果主存中的内容在调入Cache之后发生了变化,那么它在Cache中的映像也应该随之发生相应改变,反之,当CPU修改了Cache中的内容后,主存中的相应内容也应作修改。

-

存储器

+关注

关注

39文章

7768浏览量

172387 -

cpu

+关注

关注

68文章

11362浏览量

226298 -

计算机

+关注

关注

19文章

7848浏览量

93557 -

Cache

+关注

关注

0文章

130浏览量

29820

发布评论请先 登录

机械硬盘的工作原理是什么

Cache的工作原理

高速缓冲存储器Cache的原理、设计及实现

cache结构与工作原理

什么是 Cache? Cache读写原理

深入理解Cache工作原理

Cache工作原理讲解 Cache写入方式原理简介

Cache工作原理是什么

Cache工作原理是什么

评论