高速SerDes的数据和时钟通路上需要很多buffer,传统CML buffer的有限带宽往往限制系统的奈奎斯特频率,采用电阻负载串联无源电感的方式理论上最大可将带宽boost 1.8倍左右,大量无源器件的引入无疑增大了研发成本。本期跟大家聊聊如何通过有源器件实现电感特性,从而实现低功耗、高带宽以及小的芯片面积。

**1 **CML buffer

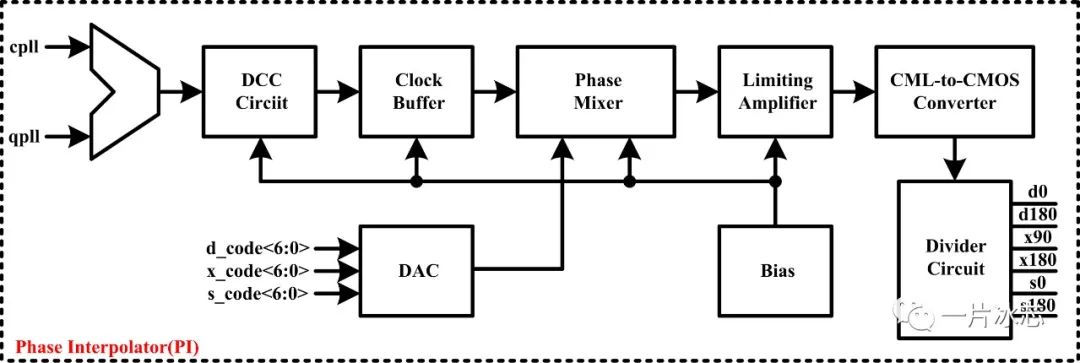

我们先一起回忆一下PI一讲中PI的整体框图 ,如图1所示。图中的DCC Circuit、Clock Buffer、Phase Mixer、Limiting Amplifier电路都是CML 结构或其变形。当时钟频率为5GHz时,图1所示结构,功耗轻易就能达到20mA,随着时钟频率的进一步提升,即使不care功耗,传统CML结构Buffer也很难满足如此高的频率。

将CML Buffer的电阻负载换成有源电感,可在低频处引入零点,从而boost CML Buffer的带宽,实现低功耗、高带宽、小面积。

Fig1. Block diagram of PI

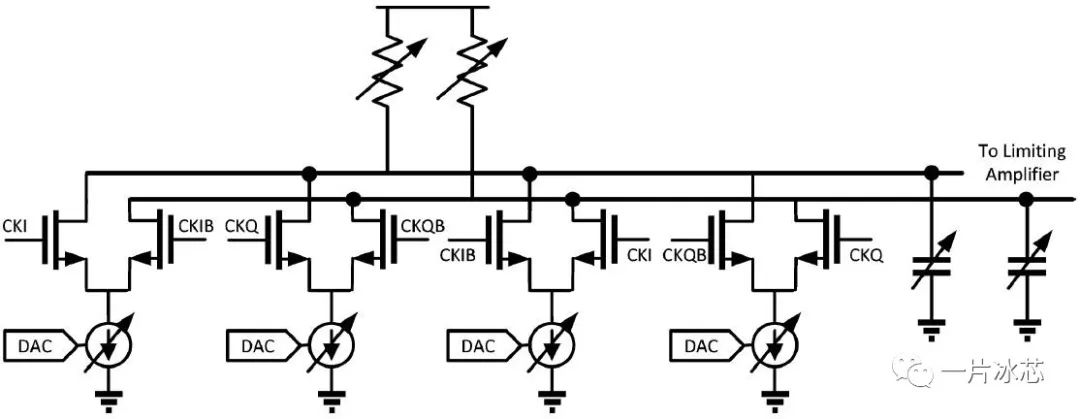

文献[2]给出的phase mixer,同样采用CML结构,如图2所示。通过调整负载电阻、电容及尾电流的大小在20 nm CMOS工艺下实现0.5-16.3 Gbps的宽频率范围内的线性插值。

Fig2. Ref[2]proposed bandwidth adjustable phase mixer

**2 ** (Active)Inductor

2.1 Working principle and application of active inductor

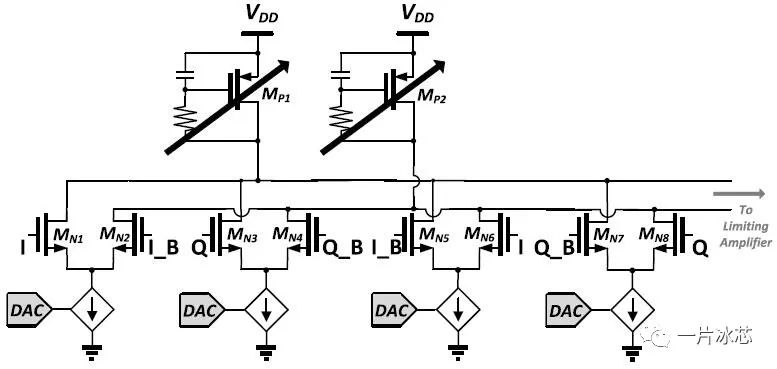

将图2相位差值器的电阻负载换成有源电感负载 即可实现带宽拓展,如图3所示。

Fig3. PI mixer with active inductor load

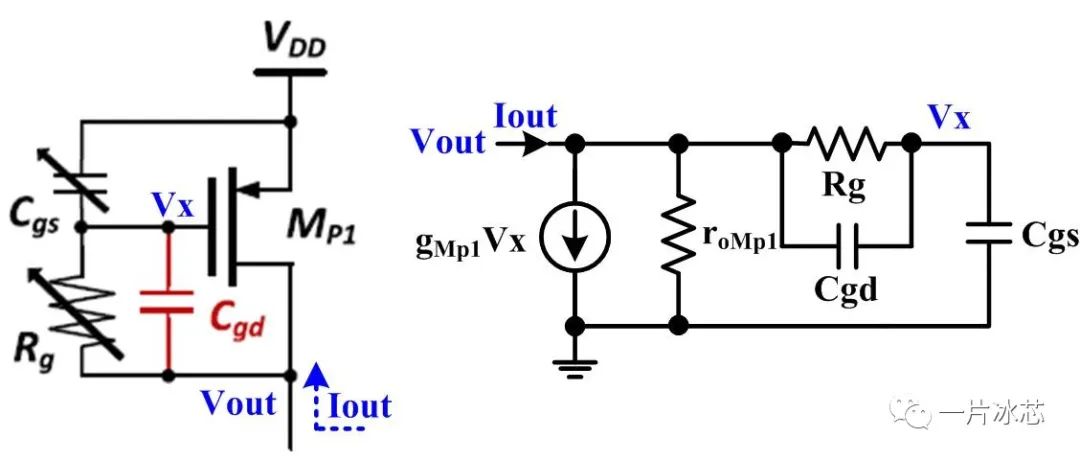

设与图3负载管MP1相连的电阻电容分别为Rg和Cgs,MP1栅漏寄生电容为Cgd,画出有源负载的小信号等效模型,如图4所示。

Fig4. Active inductor load and small-signal equivalent model

列出图4中Vx和Vout节点的KCL方程

KCL@Vx:(Vout-Vx)/[Rg//(1/sCgd)]=sCgsVx,得:Vx=Vout/(1+s[Rg//(1/sCgd)]Cgs)

KCL@Vout:Iout=gMp1Vx+Vout/r oMp1 +(Vout-Vx)/[Rg//(1/sCgd)]

可得,Zout为Zout=Vout/Iout=(1+s[Rg//(1/sCgd)]Cgs)/(s(Cgs+[Rg//(1/sCgd)]Cgs/r ~oMp1~ )+(g ~Mp1~ +1/r ~oMp1~ ))

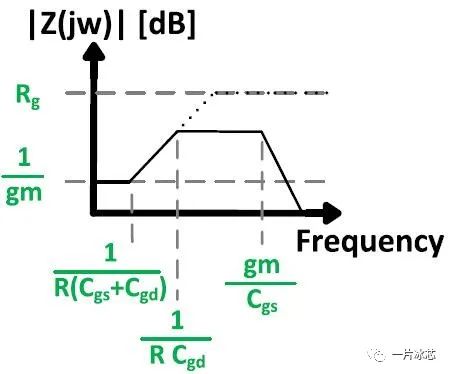

由Zout表达式可得,在1/Rg(Cgs+Cgd)处存在一个左半平面低频零点,Zout的幅频特性曲线,如图5所示,图中的R为Rg,gm为MP1的跨导。合理设置R、Cgs及gm可实现不同频率的补偿。

Fig5. Active inductor small-signal impedance versus frequency

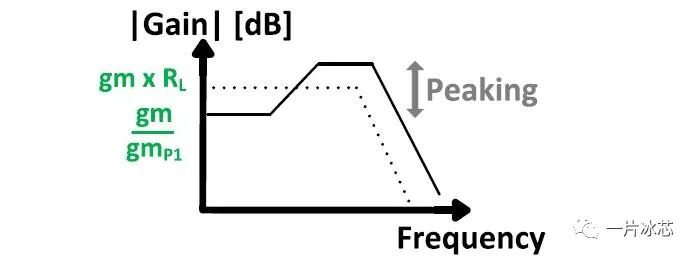

图6给出了传统CML buffer及有源电感负载buffer的幅频特性曲线,可见采用有源电感结构不仅可以boost高频分量及带宽,而且可以衰减低频分量。换句话说有源电感负载结构可以看作一个带通滤波器,抑制了低频噪声、DCD、dc offset,增大了带宽,有利于减小时钟jitter,同时提高INL。

Fig6. CML stage small-signal gain versus frequency for resistive load(dashed line) and active inductor load(solid line)

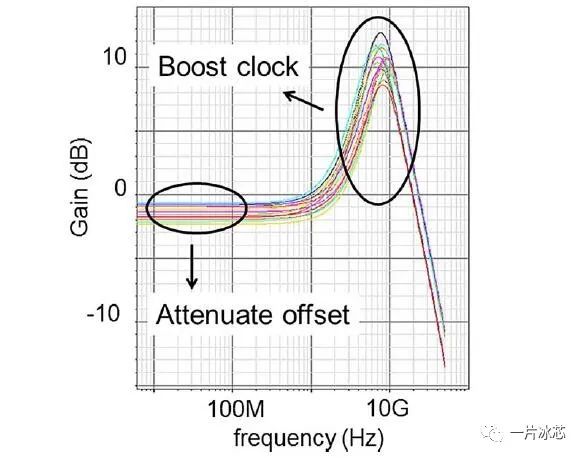

参考文献[4-5]同样采用有源电感负载实现与图6相同的功能,参考文献[4]仿真结果如图7所示。

Fig7. Simulated frequency response of active inductor clock buffer circuit

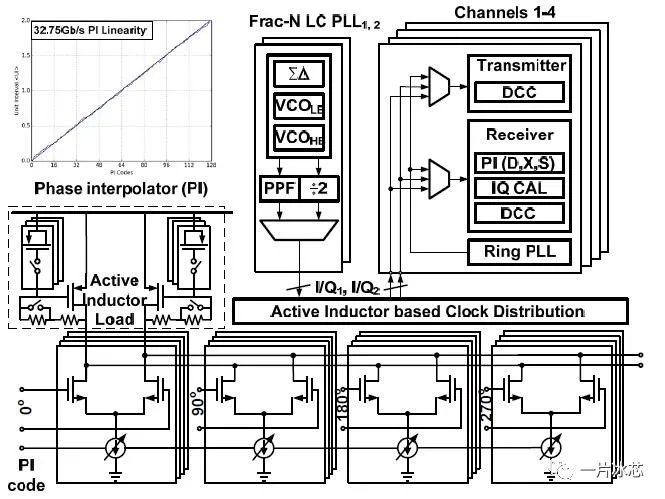

参考文献[5]将有源电感负载结构用在了基于16 nm FinFET CMOS工艺的32.75 Gbps的SerDes中,PI结构如图8所示,左上角给出的PI线性度曲线,可见其具有非常好的线性度。

Fig8. Active inductor based low power linear PI

2.2 applicationof passive inductor

之前跟大家聊过一期无源电感,无源电感除了面积大外,似乎没有什么别的缺点。LCVCO中的电感线圈面积可以轻松到达几百um^2^,LCVCO高Q值的需求,使其无法采用太多层金属堆叠绕制成大感值小面积的电感。

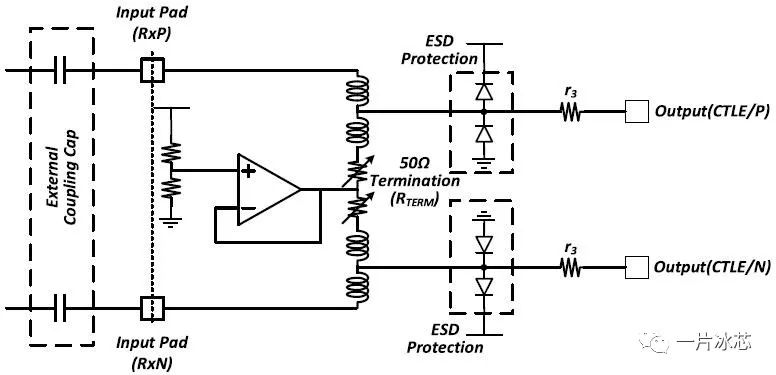

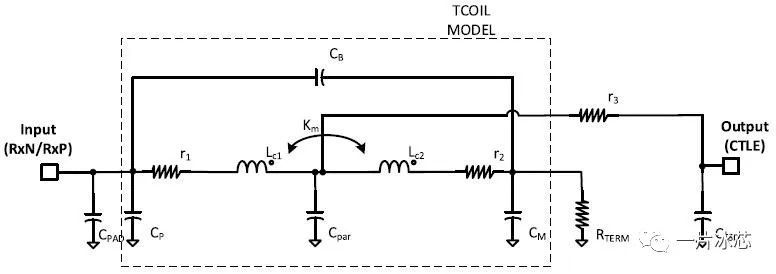

在某些场合,适当引入小尺寸的无源电感,会简化你的设计,如Tx输出和Rx输入。图9给出了Rx输入端的等效电路。

不同于LCVCO,Rx输入端利用电感两端电流不能突变特性来产生零点,进而拓展Rx输入端带宽。图9要满足0.5-16.3 Gbps的数据通信,这里利用电感的交流特性实现宽频率范围内的50Ω阻抗匹配(假设直流电阻已精确校准)

Fig9. Rx input stage

图10给出了Rx输入端半边等效电路,T-coil结构电感将端接电阻和PAD电容分离,利用电感两端电流不能突变的原理,当Rx输入级电流阶跃信号来临时,只给PAD电容充电,初始时刻由于电感对电流的阻塞作用,不会分流到端接电阻,从而实现快速频率响应。

Fig10. Passive input network with T-coil

3 Consideration anddiscussion

Rx输入端T-coil结构电感Layout上如何实现?抽头系数、感值如何确定?图9放大器有什么特别之处吗?采用什么结构?该如何实现?50Ω阻抗匹配又该如何实现?

-

寄生电容

+关注

关注

1文章

293浏览量

19276 -

CMOS工艺

+关注

关注

1文章

58浏览量

15694 -

CML

+关注

关注

0文章

32浏览量

19358 -

有源电感

+关注

关注

0文章

6浏览量

7308 -

SERDES接口

+关注

关注

0文章

28浏览量

3044

发布评论请先 登录

相关推荐

LPC2142的低功耗有源RFID手持机设计

用于定位的低功耗有源RFID标签设计方案

如何通过有源器件实现低功耗及小的芯片面积呢?

如何通过有源器件实现低功耗及小的芯片面积呢?

评论