随着工业界开始大批量生产下一代PoP器件,表面组装和PoP组装的工艺及材料标准必须随之进行改进。

当苹果公司的iPhone在2007年亮相时,随即便被拆开展现在众人面前,层叠封装(PoP)技术又进入了人们的视野。PoP曾经是众人关注的焦点。然而有相当长的一段时间内PoP消失了。目前,更先进的手机将处理器和存储器结合在一起,PoP又成为这类手机的封装选择方案。

平稳的度过几年后,所有主要的手机制造商都已转移到PoP结构来,这是带动他们旗舰产品的引擎。其原因不但关系到尺寸和性能——这是直观可见的,而且也关系到商业因素和供应链,虽然这一点并不明显。PoP的未来十分光明,因为很多新产品都正在采用它,这些产品要求性能不断提高,形状因子继续缩小,以及不同的存储器配置和接口。多样的PoP正处于快速发展阶段,以满足不断增加的需求。PoP这种形式已证明了自身的成熟性,那么除手机之外的其他应用也开始受益于PoP的采用。

应当指出,德州仪器和诺基亚第一个认识到PoP的潜力,并实施大规模的生产。移动电话的印刷电路板(PCB)上总有一些存储器和处理器。在过去,这些器件是单独封装、并排分布的。消费者要求他们的手机中含有最新的、功能丰富的各种应用,这需要越来越多的存储器,因此就迫切要求在相同封装尺寸和形状因子下对存储器件进行叠层。这种方法曾获得巨大的成功。因此,当今每个电话中平均至少含有一个裸片叠层封装,而且这种趋势还是逐渐增加的。

将存储器叠层在逻辑器件上看似比较合理,这可以实现更大规模的小型化、性能和成本效益。然而,看似符合逻辑的想法却并非如此简单。因为逻辑处理器是逻辑加存储配置或叠层中价值较高的器件,逻辑器件制造商在将他们的逻辑器件与存储器件集成时遇到很大困难。他们预计购买晶圆形式的存储器,但这并不是他们自身的产品,因此他们对存储器件的测试良率、交互作用和质量非常关心。此外,存储器测试的专业性非常强,最好留给存储器制造商来完成,并可查看测试结果,以免遇到意想不到的复杂性和高成本。经过前期几次倒霉的尝试,大多数想将逻辑与存储器件集成在同一封装体内的逻辑器件制造商都在焦虑地寻找更好的方法。

PoP解决方案

PoP被认为是更好的方案,可在同一封装体内集成逻辑和存储器件(图1)。PoP的底部可

容纳逻辑器件,这种封装的底面可以处理高引脚数,要求器件采用微小的焊球间距。PoP的顶部可容纳存储器件或器件叠层。由于存储器件一般要求引脚数较低,可以通过周边阵列来处理,即在两个封装体互连的封装边缘处。封装体的底部可以由逻辑器件制造商来制造和测试——每个都会影响他们核心的能力和技术。在一个封装内集成外来的芯片所造成的责任问题可以消除了,因为每个制造商只负责他们自己的封装。终端用户、手持设备制造商可以通过调配来获利,即传统的存储器供应商来供应顶部封装,逻辑器件供应商来提供底部封装。他们的配置也比较灵活,有多个存储器货源和封装类型,可以与多个处理器封装类型和供应商相匹配。

如果逻辑器件和存储器件都被集成到同一个叠层封装中,那么手机制造商则无需再列出特定的器件组合方案。通过JEDEC的电学(取决于内部存储器的配置)和机械标准,可以灵活地实现顶部存储器件封装与底部逻辑器件封装的组合。底部封装也遵守JEDEC的机械标准。这样的标准化允许制造商设计并生产能够彼此兼容的产品,这也是为什么PoP终于成熟,并且在过去几年内投放市场进行大量生产的一个基本原因。

今天,将PoP投入量产并不轻松,如同所有新型封装技术一样,还有很多障碍需要克服。为实现灵活的PoP结构,封装叠层需要在PCB上同时塑模并再回流。此前并不容易实现,需要手机制造商或者其电子制造服务提供商(基板组装)进行开发和优化。两个球栅阵列(BGA)封装不但可以在相互的顶部进行再回流,而且再回流两个非常薄的、相对大些、窄间距的BGA在某种程度上也是新的挑战。由于两种封装的间距都相对较窄(一般为0.65 mm的间距或者小于封装体到封装体之间的互连),再回流过程中每个封装体能够承受的翘曲量是非常有限的。以前,再回流过程中封装翘曲并不是影响表面贴装良率的主要考虑因素。

现在已经可以度量并控制封装翘曲。使问题进一步复杂的原因是该结构很难控制底部PoP的翘曲。底部PoP的外围缺乏模塑密封材料,可以互连到顶部封装。因此,外围由一个无支持的封装基板组成。为了降低整个叠层PoP的高度,基板又被尽可能地做薄。因为基板会由于再回流的温度而膨胀(所有PoP都在稍高的再回流温度下采用无铅焊球,而非共晶锡铅焊球),这样的配置会内在的导致翘曲。封装尺寸、器件尺寸、基板厚度和成分、模塑密封材料、裸片粘接厚度和材料全都在决定底部PoP翘曲中发挥重要作用。同样地,必须对它们进行优化才可能生产出满足表面组装良率要求的底部PoP。一般而言,如果PoP叠层无法再回流到PCB上,就无法选择重做,因此对于基板组装时初次通过的良率要求是非常高的。

控制顶部封装的翘曲也是一项挑战。顶部PoP内部可叠层2至5片裸片。这些器件的尺寸各式各样:一些器件尺寸相同或相近,需要在叠层裸片之间采用间隔夹层,这样才能使引线键合到基板上。虽然再回流时观察封装的顶部会发现一般底部PoP的外形有些凹陷,然而顶部PoP的外形也会凹陷或凸起。尽管顶部PoP将模塑密封材料扩展到封装边缘,通常产生的翘曲小于底部PoP,顶部PoP的翘曲必须经常容忍底部封装的翘曲或者保持绷紧状态以允许底部封装中更高的翘曲。封装材料和厚度的优化对于顶部PoP实现合格的表面组装良率是非常重要的。再回流过程中以顶部和底部封装为目标的翘曲最初大约80μm。然而,随着大量的调查,对于0.65 mm的封装到封装互连间距,一些顾客已经将翘曲目标降低到60μm。

当前PoP的趋势和进步

当前的趋势是朝向更小化和更高密度的PoP发展,封装到封装的互连间距有0.5mm,这类封装要求再回流时翘曲低至50μm,这类封装也将会使底部PoP的底部上的焊球间距转移到0.4mm,由于高引脚数和受限的封装面积(目标一般是12×12 mm或更小的封装尺寸),需要在室温下满足共面规范,再回流时满足在焊料熔点温度以上的苛刻的翘曲规范。在表面组装一侧,为使微细球间距的PoP组装和再回流同时发生,正在引入改进的表面组装工艺。当今典型的表面组装工艺包括在PCB上印刷焊膏、放置底部PoP、在熔剂内电镀顶部PoP焊球、在底部PoP上放置顶部PoP、在清洁干燥的空气中通过熔炉再回流将其熔化。引入的新型工艺包含了在焊剂或焊料糊中熔化顶部封装焊球,可以提高再回流过程中顶部到底部的封装互连的鲁棒性。

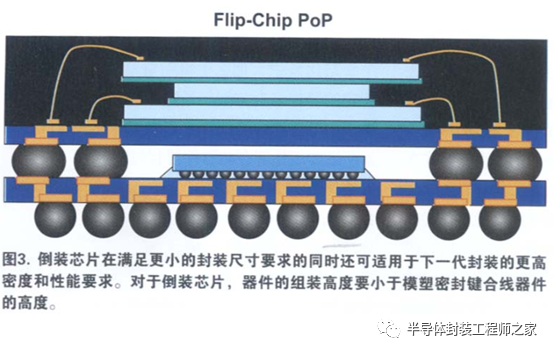

改进表面组装和PoP组装的工艺和材料是必要的,因为工业开始进行下一代PoP器件的大量生产。当今,生产的大多数底部封装可以调节键合线的互连。然而,倒装芯片仍然在满足12×12mm或更小尺寸要求的同时,一般还可适用于下一代封装的更高密度和性能要求(图3)。因此,大部分在印刷版上的底部PoP逻辑器件都是倒装芯片器件。倒装芯片的另一个优势是器件的组装高度小于模塑密封键合线器件的高度。倒装芯片器件无需进行模塑密封,这就降低了加工成本。然而,不采用模塑密封材料,不需要底部填充倒装芯片器件,这会为控制封装的翘曲带来很大的挑战。

控制封装翘曲

为控制封装翘曲,稍厚的基板和新型封装材料需要进行检测。为满足最大为0.22mm(JEDEC机械规范)的组装高度,可以减薄倒装芯片,可允许在顶部组装0.5mm间距的顶部PoP。其他底部PoP的变化也正在进行开发,可有助于控制封装翘曲,允许采用更厚的裸片。目前开发的底部封装中,中心处采用模塑密封化合物的倒装芯片,或者将模塑化合物扩展到封装边缘处。这些封装一般在顶部四周处(焊盘上的焊料或其他方案)有内建的互连通孔,有助于与顶部PoP“桥接缝隙”。这种“桥接”方案也正在被含有两个裸片叠层的底部封装所采用。某些先进的下一代PoP要求逻辑器件和逻辑器件或者逻辑器件和模拟器件叠层在一起。这类叠层中的底部裸片是倒装芯片或者是键合线,但顶部裸片总是采用引线键合。因此,必须要求模塑封装,除非顶部PoP采用0.65 mm的焊球间距,“桥接”方案是必须的。

降低高度

当今,降低叠层高度是PoP所面临的最困难的挑战之一。目前,PoP一般是手机中的数字部分或PCB侧面最厚的封装。虽然其它的封装,包括裸片叠层封装,其封装高度最大为1.2mm,或者更低,而PoP叠层正努力满足最大高度为1.4mm。早期PoP叠层的最大高度在1.8mm附近,现在PoP叠层最大高度范围在1.6mm内。降低叠层高度的难度在于减少器件组装的高度,或者底部封装之间密封模塑所要求的间隙。如前面讨论所说,降低厚度可产生更高的翘曲。可以降低顶部PoP,但是在大量生产中顶部PoP都采用最薄的基板和裸片厚度(基板厚度0.13 mm,裸片厚度60至75μm)。进一步降低要求更加薄的基板、裸片粘接材料(裸片粘接薄膜),需要裸片厚度60μm以下。这些材料的供应成本通常是额外的费用,生产中这些更薄材料和器件的处理都是有疑问的。

在 过 去 几 年内,新型PoP解 决 方 案 已被 引 进 , 在满 足 最 高 高度1.4 mm的要求同时,可在顶部PoP内叠层两个存储器件。将来,这类PoP叠层将采用非常薄的存储裸片和更加先进的超薄封装材料,能够满足最高高度为1.2 mm。

PoP的未来

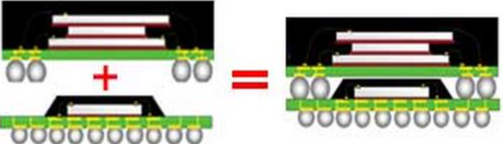

新型PoP及其变化正在冉冉升起,可以解决目前传统PoP的一些弱点。例如,随着封装变得越来越薄,焊球间距越来越小,一种控制PoP翘曲挑战的解决方式是在组装到PCB上之前将顶部和底部封装组装到一起。虽然这削弱了PoP在灵活性上的优点,但是在基板组装前进行“预叠层”是一项相对简单的工艺,再回流过程中比较容易控制——再回流中PCB自身的翘曲。对预叠层PoP进行测试,可确保它是良好的,并且能够展现出比单独的顶部或底部PoP更低的翘曲,因此制造PoP类似于在PCB上组装一个更加传统的窄间距BGA。预叠层PoP非常吸引那些现在能为终端客户提供低端逻辑器件和顶部存储器件的器件制造商。这种选择吸引的不是那些经营移动手持设备的终端客户,而是期待为自己的产品采用PoP的客户。

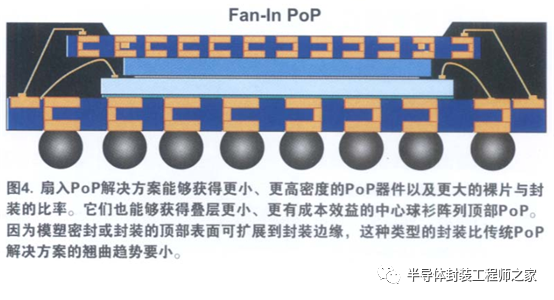

随着底部PoP的处理器性能和容量持续增高,裸片的面积越来越大,即使晶圆工艺尺寸从90 nm缩减到65 nm甚至以下,这些都造成很难在12×12mm或更小的封装体内安置器件,而这正是目前所需要的。扇入PoP解决方案(底部PoP的顶部表面上的焊盘不在四周,而在中心)已经开始研发,为获得更小、更高密度的PoP器件以及更大的裸片与封装比率(图4)。扇入PoP也能够达到一个更小的、更大成本效益的中间BGA顶部PoP。因为模塑密封或者封装顶部的表面可扩展到封装边缘,已经证明,这类封装比传统PoP解决方案的翘曲更小。扇入PoP的另一优点是在顶部叠层封装上能够容纳更高数目的互连。这无需增大封装体即可获得,因为顶部中心互连阵列间距为0.5 mm,甚至0.4 mm。这允许处理器到处理器封装叠层或者处理器到高引脚数的存储器接口,这是手机制造商的关键技术。在某种意义上讲,类似扇入PoP的PoP变化正在担负基板内嵌入元件的任务,而扇出晶圆级封装方法则将目标致力于填补未来。

结论

作为一种封装形式,PoP早已出现,但将在数年内成为在手机中处理器与存储器组合的主流封装形式。许多新产品将采用PoP形式发布,引入PoP中新的变化可以满足更小尺寸、更低高度、更高性能、更加精细焊球间距和引脚数目等方面的要求。新材料的引入及改进将有效的缓解封装的翘曲问题,并且新型表面贴装技术也有助于达到满足要求的板级组装良率。PoP正在从手机应用扩展到其他的手持设备和存储应用中,并且这种趋势将有可能继续下去。因此,PoP仍将继续位居3D封装创新的最前沿。

审核编辑:刘清

-

处理器

+关注

关注

68文章

19293浏览量

229918 -

pcb

+关注

关注

4319文章

23105浏览量

398063 -

存储器

+关注

关注

38文章

7493浏览量

163871 -

逻辑器件

+关注

关注

0文章

88浏览量

20103 -

POP封装

+关注

关注

0文章

5浏览量

5012

原文标题:多样化PoP封装浮出水面

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2.5D/3D封装技术升级,拉高AI芯片性能天花板

苹果新语音通信专利浮出水面

长电科技为自动驾驶芯片客户提供多样化高可靠性的封装测试解决方案

层叠封装PoP_锡膏移印工艺应用

3D封装多样化PoP封装浮出水面

3D封装多样化PoP封装浮出水面

评论