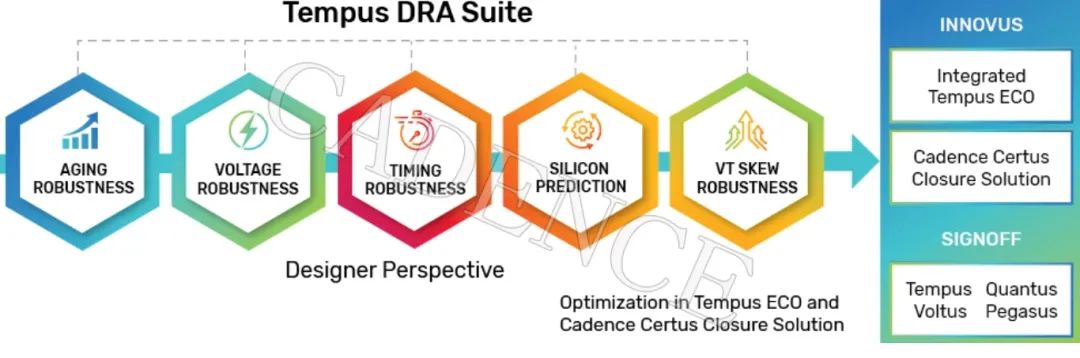

实现签核时,为了保证芯片设计的耐用性,设计师会面临重重挑战,利用 Cadence Tempus 设计稳健性分析(DRA)套件为设计工程师提供领先的建模技术,可实现最佳功耗、性能和面积目标(PPA)。

相较于传统方法,Tempus DRA 套件提供了一套全面的高级分析功能,有望增强设计级稳健性,实现更优 PPA。

使用 Tempus DRA 套件完成完整分析后,设计工程师可以利用 Cadence Innovus 设计实现系统中的 Tempus ECO 选项进行模块级的收敛,并使用 Cadence Certus 收敛解决方案进行子系统/全芯片层的签核收敛,显著提高设计收敛速度,优化 PPA 目标达成。

如需了解更多信息,请点击文末“阅读原文”。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

-

Cadence

+关注

关注

65文章

935浏览量

142867

原文标题:Tempus DRA 套件:使用先进的芯片建模实现高达 10% 的 PPA 提升

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为DRA71x、DRA79x和TDA2E-17供电的LP8733-Q1和LP8732-Q1用户指南

Advantest CEO:先进芯片测试需求大增

TPS659039-Q1为DRA74x、DRA75x、TDA2x和AM572x供电的用户指南

10 MHz高速数据转换器系统评估套件(HSDC-SEK-10)

DRA74x、DRA75x和DA2x系列设备的服务质量(QoS)旋钮

知识分享 | 轻松实现优质建模

AI网络物理层底座: 大算力芯片先进封装技术

DRA75x、DRA74x信息娱乐应用处理器器件版本2.0数据表

DRA75xP、DRA74xP信息娱乐应用处理器芯片版本1.0数据表

DRA77xP、DRA76xP信息娱乐应用处理器芯片版本1.0数据表

Tempus DRA 套件:使用先进的芯片建模实现高达 10% 的 PPA 提升

Tempus DRA 套件:使用先进的芯片建模实现高达 10% 的 PPA 提升

评论