作者:Suhel Dhanani

AMD 自适应 SoC 与 FPGA 事业部软件市场营销总监

由于市场环境日益复杂、产品竞争日趋激烈,为了加快推出新型自适应 SoC 和 FPGA 设计,硬件设计人员和系统架构师需要探索更为高效的全新工作方式。AMD Vivado设计套件可提供易于使用的开发环境和强大的工具,有助于加速大型自适应 SoC 和FPGA等系列产品的设计与上市。

现在,我很高兴为大家详细介绍 AMD 最新发布的 Vivado 设计套件2023.2 ,以及它的更多优势——将帮助设计人员快速实现目标 Fmax,在实现之前精确估算功耗需求,并轻松满足设计规范。

使用新的布局和布线特性

快速实现目标 Fmax

基于 Vivado 设计套件的智能设计运行 ( IDR )、报告 QoR 评估 ( RQA )和报告 QoR 建议 ( RQS )等差异化功能,2023.2 版本提供的新特性可帮助设计人员和架构师快速实现 Fmax 目标。

举例来说,Versal SSIT器件中的超级逻辑区域( SLR )交叉布局和布线目前已通过新算法实现自动化,从而将最大限度地提高性能。我们针对AMD Versal 设计添加了多线程器件镜像生成支持,有助于加速比特流生成。

上述改进旨在帮助设计人员快速实现其性能目标。

使用更新的 Power Design Manager 工具

改进功耗估算

需要特别指出的是,我们在 2023.2 版本中扩展了 Power Design Manager( PDM )工具的可用性,从仅支持 Versal 器件扩展到同时支持大多数 UltraScale+ 器件,使设计人员在专注于设计实现方案之前,能够比以往任何时候都要更轻松地精确估算功耗。

PDM 可提供易于使用的界面和增强的向导,支持针对最新 AMD 自适应 SoC 和 FPGA 中的硬 IP 块进行功耗估算。它使用最新的特性描述模型确保功耗估算准确性,并帮助平台为未来的热能及供电做好准备。

此外,CSV文件也可导入和导出,而 PDM 数据则能轻松转换为可读取的文本报告。

上述变化支持 Xilinx Power Estimator( XPE )能够无缝直观地过渡到 PDM。

使用新增功能轻松创建和调试设计

与此同时,我们还添加了其它特性,使复杂设计的创建、仿真和调试工作变得轻松易行。IP 集成器中面向 Versal 器件的新的地址路径可视化、增强的 DFX 平面图可视化,以及在相同设计中新增了对 Tandem 配置和 DFX 的支持,所有这些新特性都将为简化设计过程提供助力。

其它关键更新包括:扩展了对 SystemC 测试台的 VCD 支持,以协助调试功能;此外还添加了 STAPL 支持,以在编程环境中针对 UltraScale+ 和 Versal 设计验证 JTAG链。利用最新版解决方案,设计人员能够更轻松地设计 UltraScale+ 和 Versal 器件。

使用 Vivado设计套件

高效实现自适应 SoC 和 FPGA 设计

我们相信,Vivado 设计套件2023.2 所包含的更新将帮助硬件设计人员和系统架构师更轻松快速地跟进不断变化的市场需求,同时还能将高性能与快速产品上市进程兼而得之。作为您的合作伙伴,我们始终致力于不断改进优化设计工具,帮助您充分发挥 AMD 自适应 SoC 和 FPGA 产品解决方案的强大功能。

NEW

欢迎进一步了解

2023.2 版本的新功能或立即下载

快速启动工作

原文标题:Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

文章出处:【微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

-

赛灵思

+关注

关注

33文章

1798浏览量

133719 -

Xilinx

+关注

关注

73文章

2208浏览量

132086

原文标题:Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

文章出处:【微信号:赛灵思,微信公众号:Xilinx赛灵思官微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

Altera正式推出FPGA AI套件26.1.1版本

Altera发布FPGA AI套件

AMD Versal自适应SoC中eMMC烧录/启动调试检查表(上)

使用Aurora 6466b协议实现AMD UltraScale+ FPGA与AMD Versal自适应SoC的对接

AMD Vivado Design Suite 2025.2版本现已发布

vcs和vivado联合仿真

AMD Versal自适应SoC内置自校准的工作原理

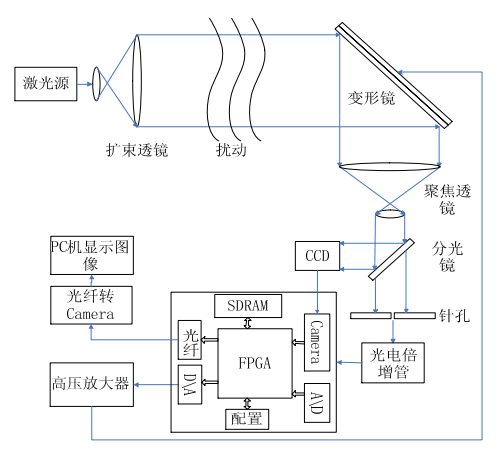

高压放大器驱动:基于FPGA的SPGD自适应光学控制平台的探索

AMD Vivado设计套件2025.1版本的功能特性

在AMD Versal自适应SoC上使用QEMU+协同仿真示例

基于FPGA LMS算法的自适应滤波器设计

Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

Vivado™ 设计套件 2023.2 版本:加速自适应 SoC 和 FPGA 产品设计

评论