CMRR定义及其测试

在开始讨论运放的共模抑制比CMRR之前,我们先了解一下运放的共模输入电压和轨对轨运放。运放的共模输入电压是指运放的两个输入引脚电压的平均值;

对于双极性输入级的运放,运放的共模输入电压,一般达不到电源电压。而轨对轨(rail to rail)运放的共模电压几乎可以达到电源电压。

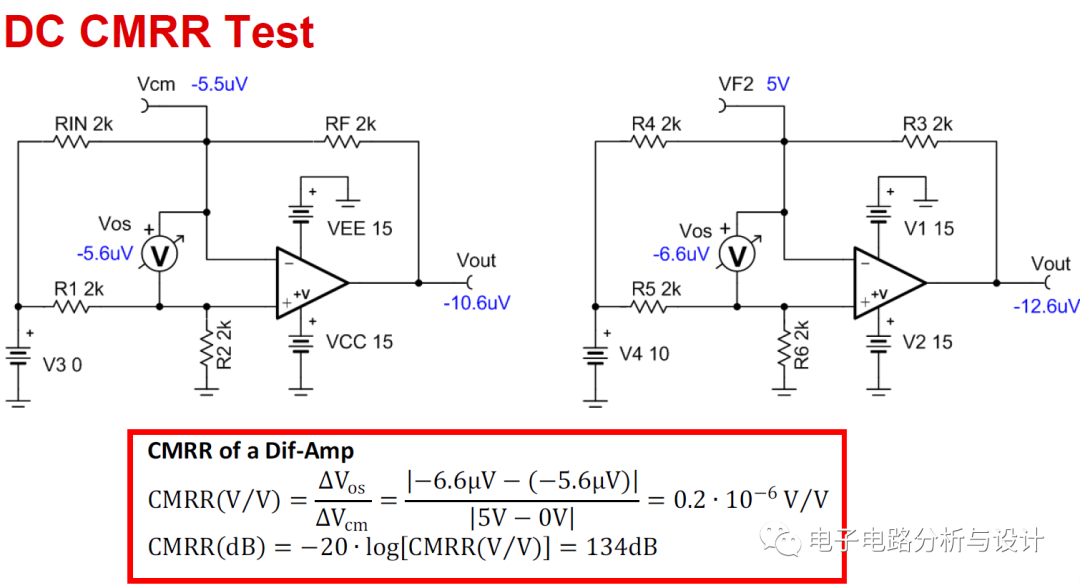

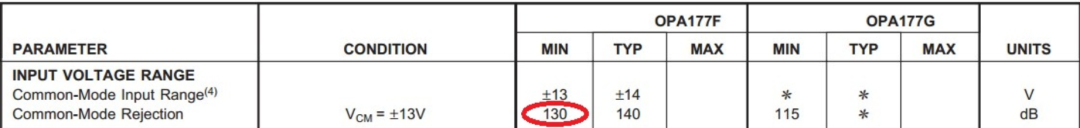

CMRR定义为差模电压增益AD和共模电压增益AC的比值,即:CMRR=AD/AC.但是为了更加便于理解,即从应用的角度出发,CMRR也可以看作输入失调电压Vos随共模输入电压Vcm变化的情况,即CMRR(V/V) = ΔVos/ΔVcm.或者写成对数的形式CMRR(dB) = -20*log[CMRR(V/V)]。

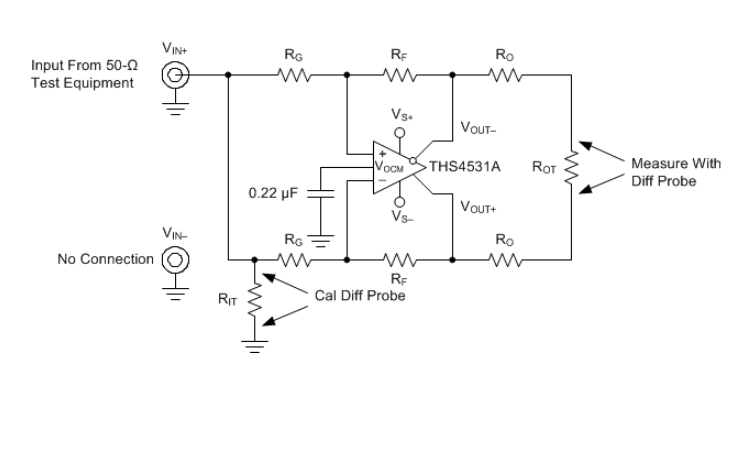

关于CMRR的测试可以基于CMRR(V/V) = ΔVos/ΔVcm此表达式。如下图所示:

影响CMRR的因素

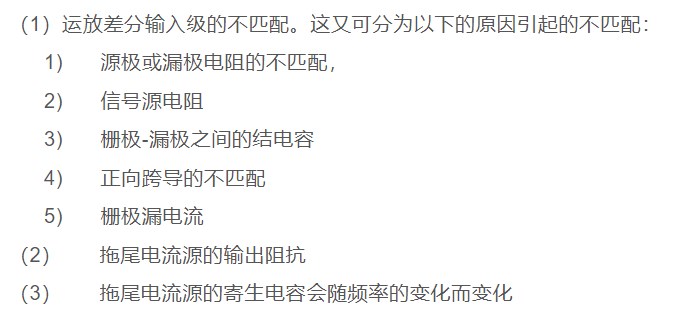

运放之所以会对共模信号能够进行放大,即CMRR(dB)不为无穷大,主要来源于下面几个原因:

下面我们就挑几个上面的原因看一下它们的影响(参考自TI中文论文):

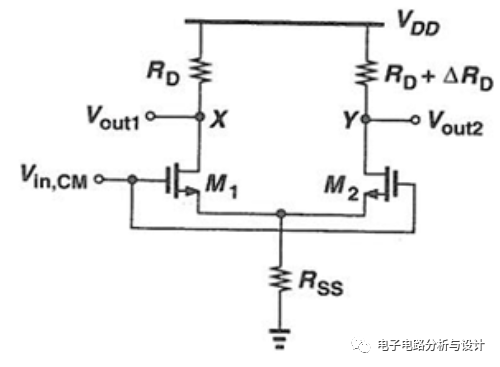

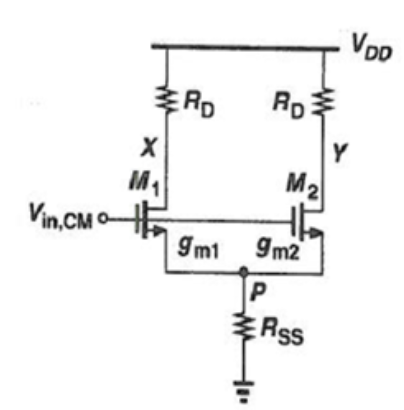

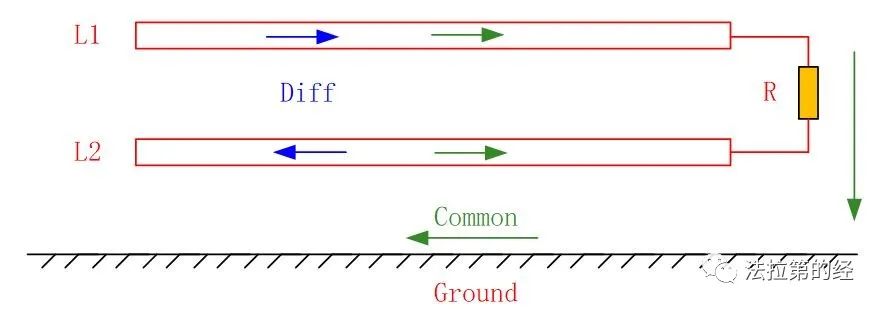

(1) 电阻的不匹配,如下图所示,由于电阻的不匹配,一个共模电压的变化ΔVin,会在X,Y点转化为一个差模电压。

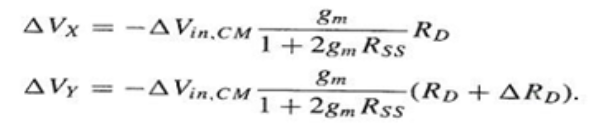

计算如下,这个由失配阻ΔRd引入的差模信号,就会转化为差分级输出信号的噪声。

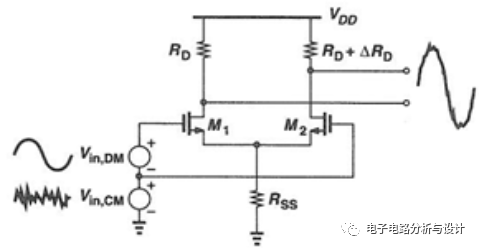

(2) 输入晶体管的不匹配,管子的不匹配,会引起两管子的电流的微小差别,并且两个的跨导是不一样的。

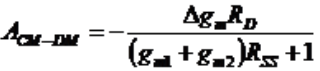

由于输入级管子的不匹配,会将共模信号转化为一个差模的误差,可以用下面的公式表示,它表示失配跨导引起的CMRR。

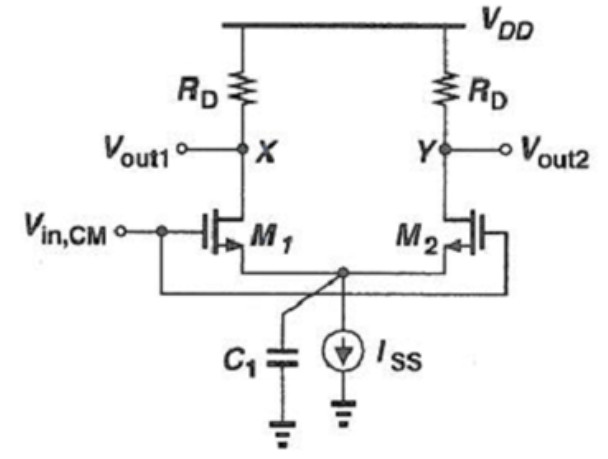

(3) 再介绍一个原因,就是拖尾恒流源的寄生电容会随频率变化而变化。这会引起这个恒流源电流的变化,差分输入端射极或源极电阻用恒流源代替的目的是保持电流恒定和高阻抗。但它的电流如果随频率发生变化,势必降低差分输入端的共模抑制能力。

-

电源电压

+关注

关注

2文章

991浏览量

24065 -

共模抑制比

+关注

关注

3文章

81浏览量

15970 -

寄生电容

+关注

关注

1文章

294浏览量

19313 -

CMRR

+关注

关注

0文章

84浏览量

14838 -

失调电压

+关注

关注

0文章

123浏览量

13929

发布评论请先 登录

相关推荐

关于仪表运放共模抑制比的问题

共模抑制比CMRR与电源抑制比PSRR相关介绍

求助,关于仪表运放共模抑制比的问题

共模抑制比,共模抑制比是什么意思

网络变压器共模抑制比CMRR概念及原理

共模抑制比CMRR是什么CMRR的技术及计算公式详细说明

共模抑制比CMRR与电源抑制比PSRR的仿真原理

什么是共模抑制比CMRR?什么是电源抑制比PSRR?

适合过程控制应用的完整高速、高共模抑制比(CMRR)精密模拟前端

共模抑制比CMRR定义及其测试

共模抑制比CMRR定义及其测试

评论