其他端接方式:

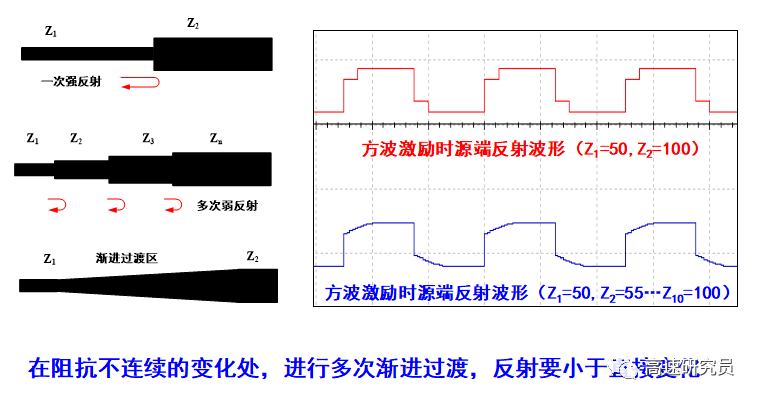

3.过渡匹配

优点:成本低,功耗低。在高速高频信号中应用广泛。

缺点:反射依然存在,只是优化。

4.使用Power Divider / Splitter

仿真验证结果表明,端接技术可以有效抑制传输线上的反射噪声,改善高速电路的性能。任何一种端接匹配都要和拓扑相联系,根据信号质量的要求并综合考虑端接技术对信号的影响,才能得到最佳的端接匹配效果。篇幅限制,后续再介绍常用的一些端接和匹配实例。

5.多负载端接技术

在实际电路中常常会遇到单一驱动源驱动多个负载的情况,这时需要根据负载情况及电路的布线拓扑结构来确定端接方式和使用端接的数量。一般情况下可以考虑以下两种方案。

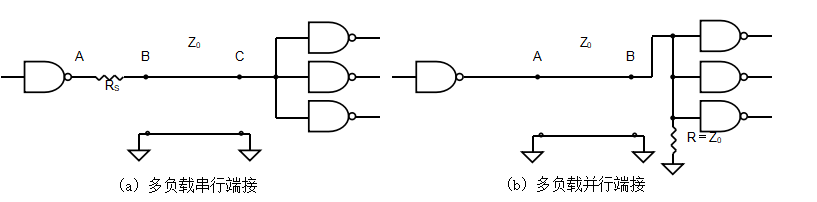

多负载串行方式下的端接策略

如果多个负载之间的距离较近,可通过一条传输线与驱动端连接,负载都位于这条传输线的终端,这时只需要一个端接电路。如采用串行端接,则在传输线源端加入一串行电阻即可,上图a所示。

如采用并行端接(以简单并行端接为例),则端接应置于离源端距离最远的负载处,同时,线网的拓扑结构应优先采用菊花链的连接方式,如上图b所示。

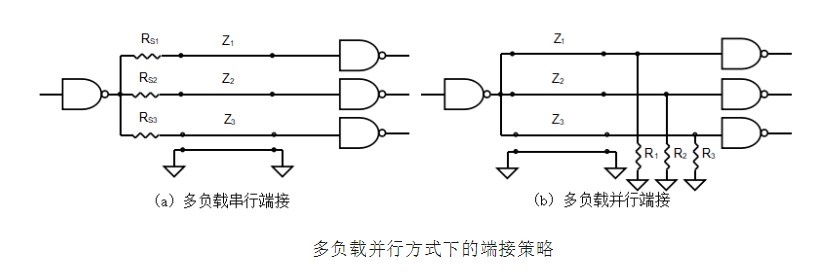

如果多个负载之间的距离较远,需要通过多条传输线与驱动端连接,这时每个负载都需要一个端接电路。

如采用串行端接,则在传输线源端每条传输线上均加入一串行电阻,如下图a所示。如采用并行端接(以简单并行端接为例),则应在每一负载处都进行端接,如下图b所示。

在采用匹配的时候,但要确保匹配元件尽量靠近源端或负载端,这样可以减少电感,使匹配更为有效。

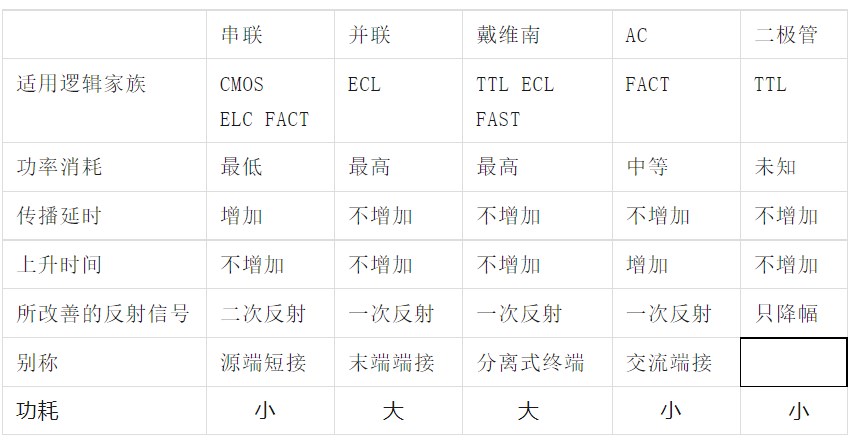

6.端接技术比较

7.不同工艺器件的端接策略

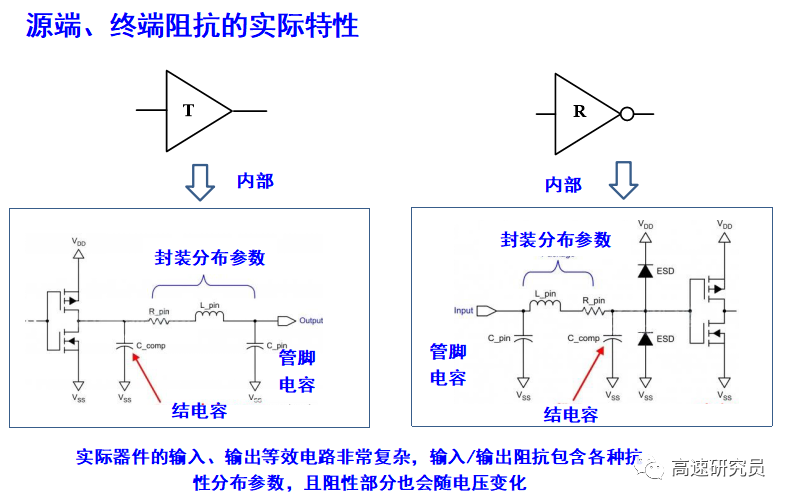

阻抗匹配与端接技术方案随着互联长度和电路中逻辑器件的家族在不同也会有所不同,只有针对具体情况,使用正确适当的端接方法才能有效地减小信号反射。

一般来说,对于一个CMOS工艺的驱动源,其输出阻抗值较稳定且接近传输线的阻抗值,因此对于CMOS器件使用串行端接技术就会获得较好的效果。而TTL工艺的驱动源在输出逻辑高电平和低电平时其输出阻抗有所不同,这时,使用并行戴维宁端接方案则是一种较好的策略。

ECL器件一般都具有很低的输出阻抗,因此,在ECL电路的接收端使用一下拉端接电阻(下拉电平需要根据实际情况选取)来吸收能量则是ECL电路的通用端接技术。

当然,上述方法也不是绝对的,具体电路上的差别、网络拓扑结构的选取、接收端的负载数等都是可以影响端接策略的因素,因此在高速电路中实施电路的端接方案时,需要根据具体情况通过分析仿真来选取合适的端接方案以获得最佳的端接效果。

-

阻抗匹配

+关注

关注

14文章

352浏览量

30798 -

TTL电路

+关注

关注

2文章

65浏览量

15072 -

传输线

+关注

关注

0文章

376浏览量

24029 -

CMOS工艺

+关注

关注

1文章

58浏览量

15672 -

ECL

+关注

关注

0文章

38浏览量

13425

发布评论请先 登录

相关推荐

传输线在阻抗匹配时串联端接电阻为什么要靠近发送端

浅析阻抗匹配及其应用

传输线阻抗匹配

从阻抗匹配的角度来解析射频微波传输线的设计技术

微带传输线阻抗匹配应用经验

ps脉冲传输线的多容性负载阻抗匹配模型和计算

解析通信网路的阻抗匹配与射频传输线的设计技术

微带传输线阻抗匹配电路设计

浅谈阻抗匹配(七)传输线的端接技术

浅谈阻抗匹配(七)传输线的端接技术

评论