11 月 2 日-3 日,2023 国际集成电路展览会暨研讨会(IIC Shenzhen)在深圳成功举行。会上,集成电路产业大咖聚集,共同洞见集成电路产业趋势的风向标。

在中国 2023 全球 CEO 峰会上,Cadence 副总裁兼亚太区技术运营总经理陈敏发表了题为《泛 AI 加速——新时代的 EDA 进化》的精彩演讲,向与会者介绍了 AI 技术的发展现状和未来趋势,并分享了 Cadence AI 解决方案的特点和优势。

在随后的 EDA/IP 与 IC 设计论坛上,Cadence 技术支持总监李志勇也做了题为《适用大模型 Al 芯片的接口 IP》的精彩演讲。

陈敏

泛 AI 加速——新时代的 EDA 进化

在 IIC Shenzhen 的全球 CEO 峰会上,陈敏分享了 AI 技术发展所必不可少的高算力、高带宽、低功耗半导体设计对 EDA 性能、效率的挑战,以及受益于 AI 技术的 EDA 在处理大数据量科学计算方面的机会,介绍了 Cadence 引领潮流的全栈 AI EDA 解决方案。

AI 技术的颠覆时刻已经到来

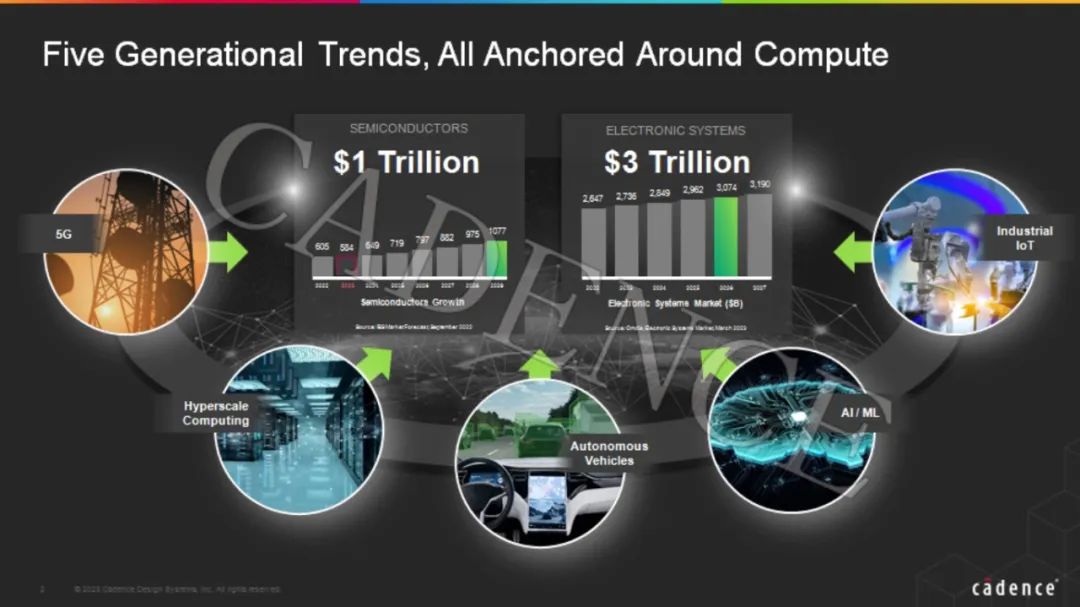

无处不在的 AI 正成为当今世界最引人注目的话题之一。人工智能(AI)的广泛应用正在改变各个行业的运作方式。EDA 行业也不例外,AI 的发展离不开高算力、高带宽、低功耗的芯片,而此类芯片的设计对 EDA 的性能和效率也提出了更高的挑战。反过来 EDA 作为处理大数据量的计算软件,也天然受益于 AI 技术。 陈敏表示,从 5G 到云计算,再到物联网的所有驱动力正在共同推动半导体行业的增长。预计在未来的 3 到 5 年,半导体市场规模将突破万亿美元,电子系统将达到 3 万亿美元。尽管短期的经济下行和地缘政治动荡正在影响 2023 年的短期收入,但设计活动依然强劲,前景依然积极。

消费者希望芯片具有更多的功能、更多的计算能力和更快的数据传输速度。这就使芯片复杂度越来越高,同时要设计的芯片种类也越来越多,这必将造成设计人员大量短缺。根据半导体行业协会数据,2030 年设计工程师缺口将达到 35%。要解决人才短缺的挑战,一方面当然是人才培养,另一方面则是提高生产力。

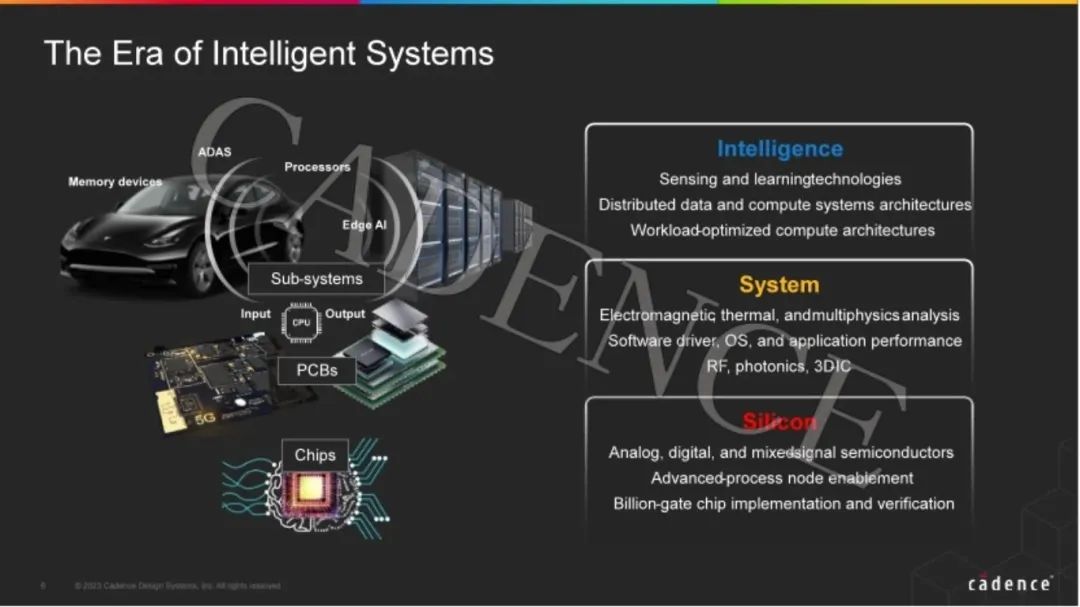

现在,全球每年制造数十亿台智能设备,预计到 2025 年,其潜在市场规模将达到 700 亿美元左右。根据半导体行业协会的数据,现代汽车可能拥有 8000 个或更多的半导体芯片和 100 多个电子控制单元,目前占车辆总成本的 35% 以上,预计 2025 年至 2030 年将超过 50%。

而设计这样的智能系统对 EDA 提出了巨大的挑战,只有不断提高生产力才能满足设计需求。EDA 通过提升抽象层次,从晶体管级到单元级,再到 IP 的设计复用,以及现在基于 AI 的 EDA 或基于 AI 的自动化来提高生产力,同时有助于延续摩尔定律。

消费者希望芯片具有更多的功能、更多的计算能力和更快的数据传输速度。这就使芯片复杂度越来越高,同时要设计的芯片种类也越来越多,这必将造成设计人员大量短缺。根据半导体行业协会数据,2030 年设计工程师缺口将达到 35%。要解决人才短缺的挑战,一方面当然是人才培养,另一方面则是提高生产力。

现在,全球每年制造数十亿台智能设备,预计到 2025 年,其潜在市场规模将达到 700 亿美元左右。根据半导体行业协会的数据,现代汽车可能拥有 8000 个或更多的半导体芯片和 100 多个电子控制单元,目前占车辆总成本的 35% 以上,预计 2025 年至 2030 年将超过 50%。

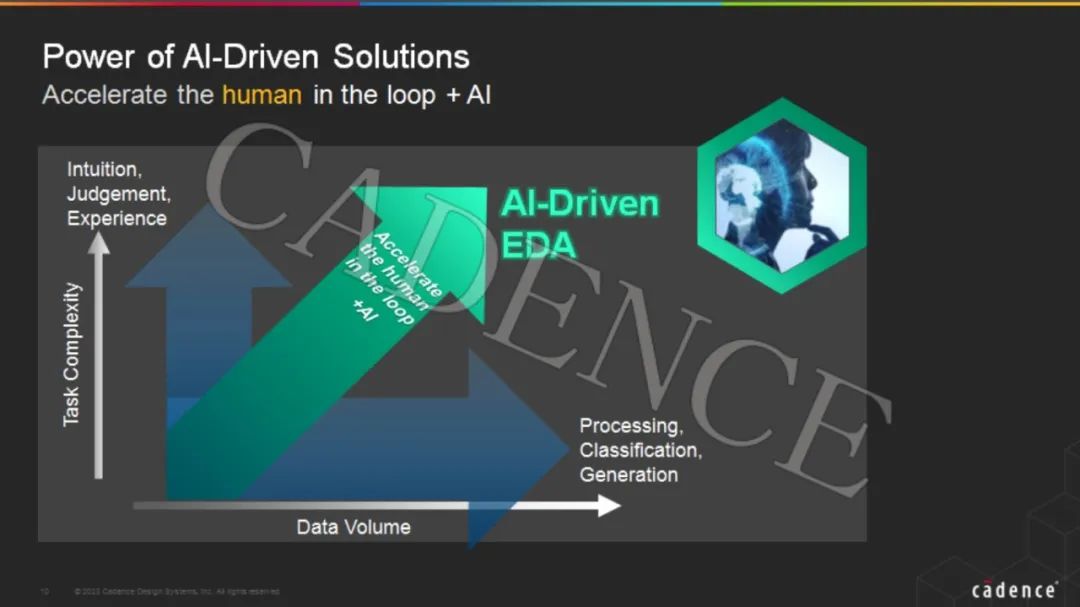

而设计这样的智能系统对 EDA 提出了巨大的挑战,只有不断提高生产力才能满足设计需求。EDA 通过提升抽象层次,从晶体管级到单元级,再到 IP 的设计复用,以及现在基于 AI 的 EDA 或基于 AI 的自动化来提高生产力,同时有助于延续摩尔定律。 他认为,工程师能够创造性地解决复杂问题,但人不善于处理海量数据。而 AI 可以在算法指引下并行处理海量数据,并在这个过程中找到规律。当通过新一代 EDA 算法把人工智能和优秀工程师的能力结合在一起时,就可以同时解决高复杂度和大数据量的设计难题,极大地提升智能系统的设计生产力。

他认为,工程师能够创造性地解决复杂问题,但人不善于处理海量数据。而 AI 可以在算法指引下并行处理海量数据,并在这个过程中找到规律。当通过新一代 EDA 算法把人工智能和优秀工程师的能力结合在一起时,就可以同时解决高复杂度和大数据量的设计难题,极大地提升智能系统的设计生产力。

Cadence AI 解决方案引领潮流

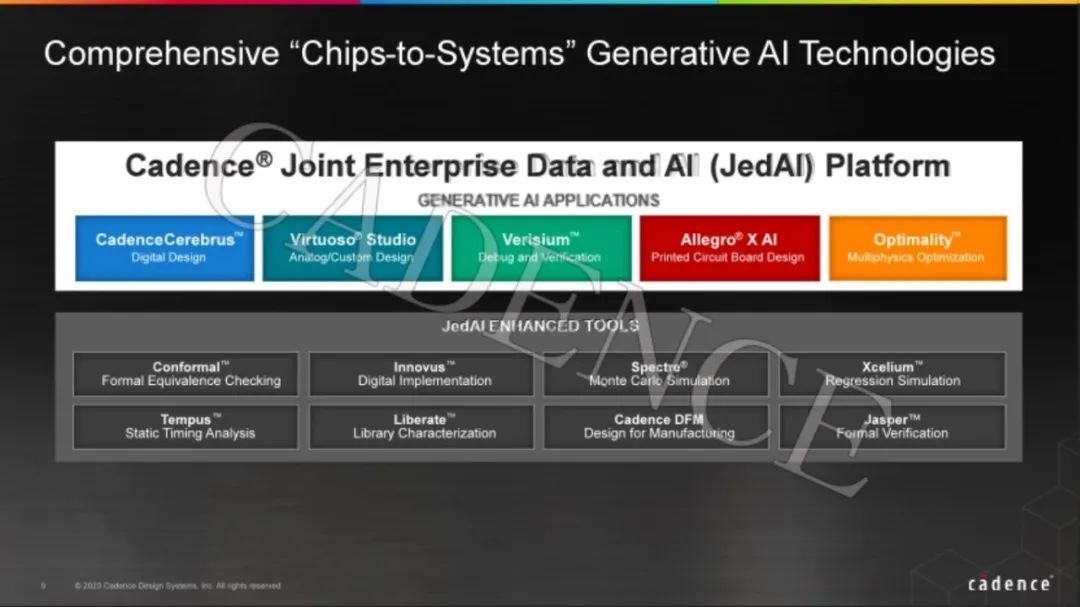

陈敏介绍说,Cadence 同时在两个方面实现了 EDA 的 AI 改造,一是通过 AI 技术提升 EDA 核心解算器的效率;二是通过 AI 处理大量的设计数据,提高人在环内的设计效率,目前多个产品线都有了相应的 AI 功能。 Cadence 全栈 AI 的 EDA 解决方案包括用于更快调试的 Verisium、用于更快更智能芯片设计的 Cerebrus、用于支持 AI 的多物理场系统分析优化且是业界首个提供机器学习(ML)驱动的完整 PCB 综合平台 Allegro X 和提供 AI 驱动的自定义布局解决方案 Virtuoso AI,以及支持 AI 的大数据分析平台——JedAI(联合企业数据和 AI 平台)。 Cadence 的领先技术有助于设计团队利用先进的 AI 驱动解决方案套件优化芯片性能,加速芯片设计并提高整个设计流程的效率,将更多时间用于创新,缩短进入市场的时间。

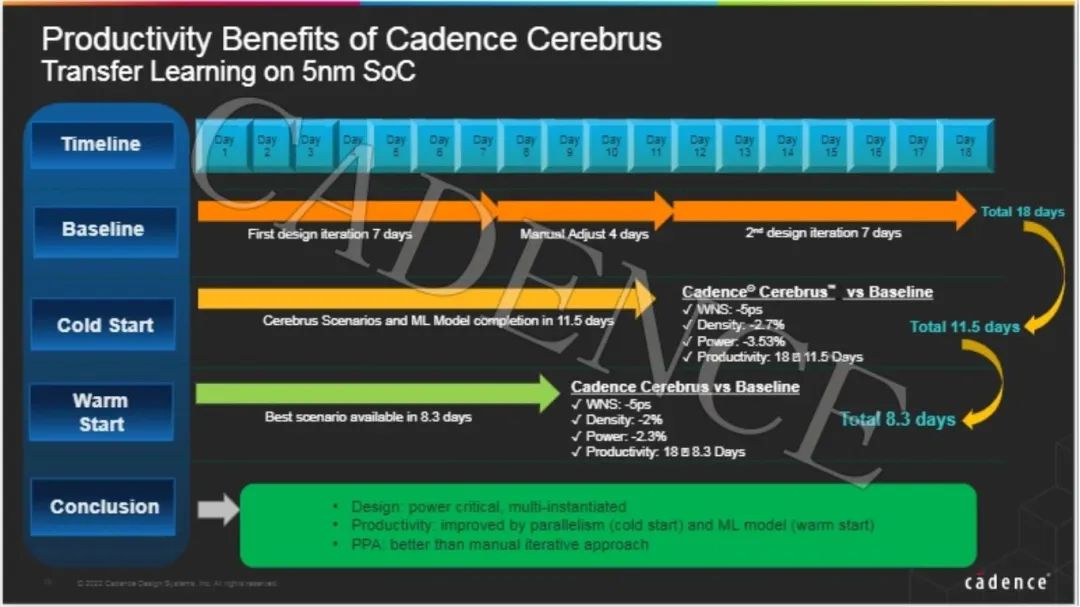

他还分享了 Cerebrus 工作流程让客户受益的案例——在台积电 N5 SoC 上使用 Cerebrus 的客户使用和不使用 ML 驱动优化的设计周期时间表。手动优化需要 18 天才能完成基线优化,而使用 Cerebrus 冷启动,优化流程在 11.5 天内完成,且 PPA 更好;使用ML模型,热启动仅在 8.3 天内就完成了设计收敛,优化周期时间缩短了 53%,功率、密度和 WNS 也得到了改善。

另外,作为 Cadence AI 战略的一部分,其最近推出的 JedAI 可以使设计数据和 AI 训练信息在设计流程的不同部分和不同产品之间轻松传输。这是一项跨 Cadence 的计划,随着时间的推移,越来越多的 Cadence 产品将与 JedAI 原生连接。

AI 将赋能EDA 变革

陈敏指出,AI 将成为 EDA 的一项变革性技术。目前,每个区块都需要大量的人工工程来实现所有的流片目标。现在,设计师可以使用 Cerebrus AI 驱动的优化来提高区块收敛效率和 PPA 效果,不过每个区块仍是独立实施的。 未来,Cadence 的设计收敛将在子系统层面进行,工程师只需研究一个完整的区块子系统。为了实现这一点,Cadence 正在开发一个完整的多块设计中心。利用 AI 自动化,只需一个工程师就可以实现整个子系统,或同时处理多个设计的系统,实现单工程师、多设计、多运行的解决方案。这将是芯片设计的未来。

李志勇

适用大模型 AI芯片的接口 IP

在 IIC Shenzhen 的 EDA/IP 与 IC 设计论坛上,李志勇分享了大语言模型巨大的应用市场对 AI 芯片架构设计提出的诸多挑战,介绍了 Cadence 提供的最先进的 LLM AI SoC 接口 IP 解决方案。

大模型对 AI 芯片设计要求更高

李志勇表示,两年来,以 ChatGPT 为代表的生成式 AI 呈现爆炸式增长,相关硬件需求迅速增加,据 Bloomberg Intelligence 预测,未来 10 年相关产值将从 370 亿美元增长到 6410 亿美元。无论是数据中心还是边缘侧,对 ASIC 的需求都将与日俱增。

大语言模型巨大的市场正在导致 AI 训练/推理芯片的变革,而 Transformer 网络模型需要大量的参数来支撑,对 AI 芯片架构设计提出了更高要求,其中高带宽存储接口、芯片互联、小芯片(Chiplet)都需要高速高带宽的接口 IP。

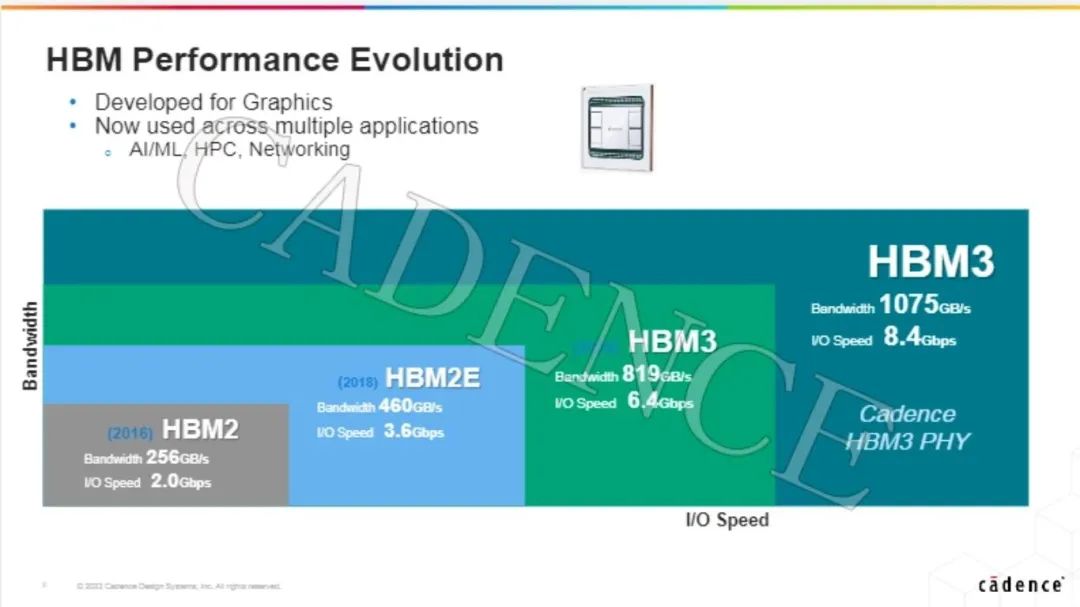

另外,不同 AI 应用场景对内存的要求不尽相同,如带宽、成本和功耗;HBM IO 速率也在发生变化,IO 带宽每三年将翻一番;PCIe 接口标准已演进到 PCIe7,CXL功能也已升级到 3.0,高速以太网在数据中心已大量使用。

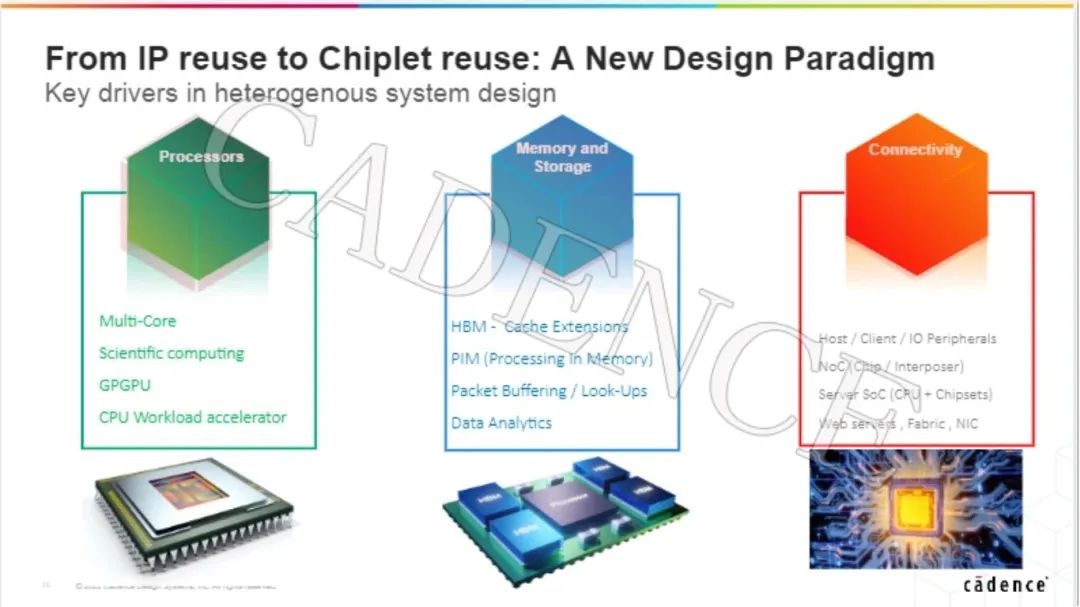

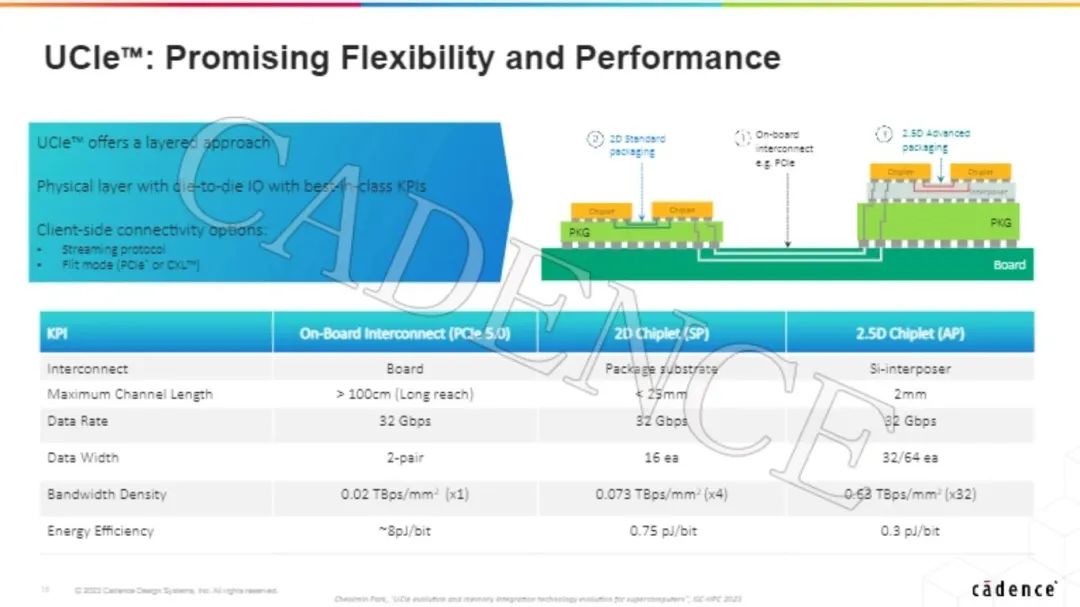

芯片设计方面,在异构系统设计推动下,出现了一种新的设计范式——从 IP 复用到 Chiplet 复用。在 Chiplet 中,利用UCIe可以提高带宽密度和功率效率,进一步降低功耗。

李志勇认为,当前的挑战有三,一是传统芯片和封装设计 EDA 在尺寸/复杂性和先进工艺节点、3D-IC 和高速模拟信号设计;二是芯片以外的系统,包括外壳/PCB/封装/芯片电磁和热设计、安全软件的早期开发以及毫米波和微波射频;三是系统融入智能的需求越来越多,必须提高设计质量,使产品更具可扩展性。

为要求苛刻的应用

树立先进节点新标准

李志勇表示,Cadence 为要求苛刻应用的先进节点提供最先进的接口 HPC/AI LLM IP 解决方案,如 PCIe5/6 和 CXL2 经过硅验证的子系统;112G PHY IP 和 224G PHY IP;硅验证的 LP5x-8533、24G 的 GDDR6 IP 和业界最快的 HBM3 8.4G;以及大规模商用的 Ultralink PHY IP 和最新 UCIe IP。

他介绍说,Cadence HBM3 内存接口是具有 8.4Gbps 最高性能的 PHY IP 完整解决方案;中介层设计是 2.5D 系统设计的关键组件,可为所有 PHY 到 DRAM 连接提供相似的路由长度,以实现最高数据速率。

李志勇还展示了 Cadence 业界首个用于 PCIe 和CXL 的硅 IP 子系统,以及 128G PCIe 7.0-ready SerDes IP,以及已在 Tier1 超标量处理器和前沿初创公司大规模商用的 40G UltraLink D2D PHY+链路层。

助客户成功一臂之力

李志勇强调,UCIe 可以支持标准封装和先进封装,Cadence 112G Serdes PHY 支持 1-112G 速率及以太网等多种协议。Cadence 在 CoWoS 方面的丰富经验也有助于大芯片设计一次成功。

他最后总结道,Cadence 提供完整的 HPC IP 设计套件,包括业界领先的 DDR/HBM/GDDR IP、PCIe/CXL IP 和 D2D 以及 PAM4 IP。这些丰富的 IP 组合可以为各个先进工艺节点提供更高性能的 IP。

关于 Cadence

Cadence 是电子系统设计领域的关键领导者,拥有超过 30 年的计算软件专业积累。基于公司的智能系统设计战略,Cadence 致力于提供软件、硬件和 IP 产品,助力电子设计概念成为现实。Cadence 的客户遍布全球,皆为最具创新能力的企业,他们向超大规模计算、5G 通讯、汽车、移动设备、航空、消费电子、工业和医疗等最具活力的应用市场交付从芯片、电路板到完整系统的卓越电子产品。Cadence 已连续九年名列美国财富杂志评选的 100 家最适合工作的公司。如需了解更多信息,请访问公司网站 www.cadence.com。

2023 Cadence Design Systems, Inc. 版权所有。在全球范围保留所有权利。Cadence、Cadence 徽标和 www.cadence.com/go/trademarks 中列出的其他 Cadence 标志均为 Cadence Design Systems, Inc. 的商标或注册商标。所有其他标识均为其各自所有者的资产。

往期推荐

喜讯!Cadence Verisium 平台荣获 2023 ASPENCORE 全球电子成就奖!

AI 注入 EDA,点燃汽车革命烽火

芯片迈向系统化时代:EDA 软件的创新之路

-

Cadence

+关注

关注

65文章

931浏览量

142555

原文标题:IIC Shenzhen 2023 | Cadence 应对 AI 机遇与挑战,智能重塑芯片设计流程

文章出处:【微信号:gh_fca7f1c2678a,微信公众号:Cadence楷登】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IIC Shenzhen 2023 | Cadence 应对 AI 机遇与挑战,智能重塑芯片设计流程

IIC Shenzhen 2023 | Cadence 应对 AI 机遇与挑战,智能重塑芯片设计流程

评论