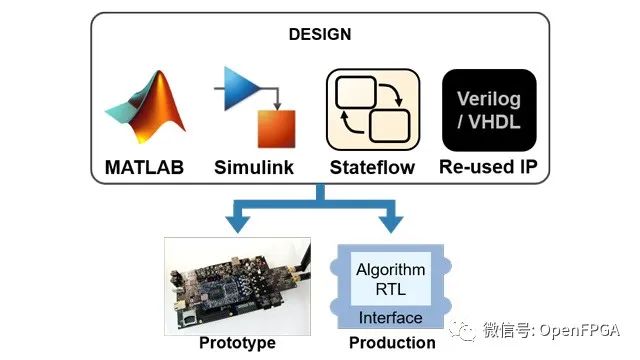

我们将使用实例讲解MATLAB / Simulink HDL 使用入门。

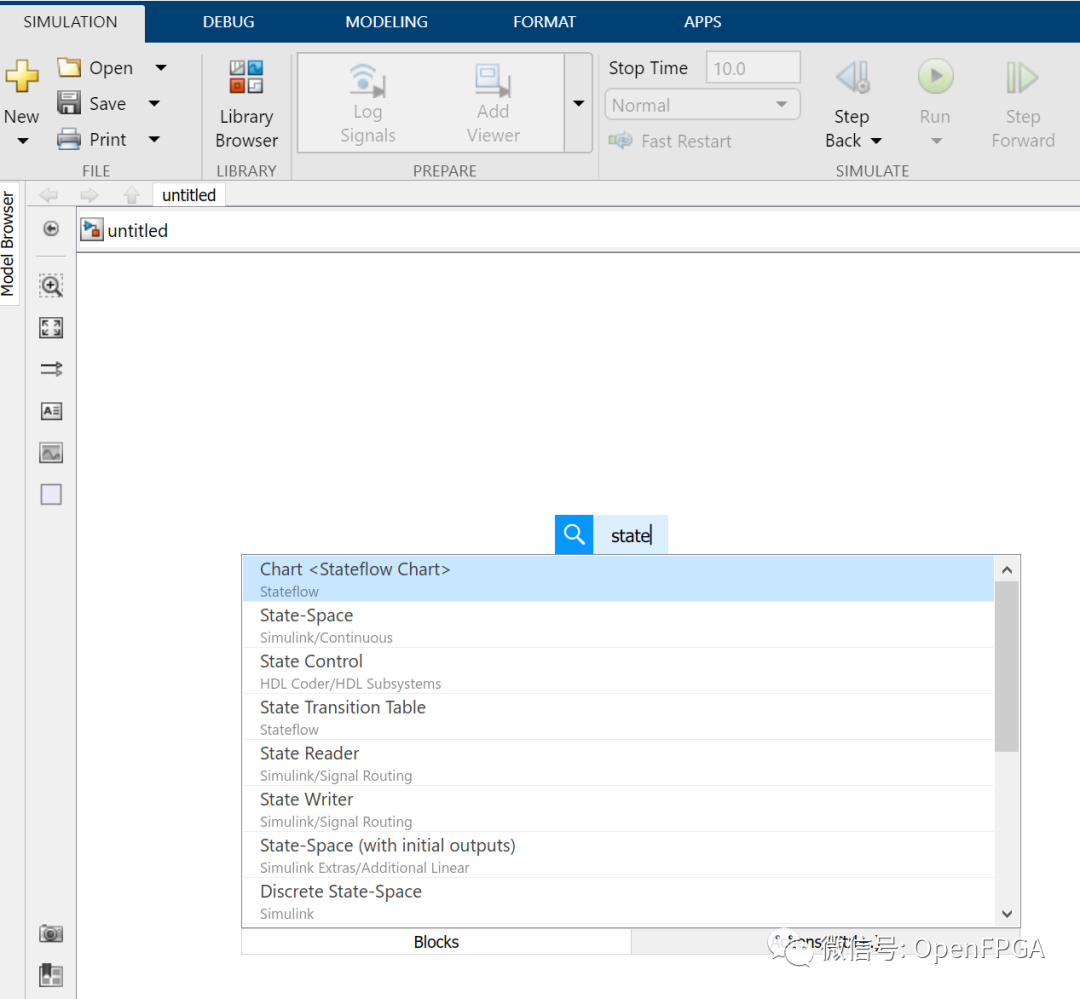

开始这个项目,首先需要创建一个包含 Stateflow 的新 Simulink 。只需单击画布中的任意位置并开始输入 Stateflow。

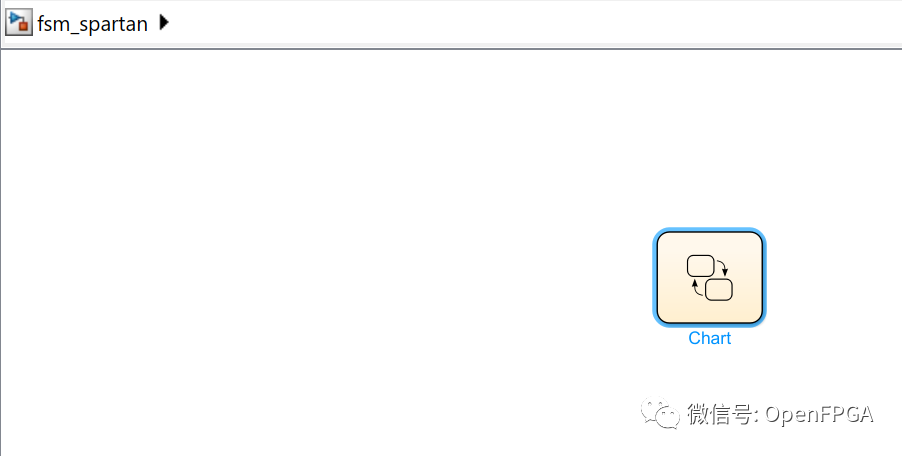

此时应该能在画布上看到 Stateflow 图标。双击图标进行编辑。

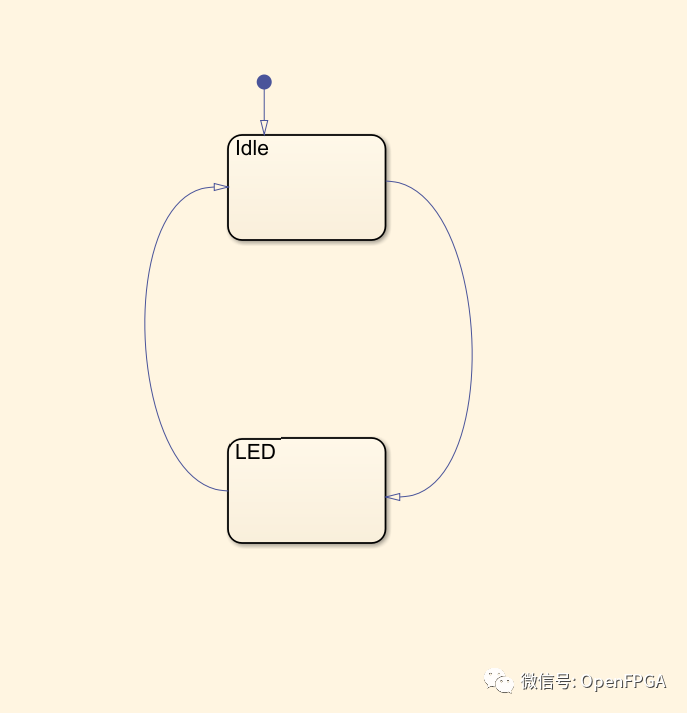

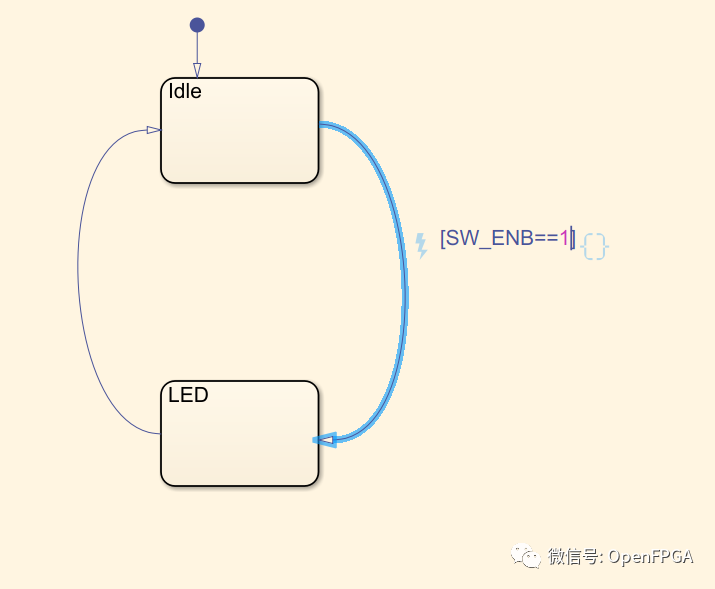

进入图表编辑器后,可以添加状态以及状态之间的转换。开始,我们创建两种状态并将它们命名为“idle”和“LED”。它们之间的转换还没有任何条件。

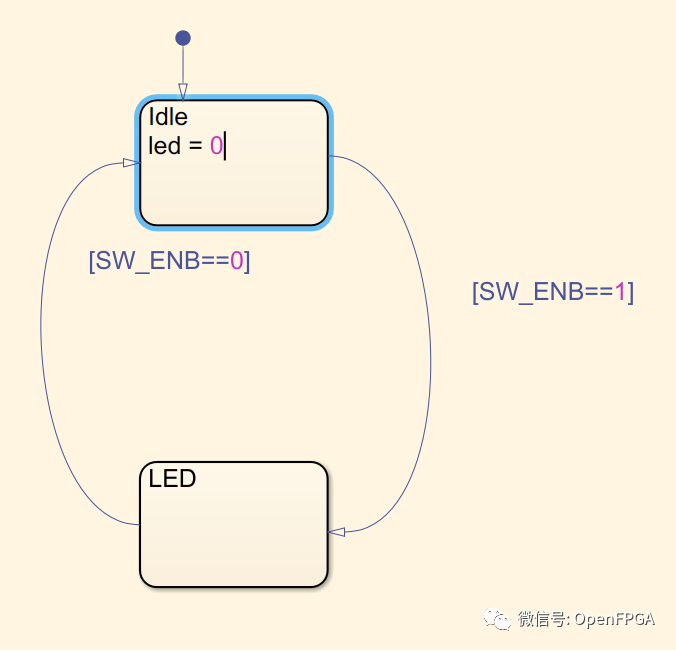

要添加状态转换条件,可以双击转换并输入所需的条件。

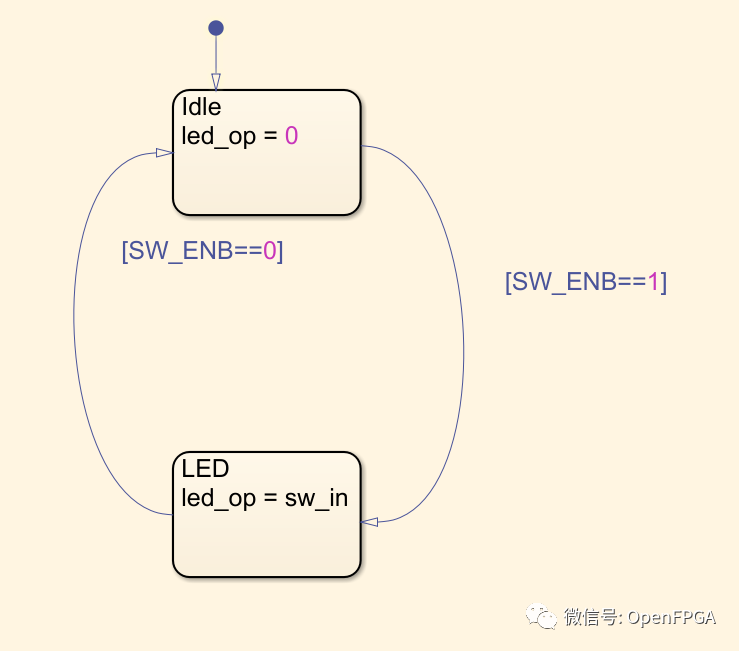

当然,状态机可以具有 Mealey 和 Moore 输出,这些输出作为当前状态 (Moore) 或当前状态和输入 (Mealey) 的函数出现。在本例中,将 LED 输出声明为 Moore 输出,并在每个状态下声明。

最终的结果如下所示。

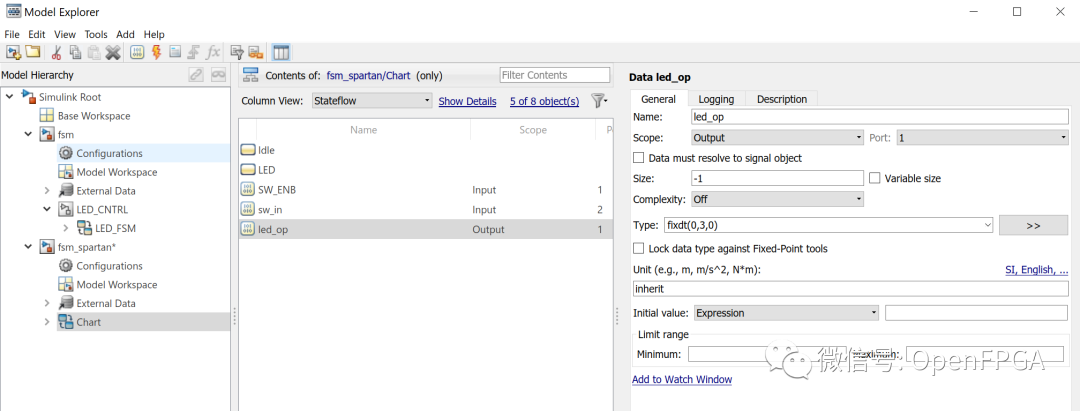

使用模型浏览器,我们可以定义状态机的输入和输出。对于输入,我们将它们保留为与 Simulink 相同的类型,但需要定义输出。由于 LED 需要三位,因此我们使用类型 fixdt(0,3,0)。这意味着向量是三位宽、无符号的,并且没有数字的小数元素。

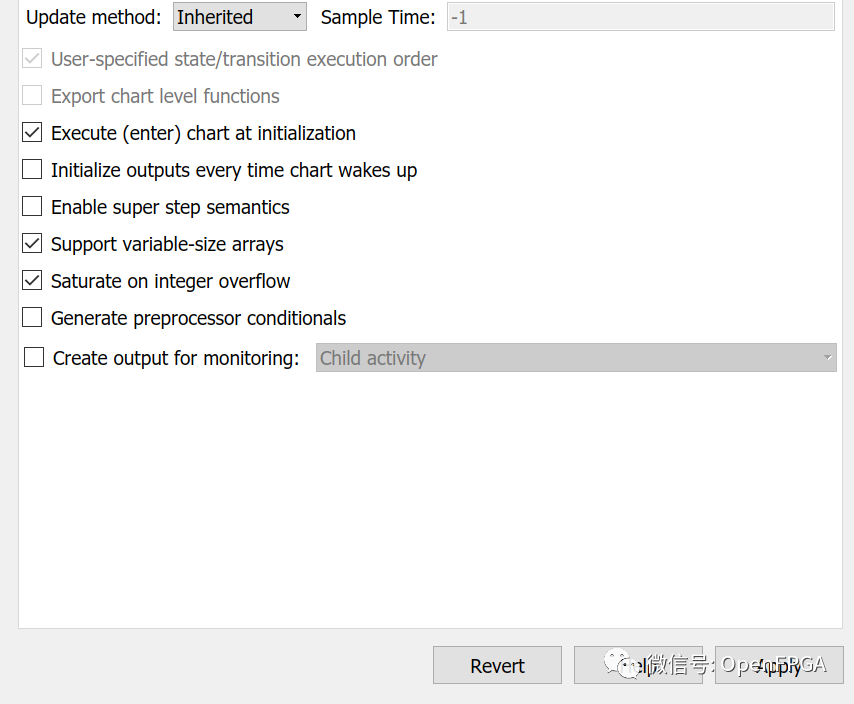

此外,在模型资源管理器中选中“初始化时执行(输入)图表”选项。

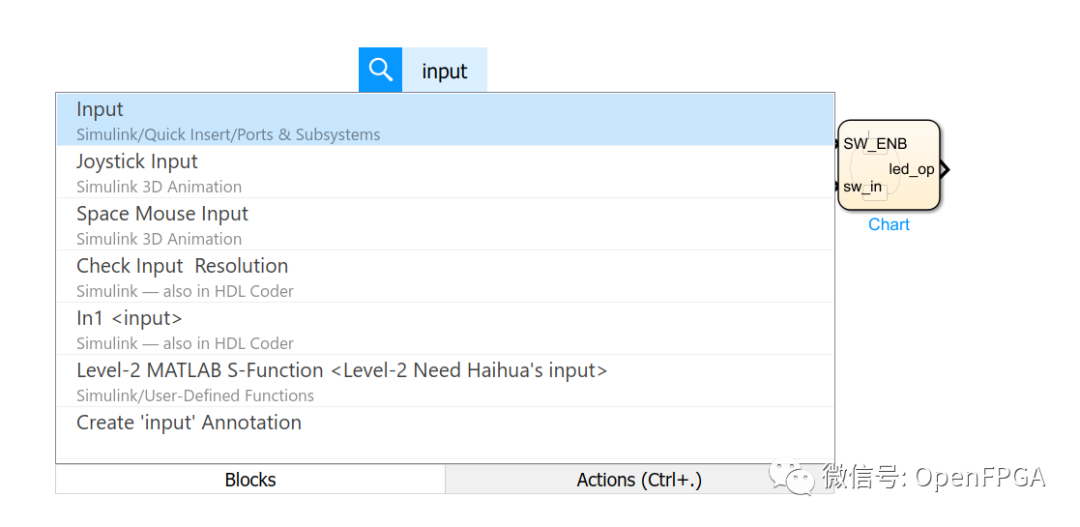

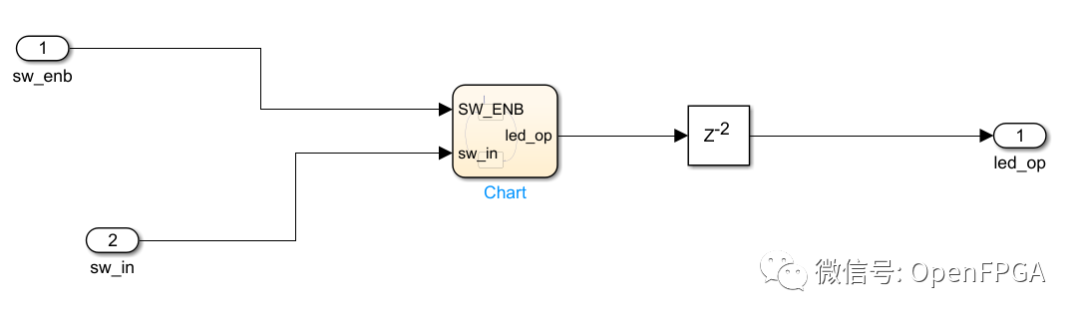

导航到图表上方的画布。这里我们需要添加块的 IO,我们还将添加延迟。在画布中,开始输入输入或输出以获取所需的端口。

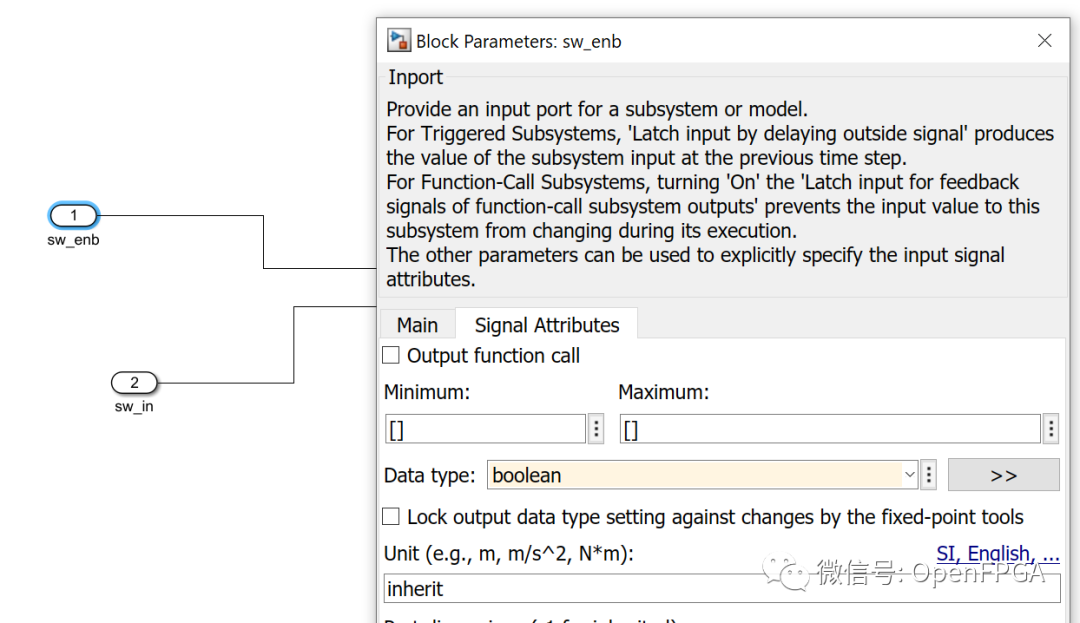

还可以通过双击输入和输出来命名端口,将其设置为正确的类型。

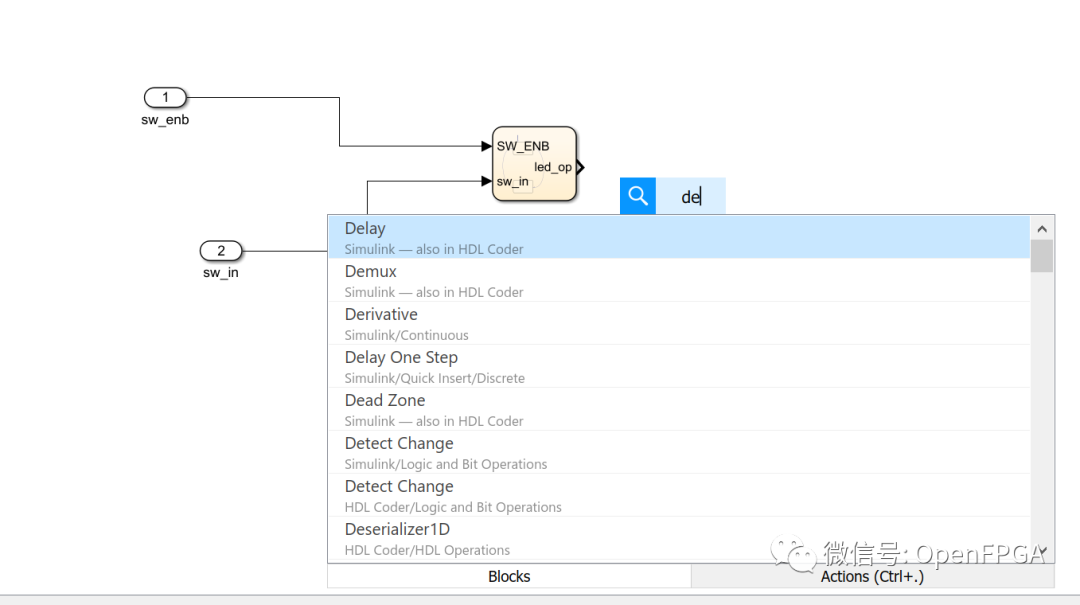

将 sw_in 设置为与之前声明的输出类型相同的 fixdt(0,3,0)。我们使用延迟来添加寄存器。要添加额外的延迟,只需在画布中键入即可。

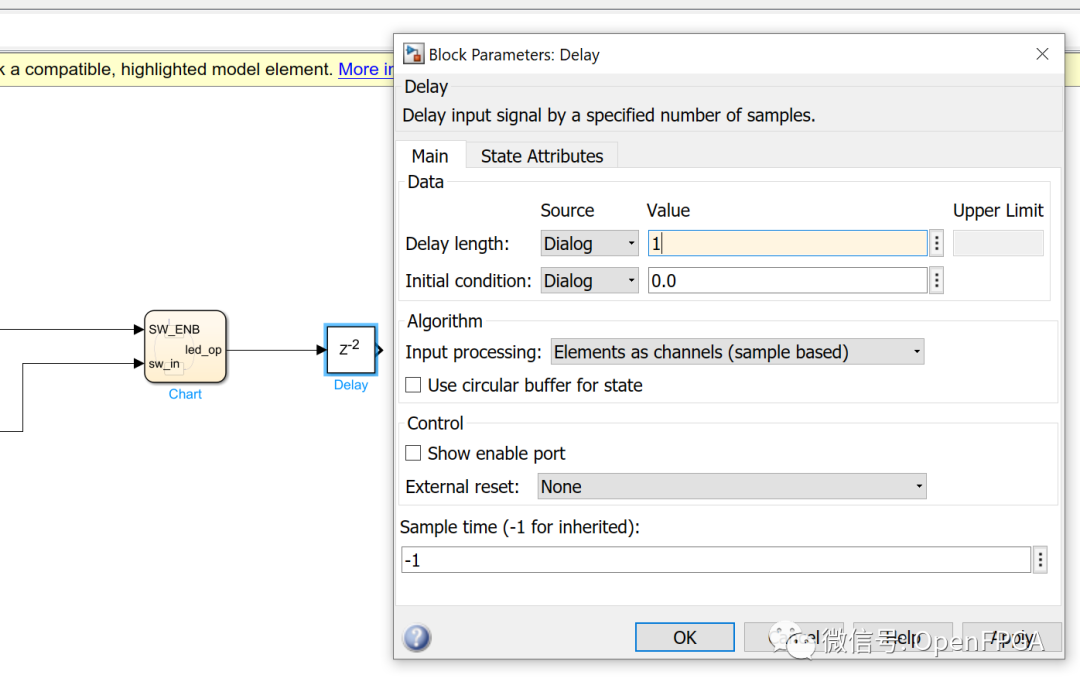

要更改延迟的长度,双击延迟并将其更改为延迟 1。

下图显示了完整的图表。

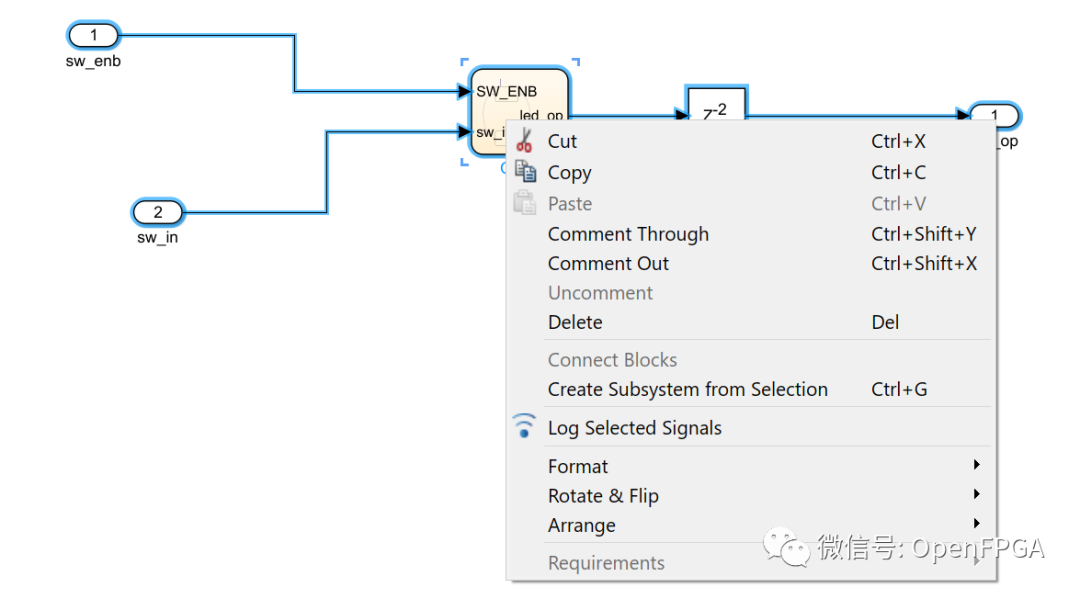

现在我们可以将其生成 RTL,但首先我们将为它创建一个测试平台。选择画布上的所有元素,右键单击它,然后选择从选择创建子系统。

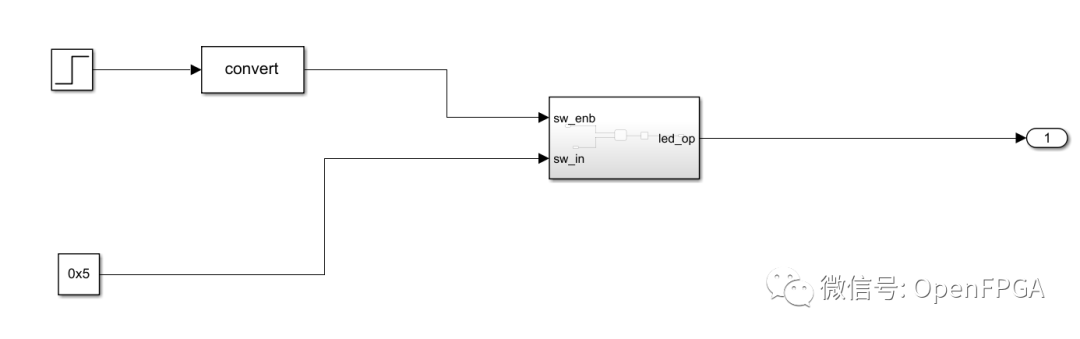

添加阶跃函数和常数,设置子系统模块中使用的模块类型,并确保将离散采样的采样时间设置为 -1。

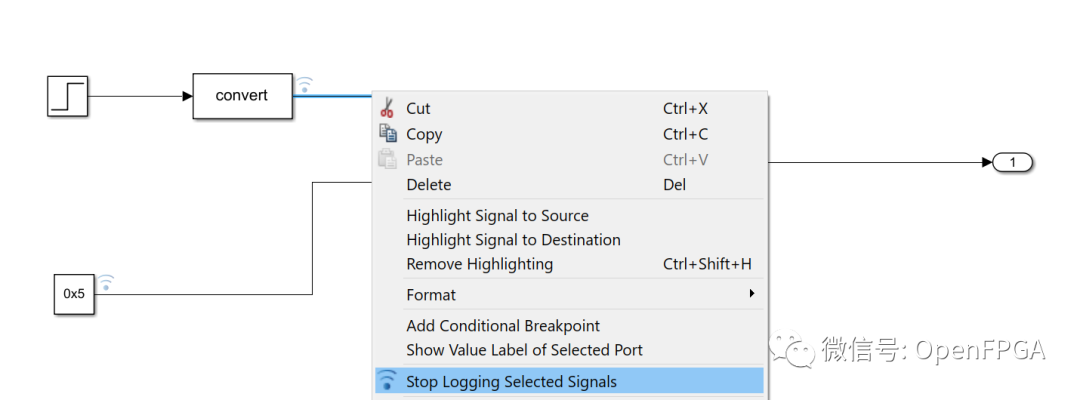

右键单击感兴趣的信号并选择开始记录所选信号。

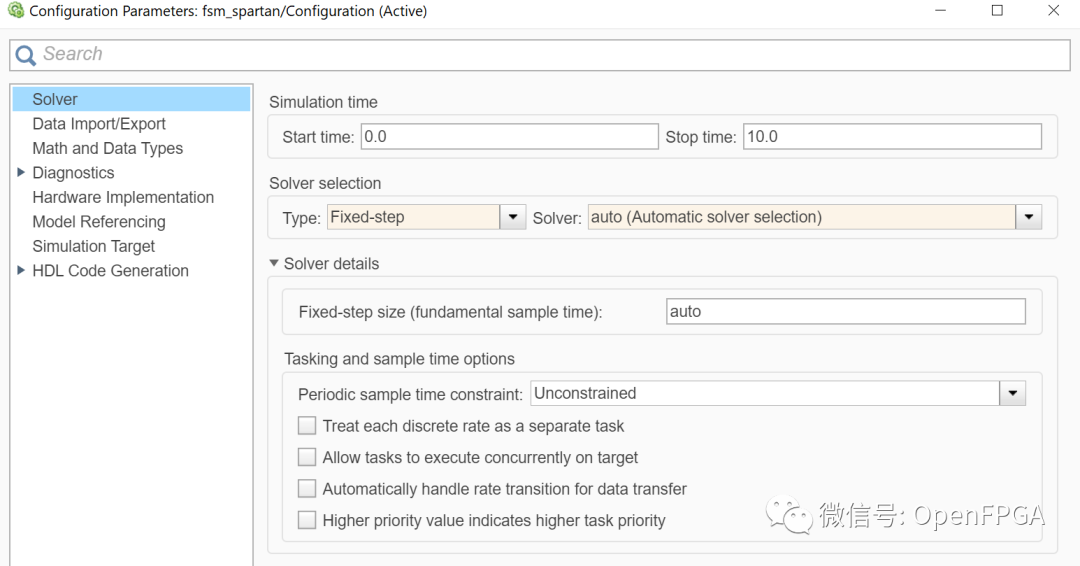

打开模型资源管理器并将模型设置为具有固定步长的计时器的离散时间。

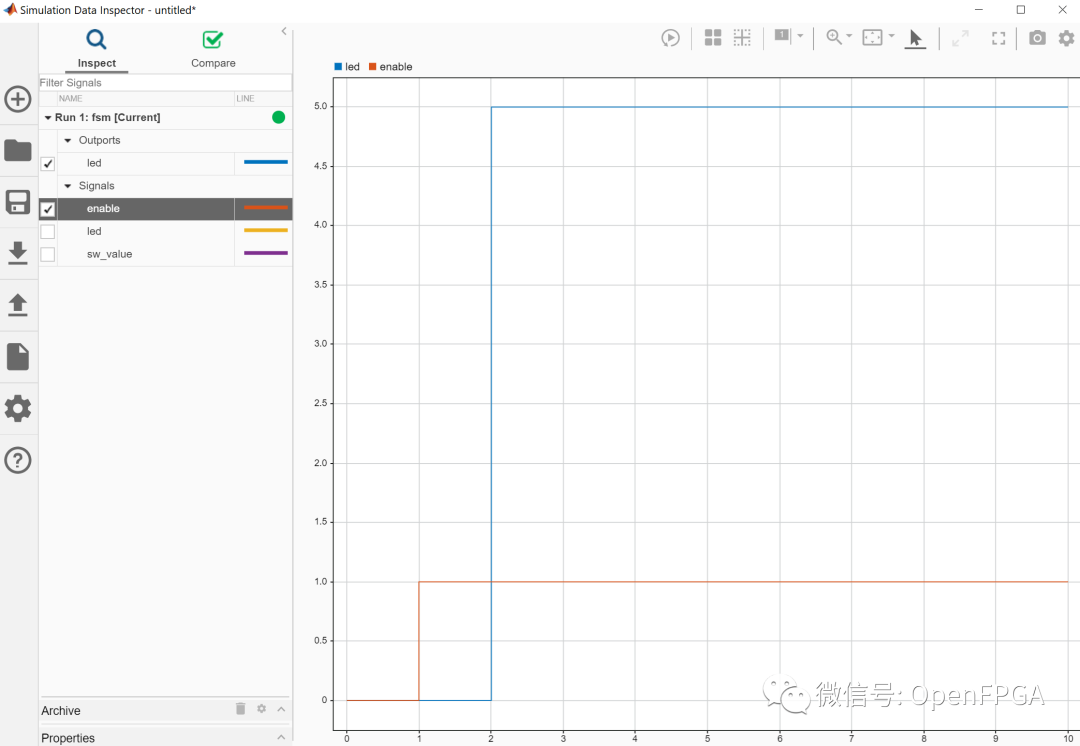

运行模拟并打开数据检查器。应该能够看到 SW_ENB 被置位,并且 LED 输出在下一个时钟后变高。

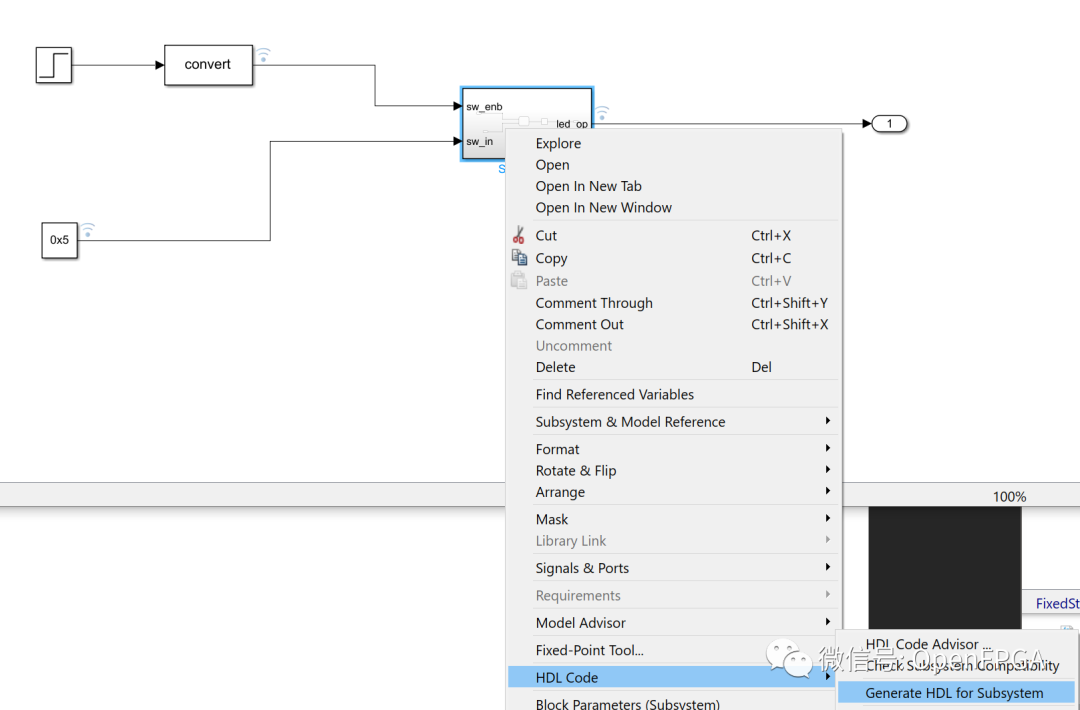

现在我们可以创建 HDL 并将其导出到 Vivado 中使用。我们可以通过右键单击子系统并选择为子系统生成 HDL 来完成此操作。

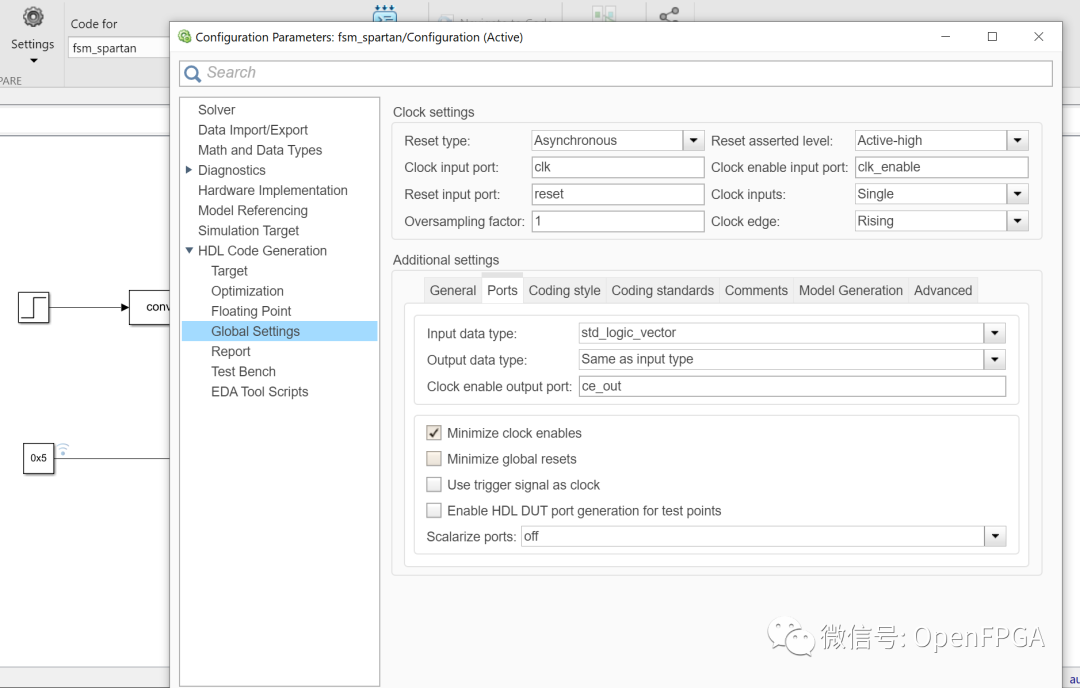

如果要更改任何生成的 HDL 代码格式(即删除时钟启用),需要从 HDL 代码生成选项卡中选择全局设置选项。

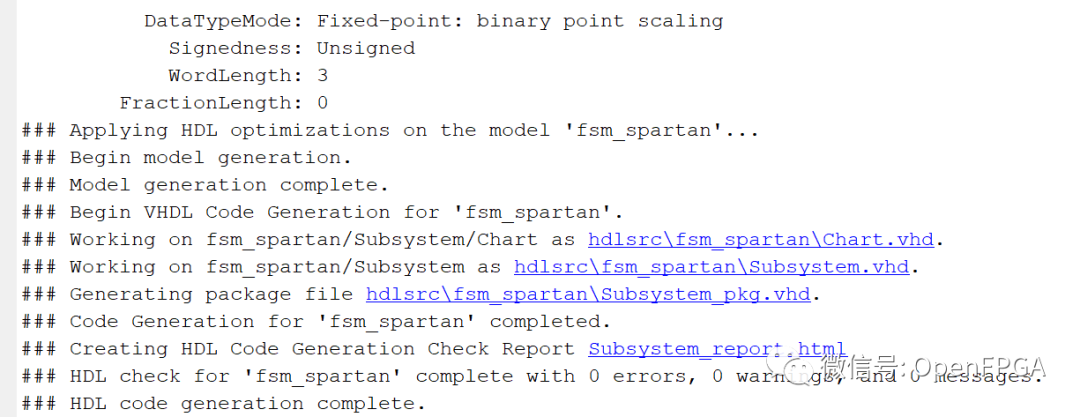

生成代码后,将在生成代码的 MATLAB 窗口中看到一条消息。

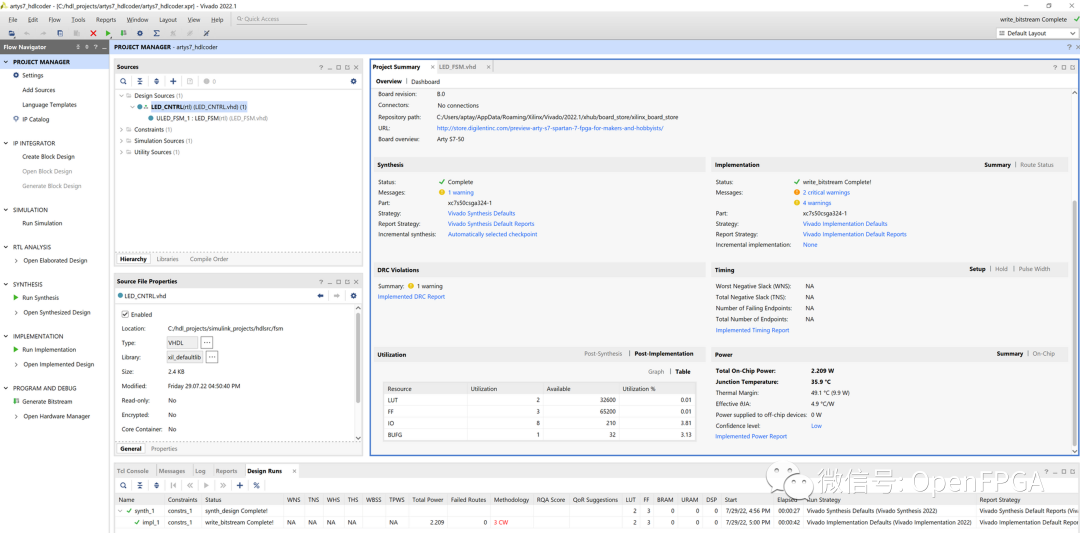

然后可以将该 HDL 导入到 Vivado 项目中。生成的代码本身实际上是可读的,并且取决于我们对 Simulink 图的注释程度。例如,我可以命名状态图,这将反映在case语句名称中。

生成三个 VHDL 文件:包含声明的包、实现状态机的实际源代码以及顶级文件。

在 Vivado 中进行综合,最终设计需要三个触发器和两个 LUT。

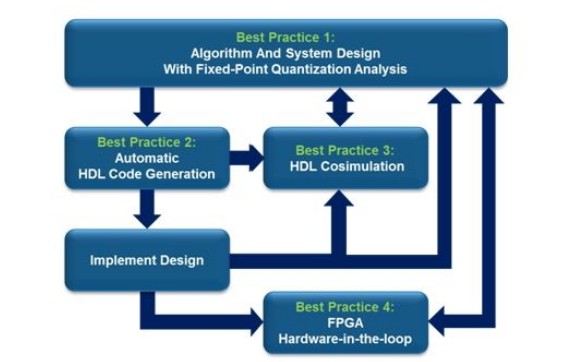

当然,这是一个简单的示例,但能够学习流程,以便可以将它用于更复杂的应用程序。

-

led

+关注

关注

244文章

24731浏览量

692654 -

matlab

+关注

关注

189文章

3029浏览量

239269 -

HDL

+关注

关注

8文章

332浏览量

49055 -

文件

+关注

关注

1文章

598浏览量

26124 -

Simulink

+关注

关注

23文章

552浏览量

66493

原文标题:MATLAB / Simulink HDL 快速入门

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

专家支招:使用MATLAB和Simulink算法创建FPGA原型

使用MATLAB Simulink和HDL编码器创建自定义IP--AWB

初学者的MATLAB_Simulink翻译

什么是MATLAB SIMULINK?Simulink有哪些应用实例?

浅析MATLAB和Simulink嵌入式视觉应用

基于MatLab/Simulink的GPS系统仿真

电路实验与Matlab/Simulink仿真

MathWorks推出基于MATLAB生成HDL代码的产品

MATLAB教程之MATLAB语言的基础知识及入门

讲解MATLAB/Simulink HDL使用入门

讲解MATLAB/Simulink HDL使用入门

评论