佳能计划将新芯片制造设备的价格定在asml最先进的***(optic grapher)费用的非常小的部分,因此正在尖端设备领域取得进展。

佳能首席执行官Fujio Mitarai表示,纳米印花的新技术将为微型半导体制造企业开辟生产最尖端芯片的道路。该产品的价格预计将低于asml用euv设备一位数,但目前还没有最终确定价格。

据悉,asml是唯一的极紫外光刻工具供应商,极紫外线刻印工具是世界上最先进的芯片制造机器,每台价值数亿美元。euv设备是数十年研究和投资的产物,是大规模生产最快、能源效率最高的芯片所必需的。

由于在技术供应链中占据重要位置,目前能够投资到这些工具上的现金充足的企业只是少数。美国向本国的同盟国施压,要求限制技术外流,最终asml被中国顾客禁止出口euv系统。

我们把希望寄托在佳能上月推出的新工艺上。日本今年7月扩大了对半导体制造出口的限制,但并未明确提及纳米压花技术。Mitarai方面表示,佳能公司将无法将这些机器运送到中国。除了14纳米技术以外的所有产品都被理解为禁止出口。

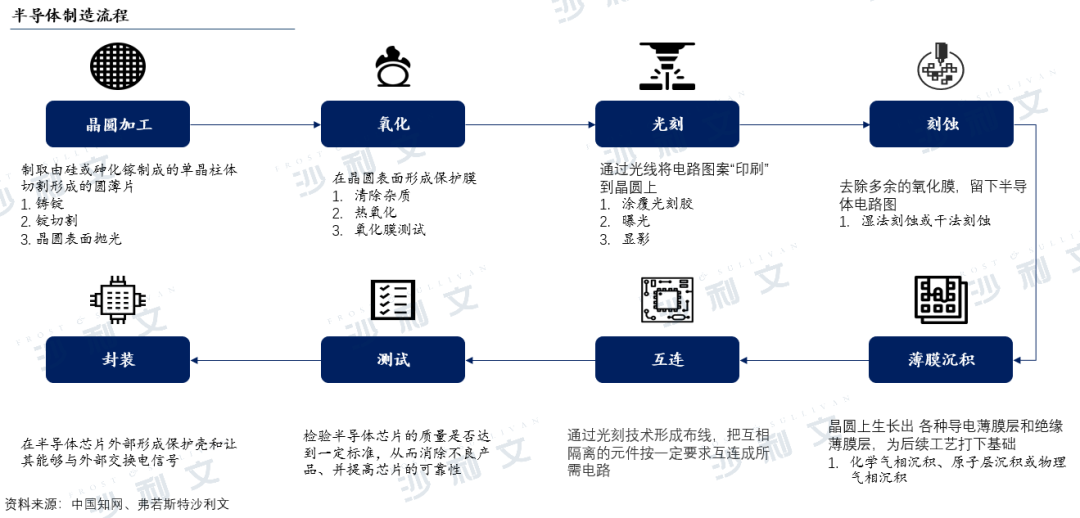

佳能和Dai Nippon Printing Co.股份公司。与存储芯片制造企业被服合作研究纳米压花技术已有近10年的时间。与极紫外光刻技术的反射光不同,佳能技术在晶片上直接印刷电路图案,制造出几何形状的晶片,虽然速度慢得多,但符合最先进的节点。得益于新机器,半导体制造商可以降低对转包工厂的依赖度,台积电公司和三星电子等转包半导体制造商也可以批量生产更多的芯片。佳能表示,这台机器的功率只有euv产品的十分之一。

Mitarai表示:“虽然不认为纳米压纹技术会代替euv,但相信会创造出新的机会和需求,已经有很多顾客前来咨询。”

-

芯片制造

+关注

关注

10文章

627浏览量

28850 -

光刻机

+关注

关注

31文章

1153浏览量

47468 -

ASML

+关注

关注

7文章

718浏览量

41270

发布评论请先 登录

相关推荐

纳米压印光刻技术旨在与极紫外光刻(EUV)竞争

镓在半导体制造中的作用

【「大话芯片制造」阅读体验】+ 半导体工厂建设要求

ESD静电对半导体制造的影响

中国大陆成全球半导体制造设备销售核心市场

台积电张晓强:ASML High-NA EUV成本效益是关键

ASML发货第二台High NA EUV光刻机,已成功印刷10nm线宽图案

阿斯麦(ASML)公司首台高数值孔径EUV光刻机实现突破性成果

佳能预计到2024年出货纳米压印光刻机

佳能纳米压印半导体制造机价格或比ASML EUV设备低一位数

佳能纳米压印半导体制造机价格或比ASML EUV设备低一位数

评论