当今复杂的FPGA含有众多用于实现各种电路与系统的功能块,诸如逻辑阵列、存储器、DSP模块、处理器、用于时序生成的锁相环(PLL)和延迟锁定环DLL)、标准I/0、高速数字收发器以及并行接口(PCI、DDR 等)。这些不同的功能块通常多个时钟驱动,FPGA一般会综合采用外部振荡器以及内部PLL与DLL来生成时钟。设计人员需要综合使用外部与内部资源来实现最佳的时钟树设计。

而可编程时钟振荡器用作FPGA系统的时序参考,可提供一系列优势;其中首要优势是为了实现时钟树优化而进行高分辨率频率选择时所带来的设计灵活性。另一个优势是可以减少电磁干扰的扩频调制功能。

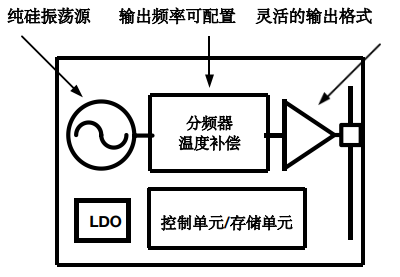

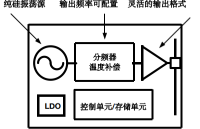

本文主要介绍一种可兼容替换石英晶振或MEMS振荡器的纯硅可编程振荡器,该振荡器是基于纯CMOS工艺,利用自主创新的先进电路和补偿算法来实现高性能的相位稳定性和频率稳定性,相比基于石英晶振的同类产品可提供更高的可靠性。

国产纯硅可编程振荡器可以实现在超宽工业温度范围内频率稳定度优于±50ppm,能产生10kHz至350MHz之间任意频率,且相位抖动性能达到350fs rms的时钟信号。是一种适用于服务器、AI处理器、网络接口、边缘计算、汽车电子以及广泛工业应用的理想时钟源。此外,纯硅振荡器只需要普通的塑封工艺,大大提高了供应链的灵活性和安全性。

可编程纯硅振荡器产品亮点:

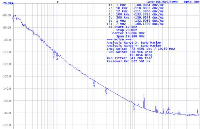

•总稳定度:+/-50ppm(包含10年老化)

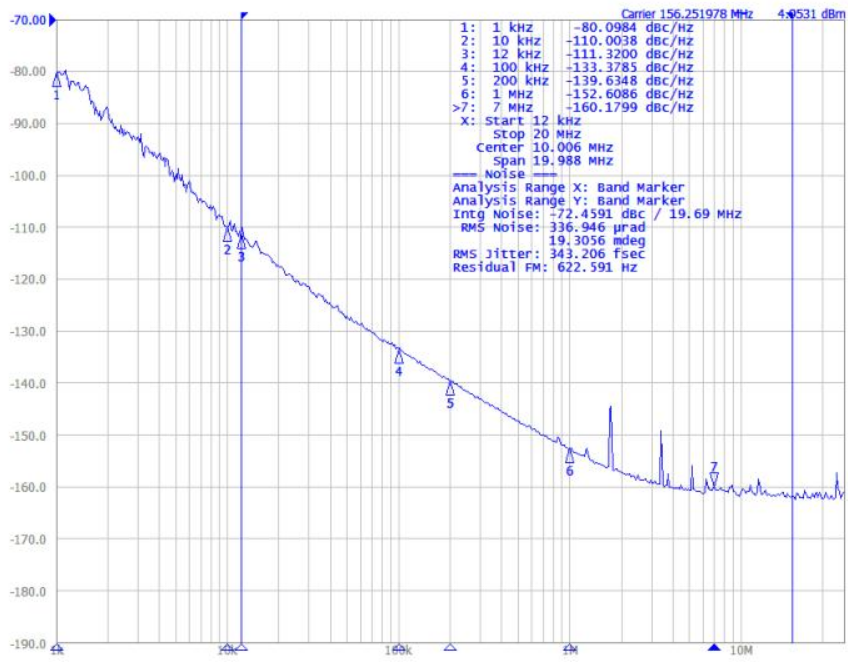

•12kHz~20MHz带宽范围内相位抖动低于350fs

•工业级器件支持-40℃~+85℃工作温度范围

•扩展工业级器件支持-40℃~+105℃工作温度范围

•可支持输出时钟展频SSC、VCXO和DCXO模式

•集成电路级的质量保证和可靠性

•支持单路LVCMOS,双路LVCMOS,LVPECL,LVDS,HCSL及CML等输出格式

•支持多至九种频率配置以及12C可编程频点输出,可替换多个振荡器和多路复用器,从而提高产品的可靠性和性能并降低用户的BOM成本。

•提供与3.2x2.5mm和5.0x3.2mm振荡器行业标准封装兼容的6引脚封装

注:如涉及作品版权问题,请联系删除。

-

FPGA

+关注

关注

1631文章

21806浏览量

606703 -

振荡器

+关注

关注

28文章

3857浏览量

139455 -

驱动

+关注

关注

12文章

1855浏览量

85742 -

国芯思辰

+关注

关注

0文章

1101浏览量

1481

发布评论请先 登录

相关推荐

解析全硅可编程 CMOS 振荡器 SWPM101 系列(0.01 至 212.5 MHz)的卓越特性

利用国产纯硅可编程振荡器可增强FPGA的应用优势

利用国产纯硅可编程振荡器可增强FPGA的应用优势

评论