观看视频,您将了解为什么千兆多媒体串行链路(GMSL) SerDes技术能够提供传输容量激增的多类数据所需的带宽,从而成功在车辆中部署复杂的ADAS和信息娱乐功能。

GMSL

旨在将高速视频链路性能提升到全新水平

ADI公司的千兆多媒体串行链路(GMSL)技术支持在汽车中可靠地传输高分辨率数字视频,从而改变数百万驾驶员的驾驶体验。公路上行驶的车辆中已有超过6亿个GMSL链路,这些车辆来自25家以上的汽车制造商。自2004年以来,部署这些链路的汽车总计行驶了超过20万亿公里,即超过2光年,改善了道路安全、用户界面和车内娱乐,造福于数百万用户。每公里的行驶里程都能提供宝贵的数据以改进下一代GMSL,并通过领先的ASIL兼容解决方案实现视频链路功能安全的新标准。

然而,应用于汽车仅仅是个开始。探索GMSL在安全性、自主性等方面的创新应用,让未来的机器“超越一切可能”。

汽车中的摄像头和显示屏的数量不断增加,图像质量不断提高,因此需要更高的数据速率进行视频传输。GMSL旨在支持这些趋势,并在此过程中简化系统架构。GMSL链路可传输汽车中的所有视频,包括摄像头到计算机、计算机之间以及从计算机到显示屏的视频。摄像头为道路安全、驾驶辅助和智能用户界面提供了支持。显示屏正在取代机械仪表和控件,并为驾驶员提供关键信息和信息娱乐。

ADI公司每一代GMSL的链路数据速率都比上一代提高了一倍。

GMSL1支持高达3 Gbps的链路

GMSL2支持高达6 Gbps的链路

已量产的最新一代GMSL3提供12 Gbps的链路速率

下一代GMSL将继续创新,进一步为更高性能的计算和软件定义应用提供高级特性和功能。

ADI 让新一代GMSL向后兼容上一代产品,从而简化客户从一代GMSL过渡到下一代GMSL的过程。

GMSL

优势展示

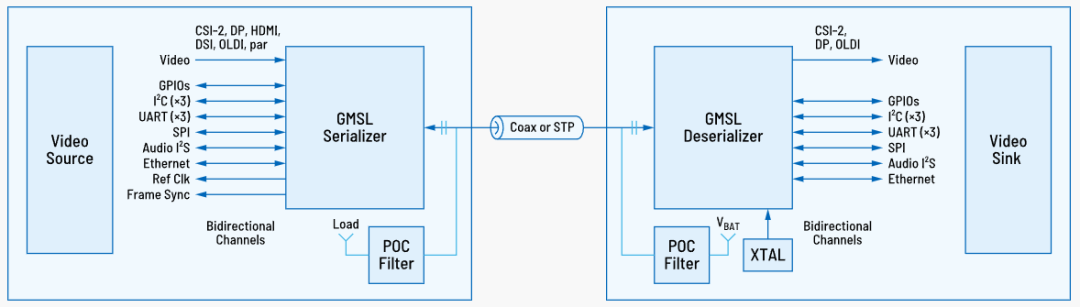

GMSL连接框图

一切通过单根线缆传输

GMSL通过单根同轴电缆或屏蔽双绞线(STP)线缆来桥接ADAS传感器所需的一切。

视频、供电、摄像头和显示屏控制与同步、触控、触觉反馈、时钟、音频、软件更新以及状态报告,全都可以通过同一条线缆同时传输。

采用GMSL的摄像头通常只有一个连接器,该连接器能提供摄像头所需的一切,并将视频从摄像头传输出去。

每个GMSL链路可以传输多个视频流。

更少的连接器和线缆意味着重量更轻、复杂性更低

GMSL能够通过单根线缆来桥接和传输一切,因此降低了布线要求,减少了影音系统的重量、能耗和成本。线缆的减少可提高燃油经济性,或延长电动汽车的续航里程。

显示屏可以采用菊花链连接,从而进一步减少布线。GMSL促进了增量数据聚合,因此车辆变得更轻,制造更简单,操作更简便。

任何视频协议都可以通过GMSL链路桥接到任何其他视频协议。例如,DisplayPort转CSI-2,或HDMI转OLDI。

高性能汽车ASIL串行器/解串器解决方案

ADI的GMSL链路是汽车SerDes市场中性能领先的产品,其数据速率高达12 Gbps,目前已大规模量产。我们的创新以安全性、可靠性和性能为核心。GMSL支持实现所需的任何级别的ASIL解决方案。

完整的低功耗、小尺寸器件组合

ADI的持续创新和100多款优化器件的组合,确保GMSL器件为每种使用场景提供小尺寸和低功耗的解决方案。

审核编辑:汤梓红

-

ADI

+关注

关注

146文章

45819浏览量

249746 -

GMSL

+关注

关注

2文章

28浏览量

15663 -

串行链路

+关注

关注

0文章

7浏览量

8154

原文标题:为什么每辆汽车都需要高速串行链路?

文章出处:【微信号:ADI智库,微信公众号:ADI智库】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速串行链路仿真工具应用实战

高速数据保障交通安全:专用高速视频链路

时钟抖动对高速链路性能的影响

高速时钟如何驱动串行链路?

时钟抖动对高速链路性能的影响

消除高速串行链路的时钟抖动

基于FPGA连接的JESD204B高速串行链路设计需要考虑的基本硬件及时序问题详解

为什么每辆汽车都需要高速串行链路?

为什么每辆汽车都需要高速串行链路?

评论