一、gicv2与gicv3

但是在gicv3之前一直都是使用的giv2,这两者有什么区别?

最近在做实验室的版本兼容,很我一直以为这个gicv2和gicv3版本更新的年代不是很久。最后看了一下gicv2的文章发现在2016年都有了,为什么现在还有gicv2,吐槽一下。不过活还是得干,之前做过关于gicv3的东西,但是现在还得整个gicv2,在基于这个gicv3上进行修改,那么必须对比一下这两个之间的差别。

循序渐进,先整概念,再看源码。

二、概念

1、gic概念

gic : general interrupt controller

分类

GIC中断控制器的分类:gicv1(已弃用),gicv2,gicv3,gicv4

• ◾gic400,支持gicv2架构版本。

• ◾gic500,支持gicv3架构版本。

• ◾gic600,支持gicv3架构版本

核心功能

gic的核心功能,就是对soc中外设的中断源的管理,并且提供给软件,配置以及控制这些中断源。

• ◾当对应的中断源有效时,gic根据该中断源的配置,决定是否将该中断信号,发送给CPU。如果有多个中断源有效,那么gic还会进行仲裁,选择最高优先级中断,发送给CPU。

• ◾当CPU接受到gic发送的中断,通过读取gic的寄存器,就可以知道,中断的来源来自于哪里,从而可以做相应的处理。

• ◾当CPU处理完中断之后,会告诉gic,其实就是访问gic的寄存器,该中断处理完毕。gic接受到该信息后,就将该中断源取消,避免又重新发送该中断给cpu以及允许中断抢占

gicv3较gicv2的特点

GICv3架构是GICv2架构的升级版,增加了很多东西。变化在于以下:

• ◾使用属性层次(affinity hierarchies),来对core进行标识,使gic支持更多的core

• ◾将cpu interface独立出来,用户可以将其设计在core内部

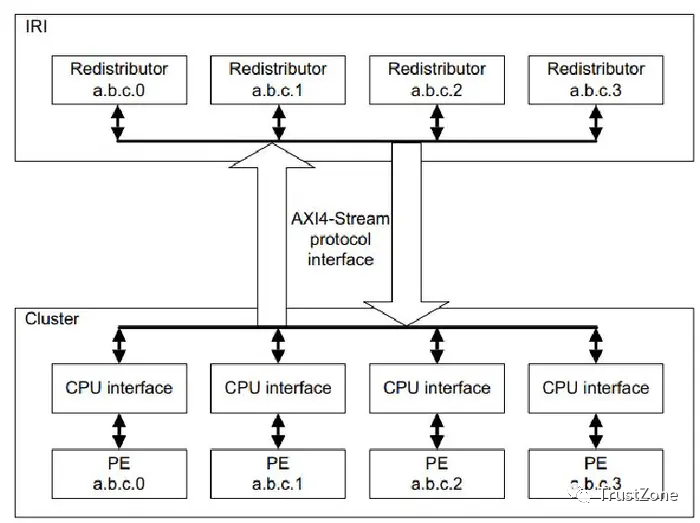

• ◾增加redistributor组件,用来连接distributor和cpu interface

• ◾增加了LPI,使用ITS来解析

• ◾对于cpu interface的寄存器,增加系统寄存器访问方式

-

cpu

+关注

关注

68文章

10860浏览量

211719 -

中断

+关注

关注

5文章

898浏览量

41492 -

gic

+关注

关注

0文章

14浏览量

6270

发布评论请先 登录

相关推荐

ARM GIC(一)之ARM soc中断的处理介绍

ARM GIC(三)之GICv2架构的组成及其功能简析

ARM GIC(四) 之GICv3架构基础知识介绍

ARM GIC(八)GICv3架构的变化

ARM GIC(十一) gicv3架构中的2种安全状态

ARM GIC(十二) GICv3支持中断bypass功能

有关ARM GICv3中断控制器的相关知识介绍

ARM GIC对soc中外设中断源的管理介绍

介绍arm GICv3和timer虚拟化的支持

Arm通用中断控制器GICv3和GICv4对虚拟化的支持

GICv3和GICv4软件概述

将GICv2中断控制器与ARM Cortex-A5x和Cortex-A72处理器集成

gic和ARM Core的连接

gicv2与gicv3的区别

gicv2与gicv3的区别

评论