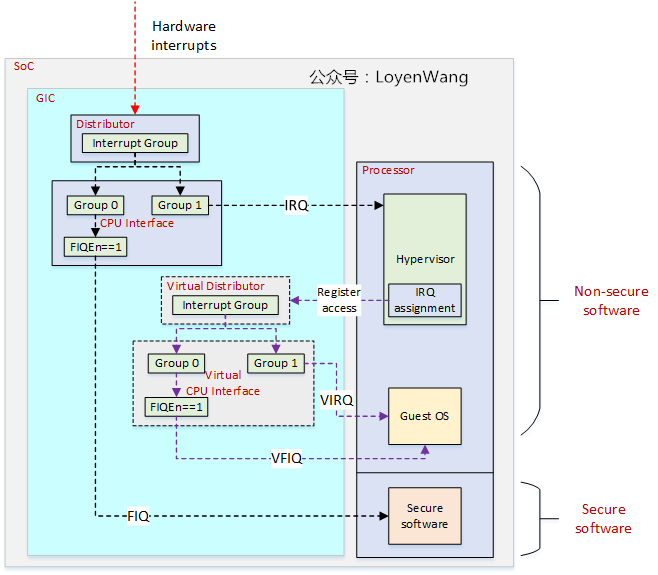

ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递

• ◾nIRQ:物理普通中断

• ◾nFIQ: 物理快速中断

• ◾nVIRQ: 虚拟普通中断

• ◾nVFIQ: 虚拟快速中断

(2)gicv3和ARM Core的连接

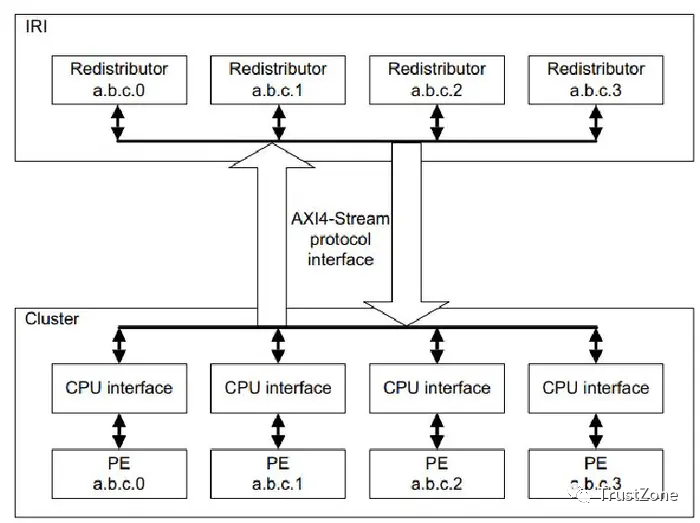

gicv3 AXI-stream协议

• ◾gic stream协议,是基于AXI-stream协议。用于gic的IRI组件,和cpu interface之间,传输信息。

• ◾distributor,redistributor和ITS,统称为IRI组件(interrupt routing

infrastructure)。

• ◾gic stream协议,包含以下2个接口:

• (1)下行AXI-stream接口:用于IRI向cpu interface传递信息,连接

• (2)上行AXI-stream接口:用于cpu interface向IRI传递信息

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ARM

+关注

关注

134文章

9203浏览量

370791 -

中断

+关注

关注

5文章

900浏览量

41953 -

gic

+关注

关注

0文章

14浏览量

6307

发布评论请先 登录

相关推荐

ARM GIC(一)之ARM soc中断的处理介绍

的桥接器件,就是arm公司推出大名鼎鼎的gic,general interrupt controller。gic其实是一个架构,版本历经了gicv1(已弃用),gicv2,gicv3,gicv4。对于

发表于 04-06 10:12

ARM GIC(二)之中断术语的定义

ARM在GIC中,对于中断,定义了如下的一些术语。一、中断状态对于每一个中断而言,有以下4个状态:◾inactive:中断处于无效状态◾pending:中断处于有效状态,但是cpu没有响应该中断

发表于 04-06 10:15

ARM GIC(三)之GICv2架构的组成及其功能简析

ARM的cpu,特别是cortex-A系列的CPU,目前都是多core的cpu,因此对于多core的cpu的中断管理,就不能像单core那样简单去管理,由此

发表于 04-06 10:26

ARM GIC(四) 之GICv3架构基础知识介绍

的使用MPIDR_EL1寄存器,来标识core是一样的。每个core,连接一个cpu interface,而cpu interface会连接gic

发表于 04-06 10:33

ARM GIC(八)GICv3架构的变化

GIC,是arm为了实现复杂的中断控制,而定义的一套架构。版本也历经了多个变化,从最初的GICv1到现在最新的GICv4。每一个新的版本,都增加了一些新的功能。目前最新的GIC-600 IP,支持

发表于 04-07 10:59

ARM GIC(十二) GICv3支持中断bypass功能

在GICv2架构中,GIC与core之间,是直接通过irq,fiq管脚,传递中断信号。但是在GICv3架构中,GIC通过gic stream接口向cpu interface传递中断信息

发表于 04-08 10:10

ARM GIC电源管理使用手册指南

背景介绍GIC电源管理,ARM官方手册,只有一页描述:1、在符合GICv3体系结构的实现中,CPU接口和PE必须位于同一个位置power domain,但它不必与关联的Redistributor所在

发表于 05-27 16:41

ARM GIC对soc中外设中断源的管理介绍

1、ARM GIC简介与Linux中断处理分析先简单说明一下GICGIC即general interrupt controller。它是一个架构,版本历经了GICv1(已弃用),GICv2

发表于 05-27 16:53

一文解析ARM GIC中断线映射与GICD寄存器配置

1、ARM GIC中断线映射与关键寄存器配置中断生命周期generate:外设发起一个中断distribute:distributor对收到的中断源进行仲裁,然后发送给对应的cpu

发表于 05-27 17:24

浅谈OpenHarmony LiteOS-A内核之基础硬件——中断控制器GIC400

公司功能更强大的Cortex-A/R系列的芯片,GIC是ARM公司给Cortex-A/R系列芯片提供的一个中断控制器,在移植OpenHarmony LiteOS-A内核到特定板子的实践中,我们遇到了很多

发表于 10-27 12:20

GIC是什么意思 GIC硬件原理

GIC硬件原理 ARM公司提供了一个通用的中断控制器 GIC(Generic Interrupt Controller) , GIC 的版本包括 V1 ~ V4 ,由于本人使用的SoC

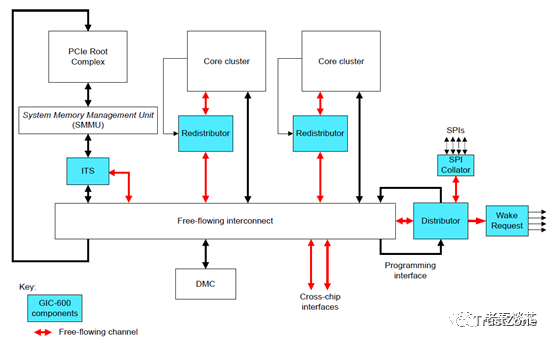

GIC-600的组件是如何连接的

为了适应大规模的SoC设计,GIC-600被设计成分布式IP。 所谓分布式,GIC-600由几种组件构成,每个组件可以跟其它相关模块在物理设计上摆放在一起,并与其拥有共同的电源域;组件之间通过片上网

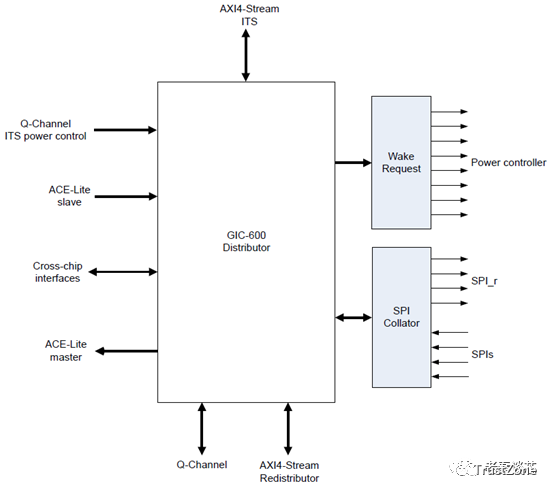

GIC-600的内部结构组件

所有的中断,并转发给相应的目标core。 图3 GIC-600 distributor和SPI collator 对于core来说,可以通过上图中的ACE-Lite slave接口访问GIC

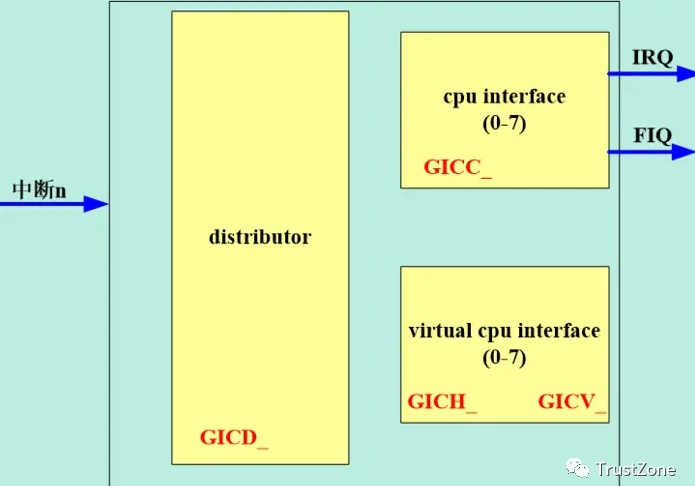

gic的组件介绍

的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。 • cpu interface:将

gic和ARM Core的连接

gic和ARM Core的连接

评论