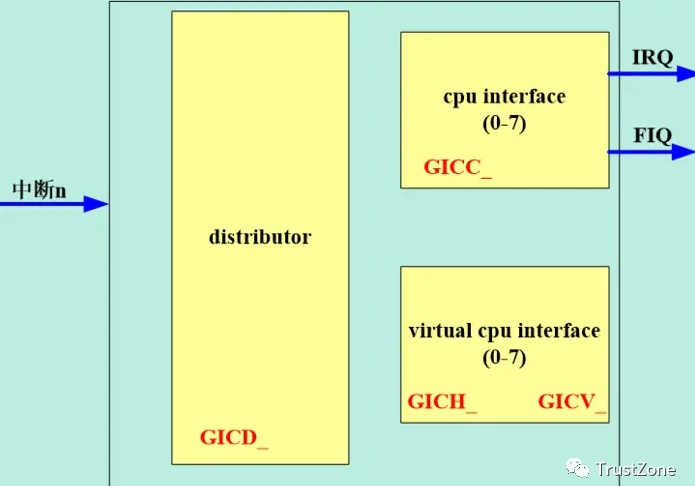

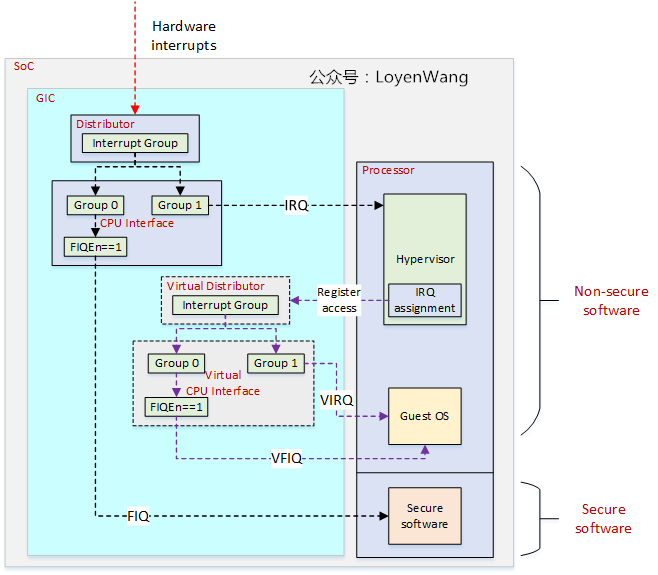

(1)gicv2的组件

在GICv2中,最大支持8个core

• distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI是所有core共享的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。

• cpu interface:将GICD发送的中断信息,通过IRQ,FIQ管脚,传输给core。每一个core,有一个cpu interface。

• virtual cpu interface:将GICD发送的虚拟中断信息,通过VIRQ,VFIQ管脚,传输给core。每一个core,有一个virtual cpu interface。

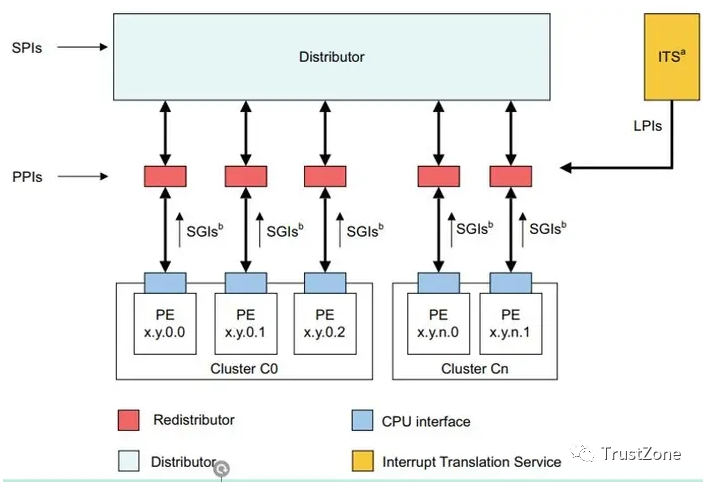

(2)、gicv3的组件

• distributor:SPI中断的管理,将中断发送给redistributor

• redistributor:PPI,SGI,LPI中断的管理,将中断发送给cpu interface

• cpu interface:传输中断给core. (实现在core内部的)

• ITS (Interrupt Translation Service components ):用来解析LPI中断。

-

SPI

+关注

关注

17文章

1730浏览量

92728 -

中断

+关注

关注

5文章

900浏览量

41953 -

gic

+关注

关注

0文章

14浏览量

6307

发布评论请先 登录

相关推荐

ARM之中断GIC分析

ARM GIC(一)之ARM soc中断的处理介绍

ARM GIC(二)之中断术语的定义

ARM GIC(八)GICv3架构的变化

ARM GIC对soc中外设中断源的管理介绍

小电阻器对治理电网GIC的效果分析

应用K值算法的甘肃电网GIC-Q扰动计算

扒一扒GIC-600的相关知识

GIC是什么意思 GIC硬件原理

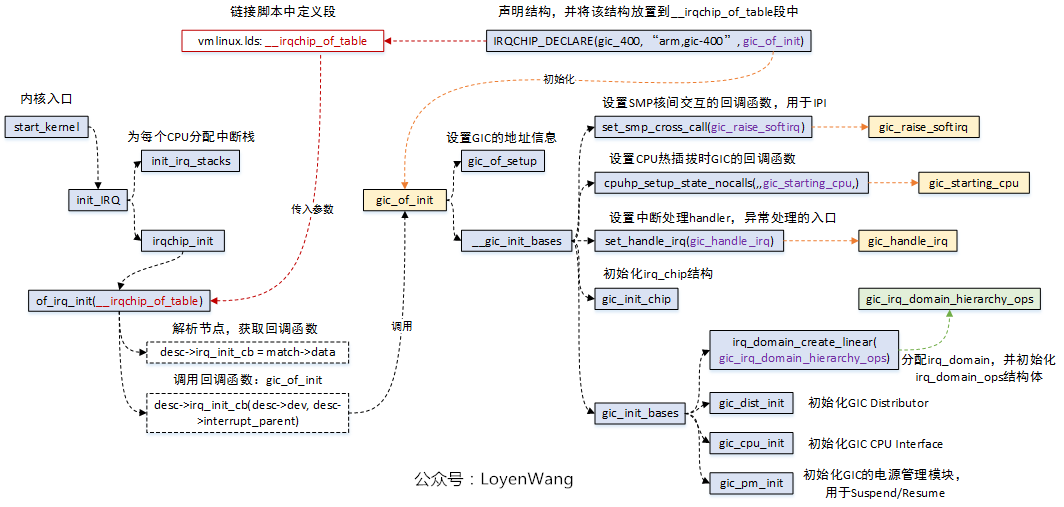

GIC驱动的执行流程是什么

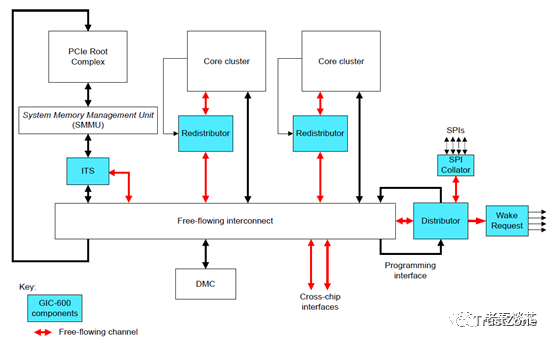

GIC-600的组件是如何连接的

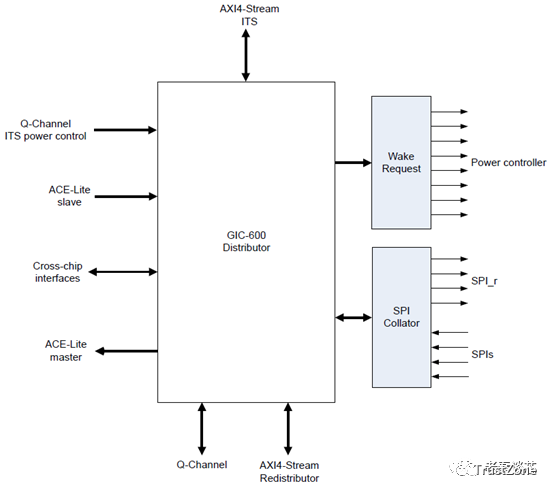

GIC-600的内部结构组件

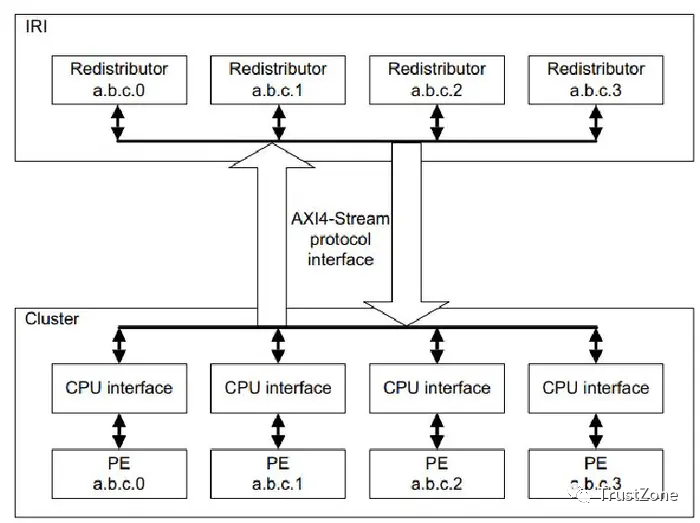

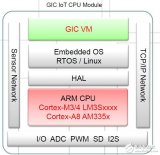

gic和ARM Core的连接

gic的组件介绍

gic的组件介绍

评论