点击蓝字关注我们

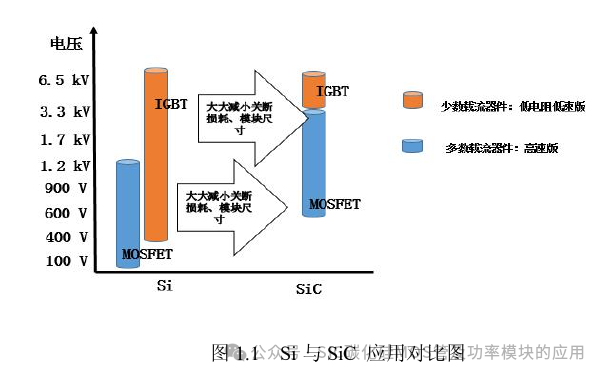

对于高压开关电源应用,碳化硅或SiC MOSFET与传统硅MOSFET和 IGBT相比具有显著优势。SiCMOSFET很好地兼顾了高压、高频和开关性能优势。它是电压控制的场效应器件,能够像IGBT一样进行高压开关,同时开关频率等于或高于低压硅MOSFET的开关频率。之前的文章中,我们介绍了SiCMOSFET特有的器件特性和如何优化SiC栅极驱动电路。今天将带来本系列文章的第三部分SiC MOSFET的封装、系统性能和应用。

封装

WBG半导体使高压转换器能够在更接近低压转换器(低于100V)开关频率的情况下工作。对于低压转换器而言,半导体封装的发展对当今开关性能的实现起到了关键作用。硅MOSFET封装取得了进步,例如双面散热、夹焊、热增强功率封装和低电感、无引线封装。同样,栅极驱动器IC封装也“瘦身”明显。更短的芯片到引线、键合线连接,加上模制无引线封装(MLP),对于最大限度地减少驱动器侧的寄生电感至关重要。驱动器和MOSFET(DrMOS)共封装是减少寄生电感、提高效率和缩小电路板面积的最新步骤。DrMOS得以实现也是因为引入了类似低压转换器应用中所使用的封装改进措施。

在高压转换器领域,爬电距离和电气间隙等最小间距要求使得高性能 SiC MOSFET依然采用低性能To−220型和To−247型封装。这些封装已经十分完善,长期以来一直是行业标准。它们非常适合工业应用,坚固且易于散热,但其长引线和内部键合线导致寄生电感更高。SiC MOSFET现在使这些寄生电感受到热应力、频率和dV/dt速率的影响,以前在高压硅晶体管中,这是从未设想到的。可以说,SiC促进了对高压分立封装的重新思考。

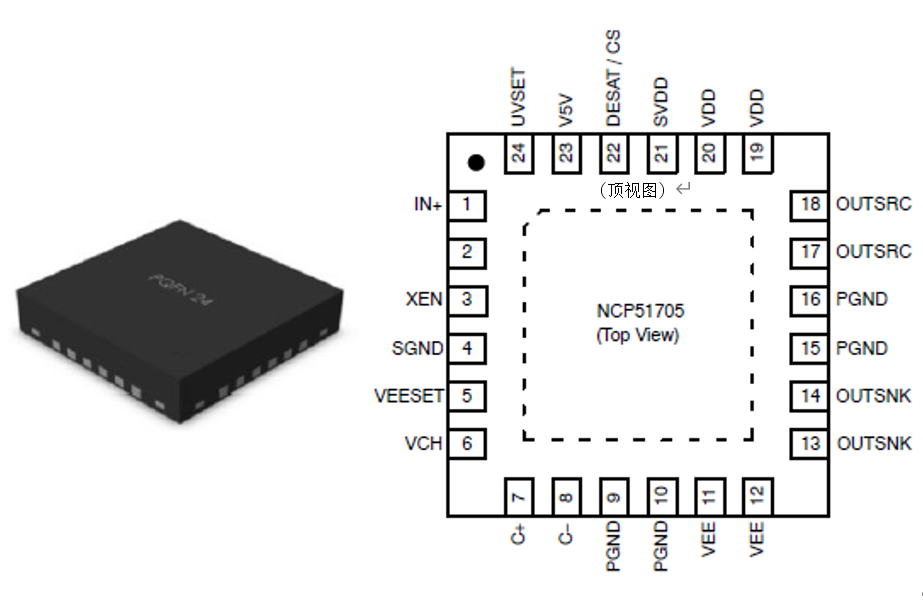

不像分立器件,SiC栅极驱动器能够充分利用那些原本用于低压电源转换器的驱动器件的封装改进。NCP5170芯片封装成24引脚、4x4 mm、热增强MLP,如图15所示。

图15.NCP51705 24引脚、4x4mm、MLP封装和引脚输出

所有高电流电源引脚都布了两个,位于IC的右半部分。此外,这些引脚都通过内部双键合线连接到芯片,以实现尽可能最低的电感。所有低功耗数字信号仅为单引脚,位于IC的左半部分,为PWM或数字控制器提供了方便、直接的接口。

NCP51705封装的底部包括一个电绝缘、导热、暴露的焊盘。该焊盘未连接到PGND或SGND,但会通过热通孔连接到隔离铜PCB焊盘进行散热。

如果散热成为一个问题,应特别注意四个主要的功耗因素:

-

与驱动外部SiC MOSFET相关的OUTSRC和OUTSNK损耗。这些是与开关频率成比例的栅极电荷相关损耗。降低开关频率将降低功耗;

-

VDD和V5V之间的LDO,能够提供高达20mA的电源。切勿加载V5V到其他负载,电压轨仅用于数字隔离器或光耦合器的偏压

-

VDD和VCH之间的LDO,这是内部电荷泵的一部分

-

内部电荷泵电源开关,可禁用并用外部负偏压替换,如电荷泵—VEE(VEESET)部分所述

系统性能

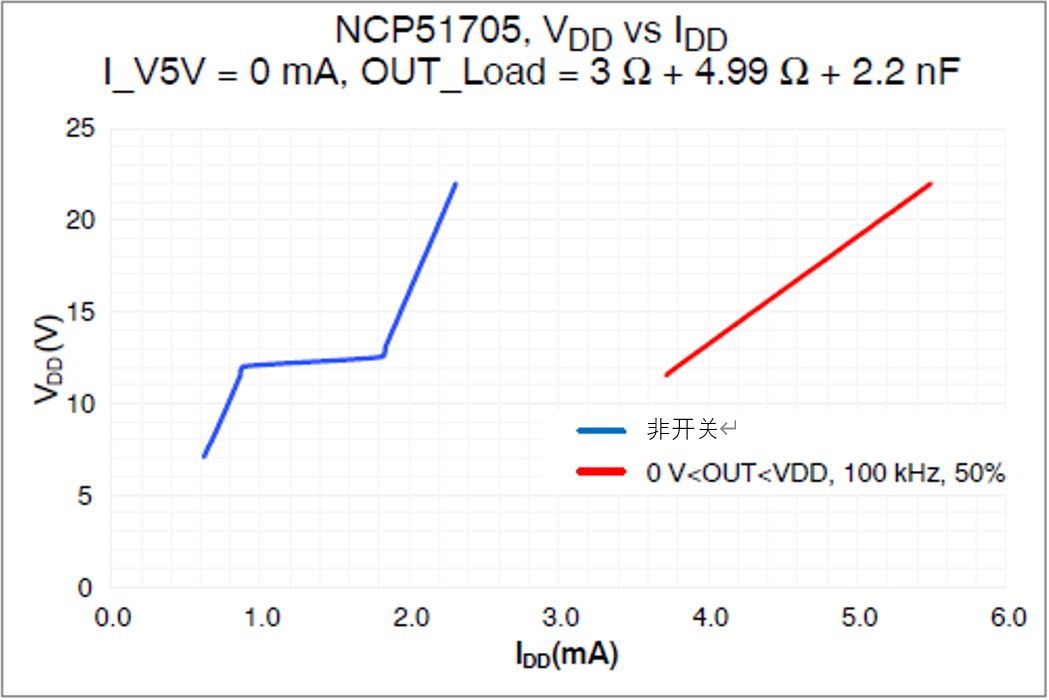

对于VDD>7V,静态电流线性缓升,直至超过设置的UVLO阈值。图16所示的蓝色曲线表示在没有PWM输入信号并且VDD(UVLO)=12V,V5V调节器无负载的情况下,VDD相对于IDD的变化曲线。对于7V

红色曲线表示在禁用内部电荷泵的同时向IN+施加100kHz、50%占空比脉冲输入的情况。使用4.99Ω+2.2nF负载,这是典型SiC MOSFET的等效输入阻抗。外部灌拉电阻为3Ω。对于12V

图16.VDD与IDD,非开关与开关

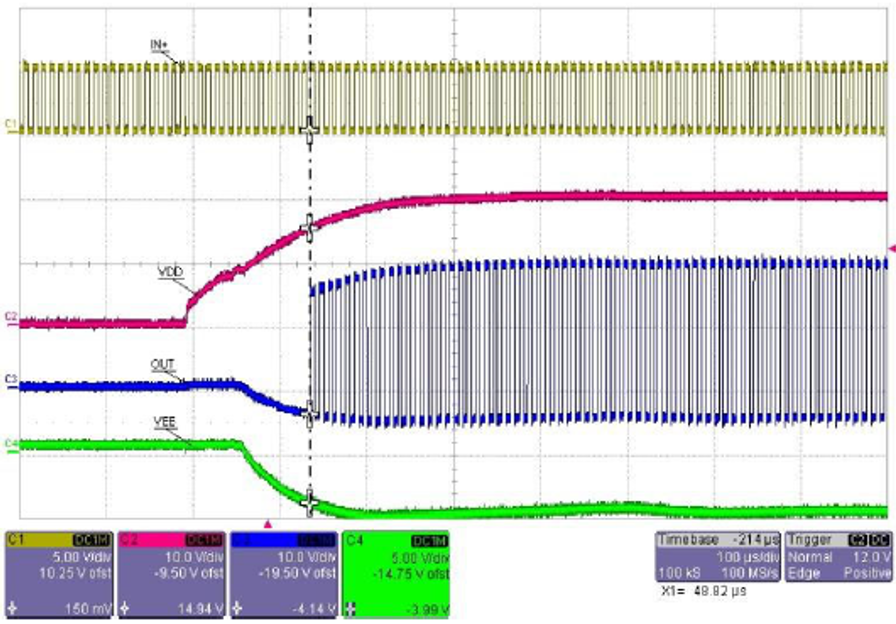

图17所示的启动波形显示了在VDD之前已经输入了PWM信号到IN+。VDD从0V上升至20V,UVSET=2V(未在图中显示),相当于VDD(UVLO)=12V。VEE被设置为在−5V调节,VEESET=V5V(未在图中显示),相当于VEE(UVLO)=−4V。当VEE=−4V时,输出便会使能,此时VDD>12V(VDD=15V)。还要注意,在近100μs的时间内,OUT(VGS)小于20V。根据VDD爬升的dV/dt速率,该时间可能更长,因此,在编程UVSET时应考虑SiC MOSFET的热应力。

图17.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=12V,VEE(UVLO)=-4V

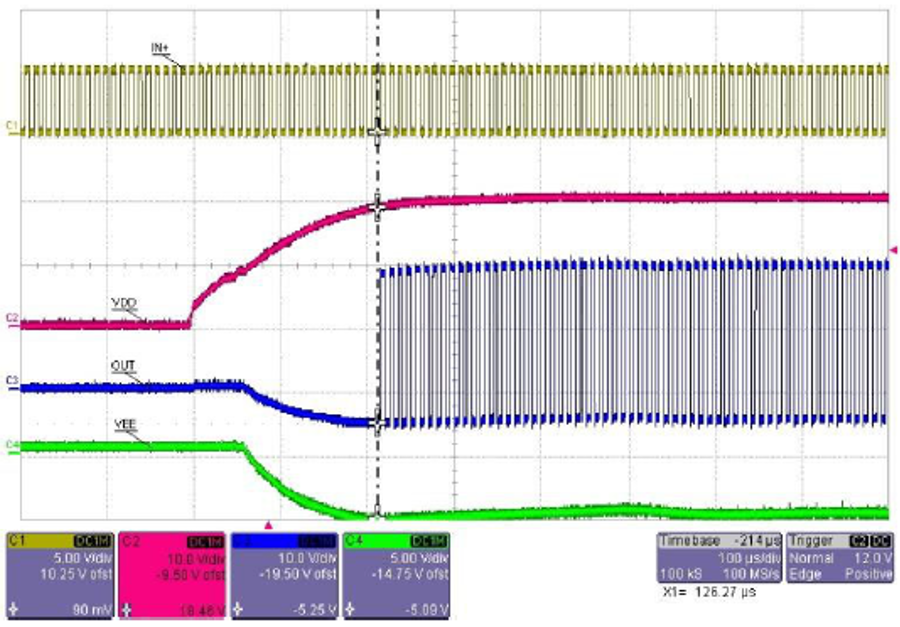

图18中显示了相同的启动波形,但UVSET=3V(未显示),相当于 VDD(UVLO)=18V。在这种情况下,当VDD=18V时,OUT(VGS)便会启用,此时VEE<−4V(VEE=−5V)。哪个UVLO占优势取决于VDD与VEE的dV/dt速率。关键点是NCP51705输出被禁用,直到VDD和VEE都高于或低于各自的UVLO阈值。与图17相比,请注意较高的UVLO设置对 OUT(VGS)的影响,其中第一个OUT脉冲出现在20V和−5V附近。

图18.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

VDD(UVLO)=18V,VEE(UVLO)=-4V

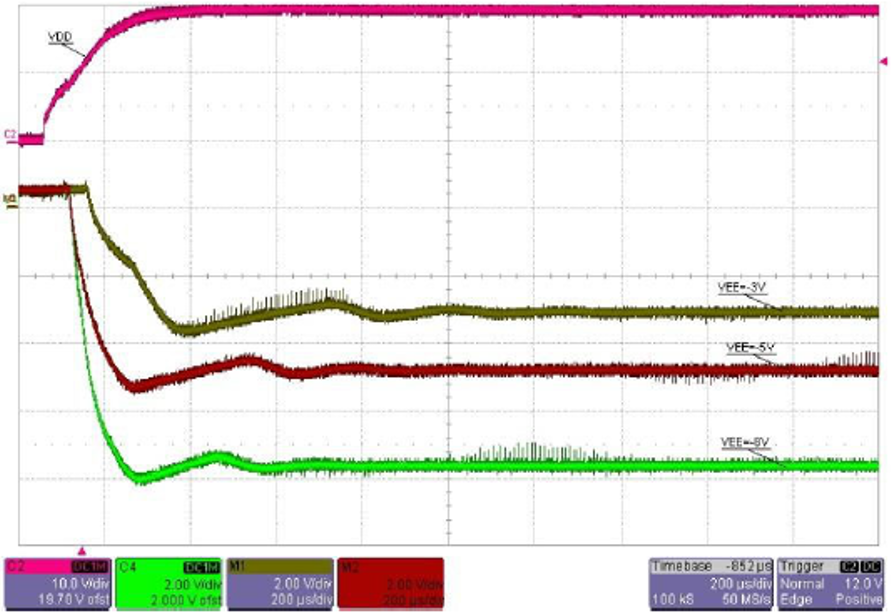

NCP51705内部电荷泵有一个缓慢的控制回路,其效果可从VEE启动期间观察到的轻微下冲和<400μs的稳定时间中看出,如图19所示。超过400μs时,VEE电压稳定至−3V、−5V或−8V的调节设定值。

图19.VEE启动

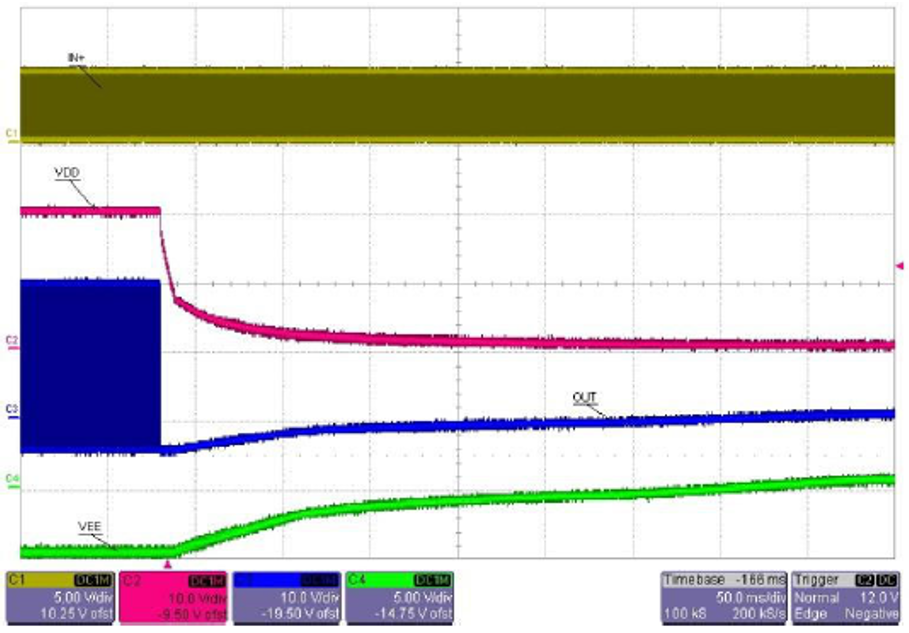

关机操作平稳,无毛刺。如图20所示,OUT停止开关并跟踪掉电的 VEE。VEE从−5V到0V的放电时间约为300ms。

图20.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;关闭

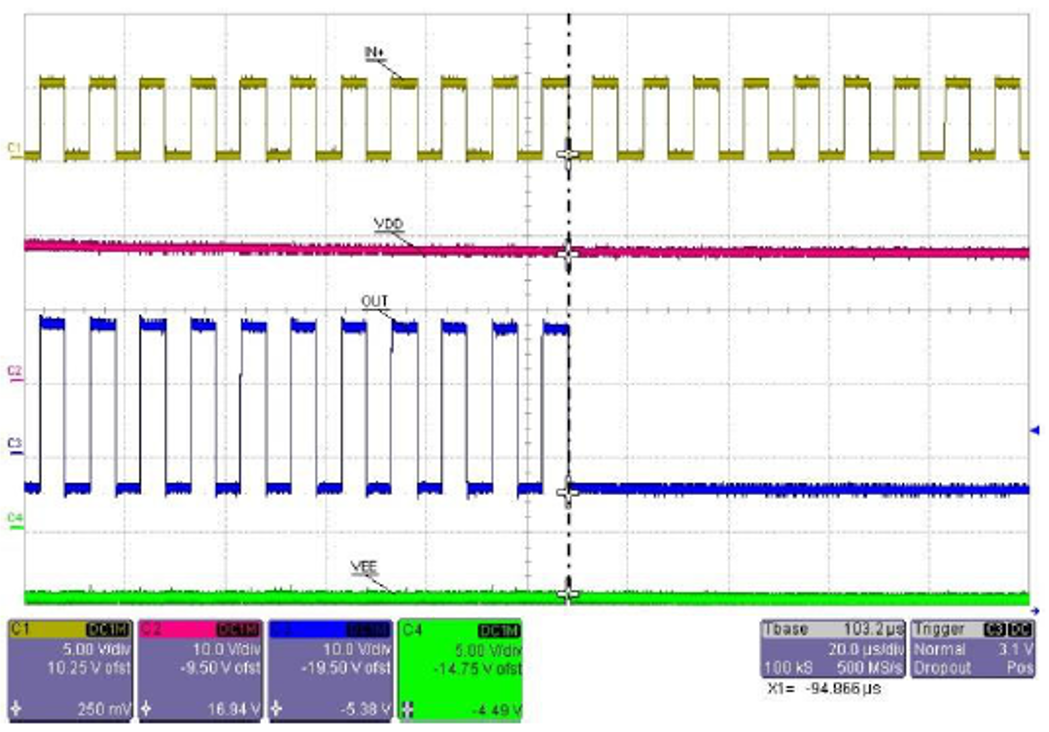

图21显示了图20中时间基准的放大图。UVSET被配置为3V(VDD(UVLO)=18V),内部VDD UVLO迟滞在内部固定为1V。当输出被禁用时,光标位置显示VDD=17V(18V−1V滞后),此时VEE=−4.5V(VEESET=V5V),并且根据其−4V UVLO仍处于有效电压范围。尽管VDD的衰减很慢,但在UVLO_OFF之后,也可以看到最后一个输出脉冲的终止很干净,没有杂散脉冲或毛刺。

图21.CH1-IN+、CH2-VDD、CH3-OUT、CH4-VEE;

关闭,VDD_UVLO(OFF)=17V

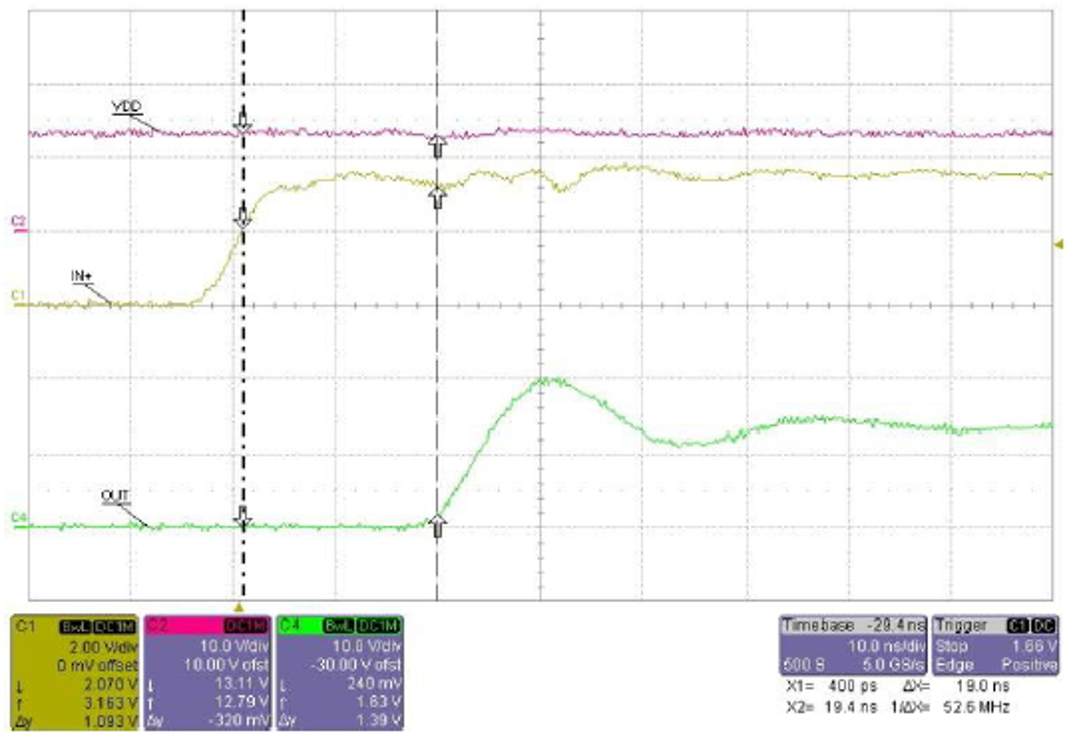

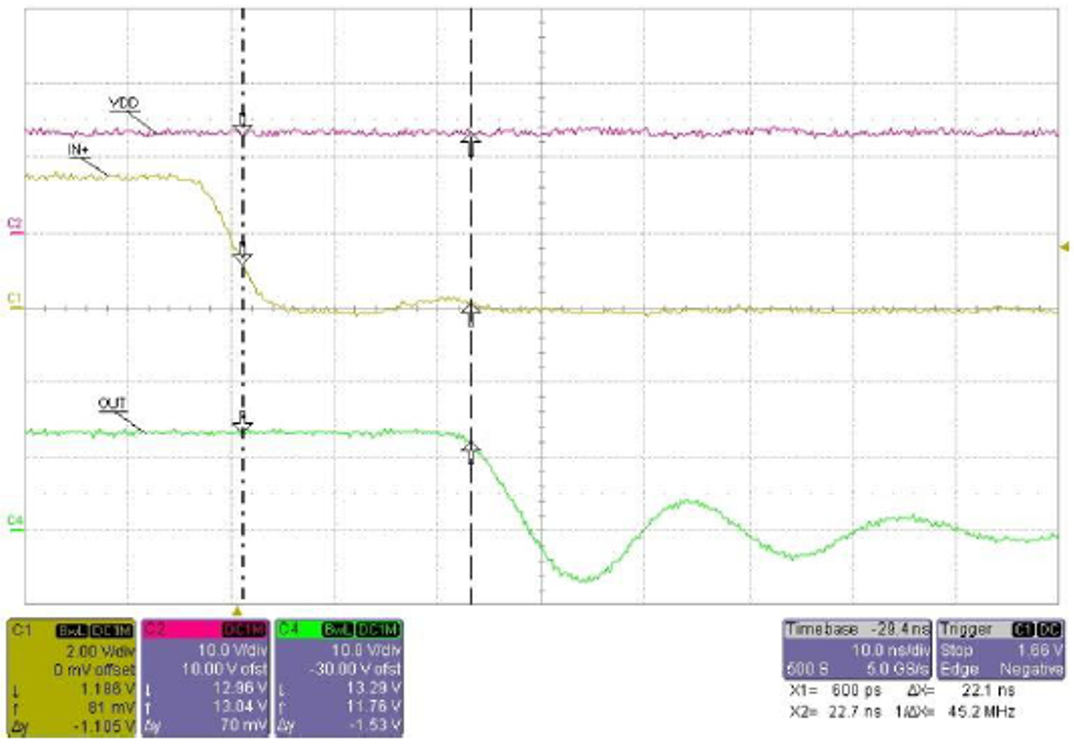

导通传播延迟的测量范围从90%IN+上升至10%OUT上升。通常SiC 驱动器将在更高的VDD下工作,但大多数SiC MOSFET传播延迟被指定为VDD=12V,1nF负载条件下的测得。图22显示了在这些标准测试条件下测得的导通传播延迟为19ns。

图22.CH1-IN+、CH2-VDD、CH4-OUT;上升沿传播延迟

同样,关断传播延迟的测量范围从10%IN+下降至90%OUT下降。图23显示了在相同标准测试条件下测得的关断传播延迟为22ns。每个边缘的输出上升和下降时间约为5ns。

图23.CH1-IN+、CH2-VDD、CH4-OUT;下降沿传播延迟

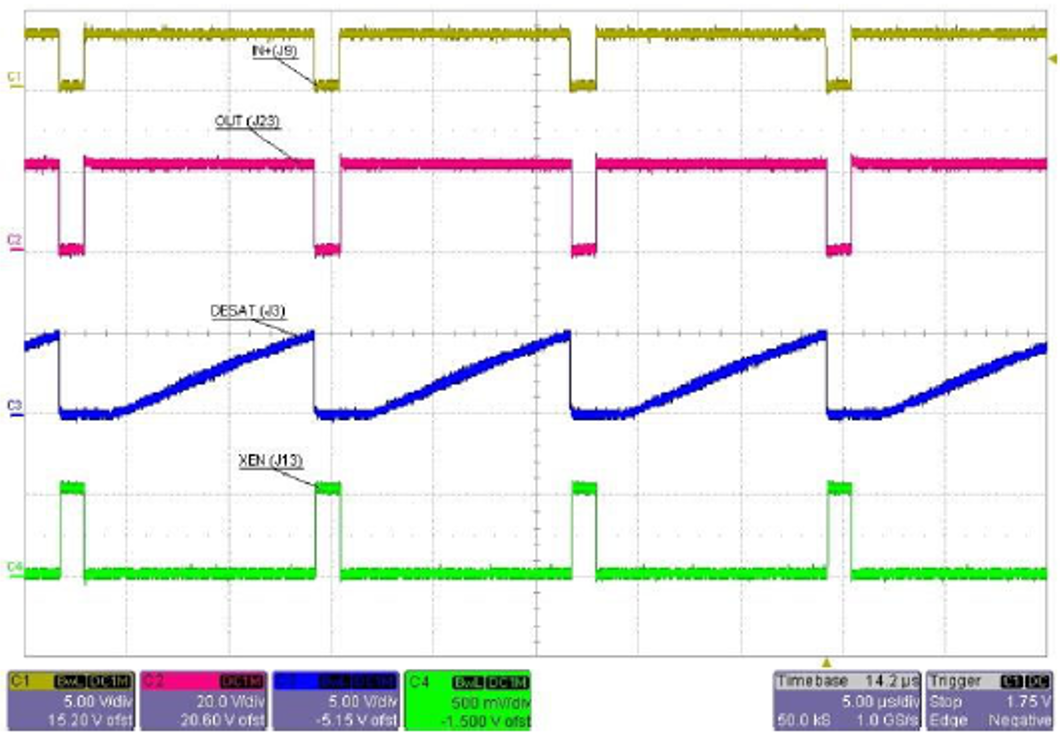

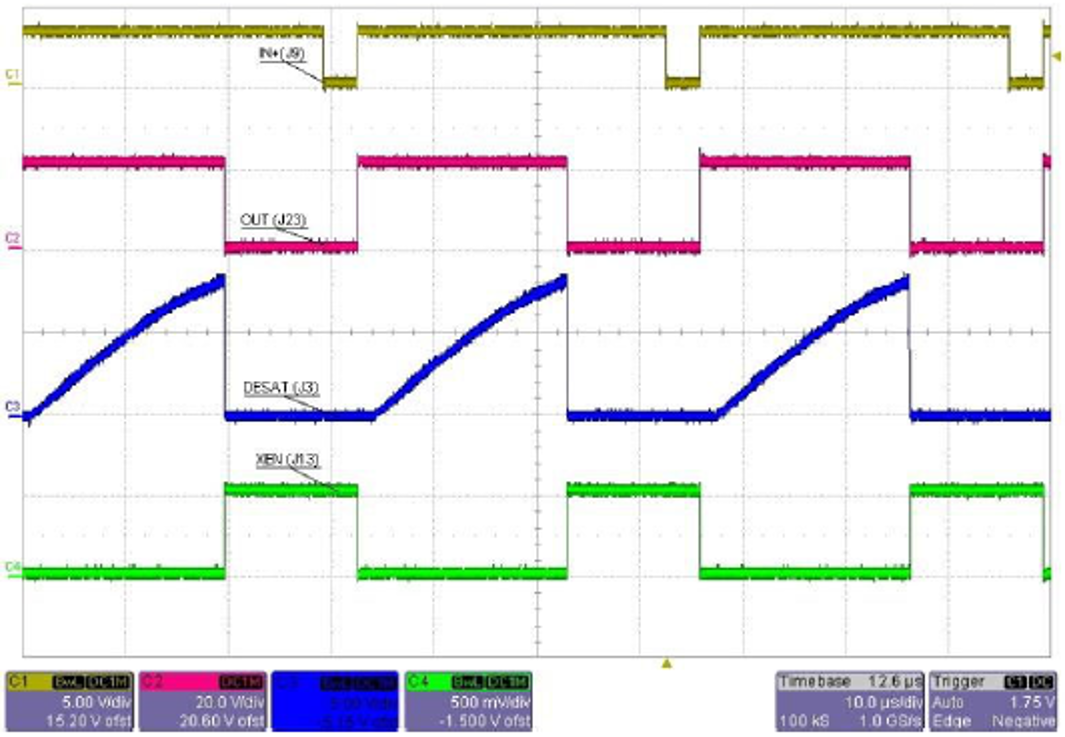

DESAT和XEN波形分别如图24和图25所示。由于测试仅用于IC验证(无功率器件级),因此将100pF固定电容连接到DESAT引脚。图24所示的波形表明DESAT低于7.5V阈值,输出在正常操作下切换。如果IN+频率降低(导通时间增加),则100pF DESAT电容将可以充电至更高的电压。如图25所示,DESAT电压已达到7.5阈值。输出后沿在输入电压切换为低之前终止。DESAT小斜坡用于强调终止的OUT脉冲上没有出现毛刺的事实。在开关电源应用中,DESAT引脚上可以使用小型(<100pF)外部电容进行高频噪声滤波。

XEN信号与OUT信号相反。无论驱动器是正常运行还是面临DESAT故障,XEN信号都能准确跟踪任一情况下的反向OUT信号。

图24.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT<7.5V

图25.CH1-IN+、CH2-OUT、CH3-DESAT、CH4-XEN;VDESAT=7.5V

应用

SiC MOSFET可以适用于目前使用IGBT的各种应用场景。一些较常见的用途包括高压开关电源、混合动力和电动汽车充电器、电气化铁路运输、焊机、激光器、工业设备及其他注重高温操作的环境。尤其值得一提的两个领域是太阳能逆变器和高压数据中心。更高的直流电压有利于减小线规厚度、接线盒、互连,并最终最大限度地减少导通损耗,从而提高效率。目前,大多数大型光伏系统均采用1kV直流母线,未来趋向于采用1.5kV总线。同样,使用380V配电网络的数据中心可以将直流电压提升至800V。

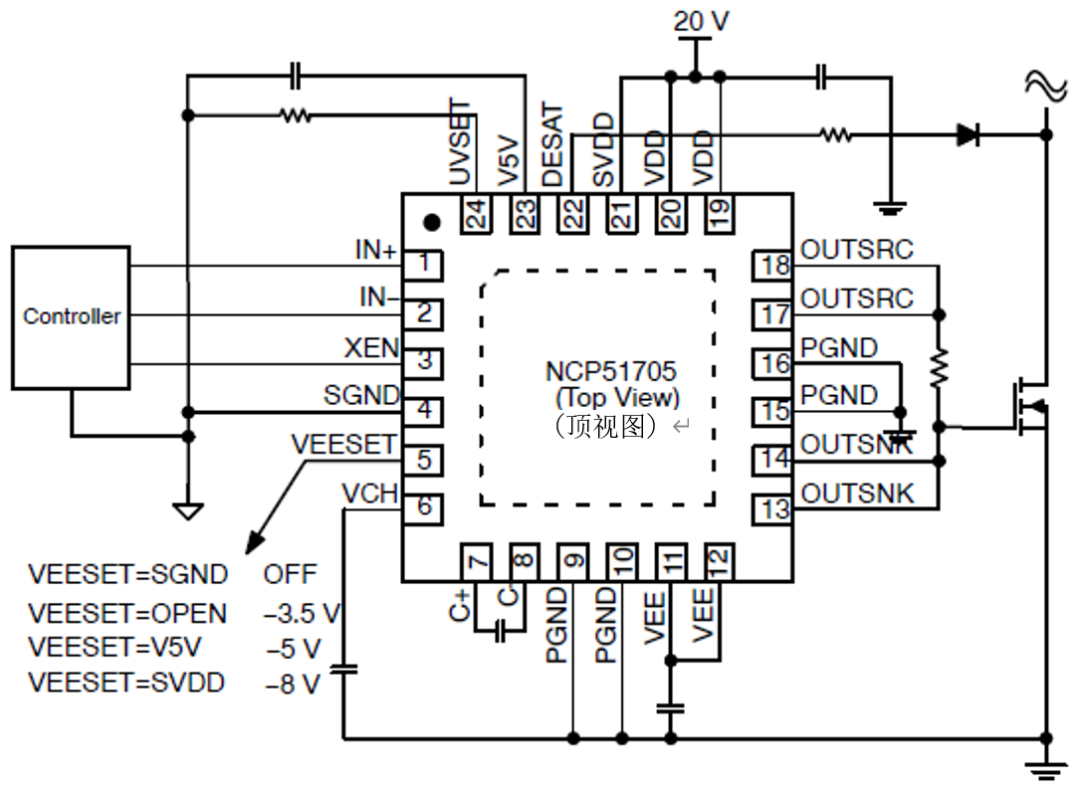

NCP51705的几个基本应用示例如下所示。

低边开关图26显示了用于低边开关应用的NCP51705的顶层原理图。未显示隔离,因此控制器和驱动器之间为直连接口,不是所有应用都是非隔离架构。此原理图旨在说明,要提供全功能、可靠和稳健的SiC栅极驱动电路,只需甚少的外部组件。还应提及,尽管只需要单一VDD电压轨,但其共模瞬态抗扰度额定值应至少为50V/ns,以防止分立式SiC栅极驱动部分中的分立式栅极驱动说明所述的杂散电流脉冲。如果 VDD电压轨由专用辅助电源提供,则应特别注意设计具有超低原-副边 杂散电容的变压器。

图26.低边开关示例

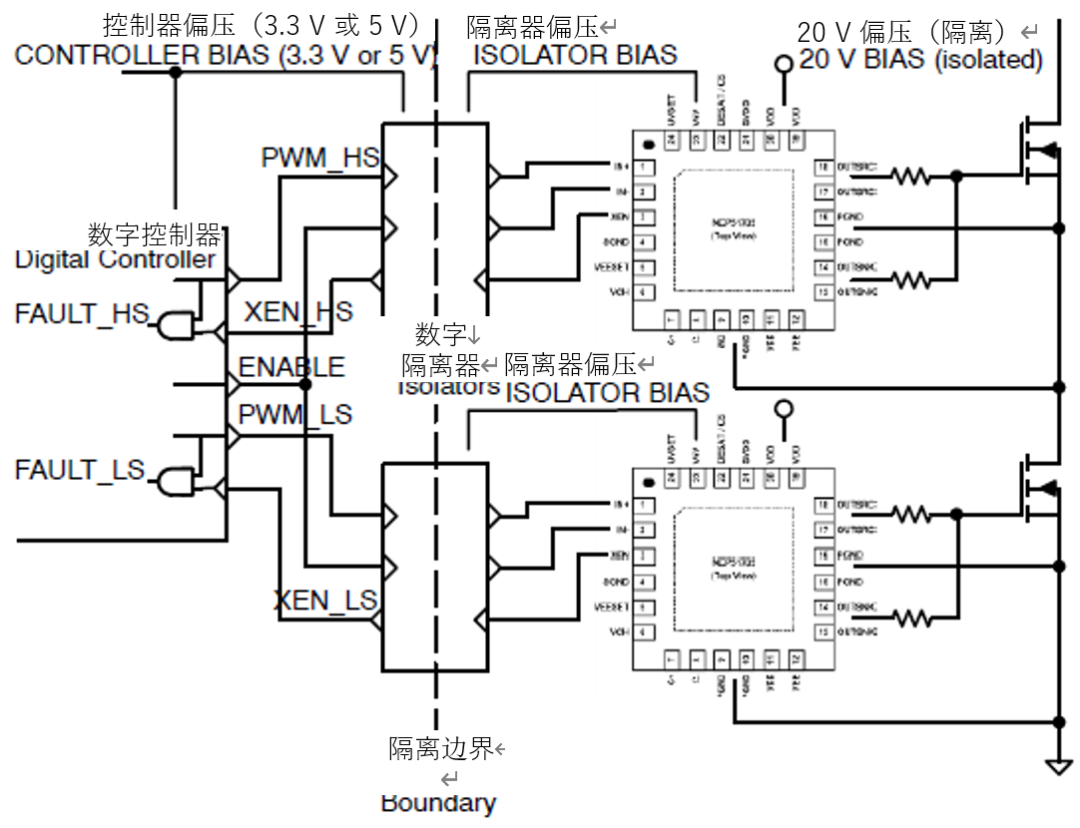

半桥概念

在半桥电源拓扑中可以找到SiC MOSFET更普遍的用途,如图27所示。高功率应用倾向于在高边和低边都使用隔离驱动器。这意味着需要两个数字隔离器。根据跨越隔离边界的IO接口的数量,此类应用的次级侧控制可能存在很大争议。在这个简化示例中,In+和In-(使能)是来自数字控制器的仅有的两个信号,XEN从NCP51705读取。XEN可以作为开发栅极驱动时序、交叉导通预防、死区时间调整和故障检测的时序信息基准。此外,温度感测、热管理(风扇控制)和更高级别的故障响应也可以由数字控制器完成。NCP51705的V5V可用于为每个数字隔离器的次级侧供电,如图27所示。

图27.半桥概念

准谐振(QR)反激式

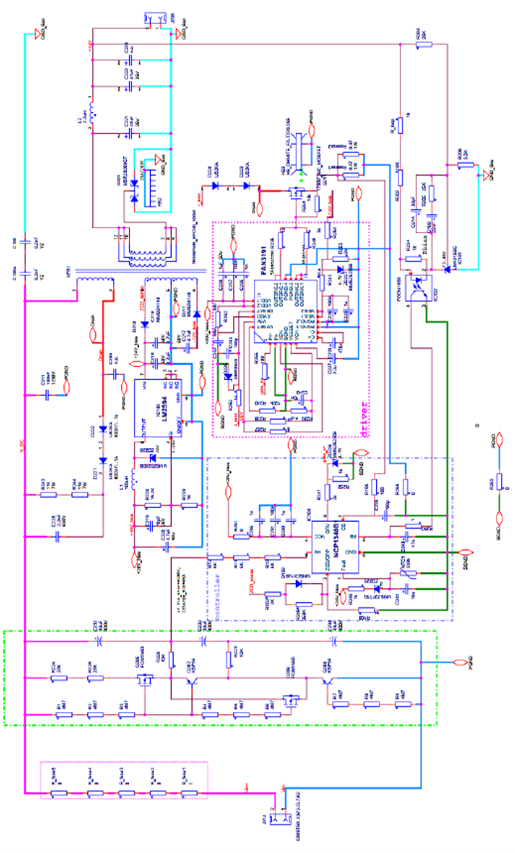

使用NCP1340B1控制器和NCP51705 SiC驱动器设计了一个100W的QR反激式转换器,可在300V

图28.1000V至24V、100W、400kHz、QR反激式

对于VIN=300V,漏极-源极电压波形是输入电压和反射输出电压之和。图29所示的波形突出显示了在全占空比操作(VIN=300V)下运行的转换器,其中SiC MOSFET的漏极-源极电压为720V。VDS上升过渡约为30ns,相当于dVDS/dt=24V/ns。NCP1340B1 QR控制在VDS下降沿实现软谐振过渡和谷底开关(在VDS谐振到最小值时“接近 ZVS”导通),可以在蓝色波形上清晰看到这一操作过程。由于QR反激式是仅限低边开关的应用,并且dVDS/dt下降沿为谐振,因此SiC MOSFET可能在0V

图29.CH3=VDS,CH4=VGS;VIN=300V,VOUT=24V,

IOUT=4A,FS=377kHz

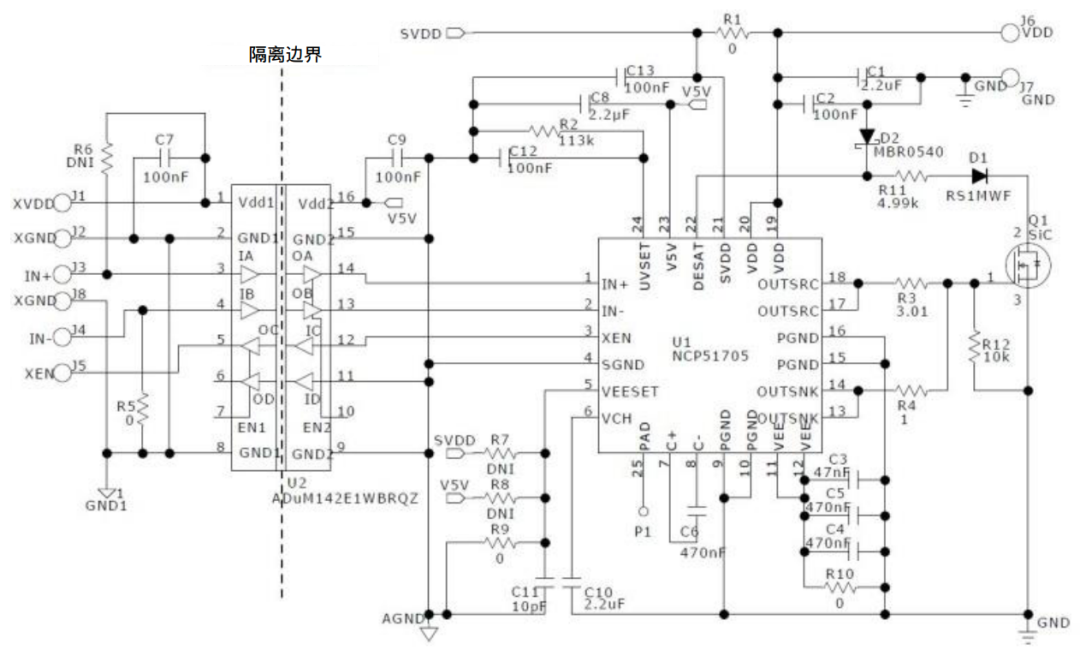

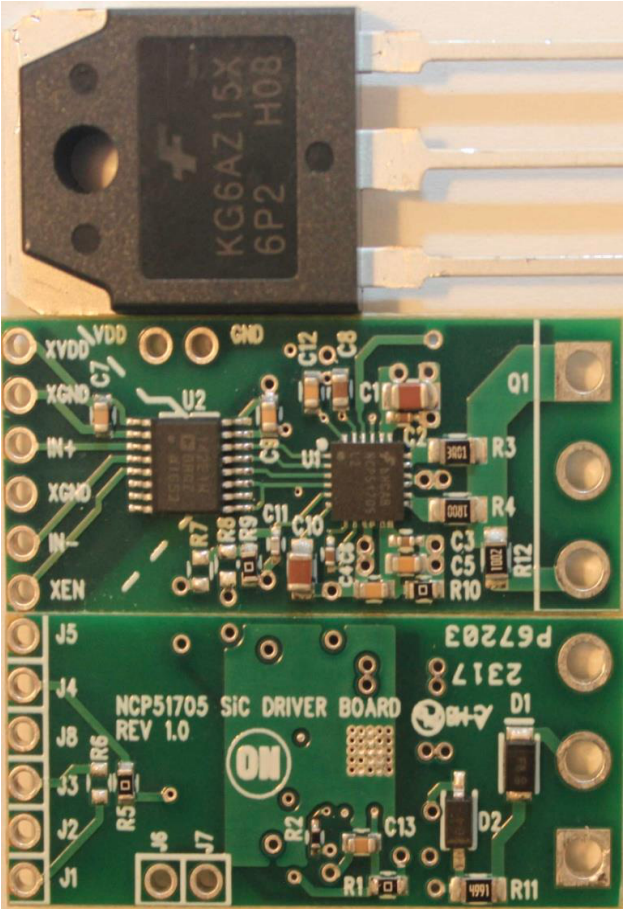

通用NCP51705客户EVB通用评估板(EVB)旨在评估NCP51705在新设计或现有设计中的性能。EVB不包括功率级,不专用于任何特定拓扑,由此可见它是通用的。它可用于任何低边或高边电源开关应用。对于桥接配置,可以用两个或者多个EVB组成图腾柱结构来驱动每个SiC MOSFET。EVB可被视为隔离器+驱动器+TO-247分立模块。EVB原理图如图30所示。

重点是提供一种超紧凑的设计,其中TO-247 SiC MOSFET的引线可以直接连接到印刷电路板(PCB)。图31同时显示了相邻TO-247封装旁边的EVB的顶视图和底视图进行尺寸缩放。

图30.NCP51705 Mini EVB原理图

图31.NCP51705 Mini EVB-顶视图(35mmx15mm)

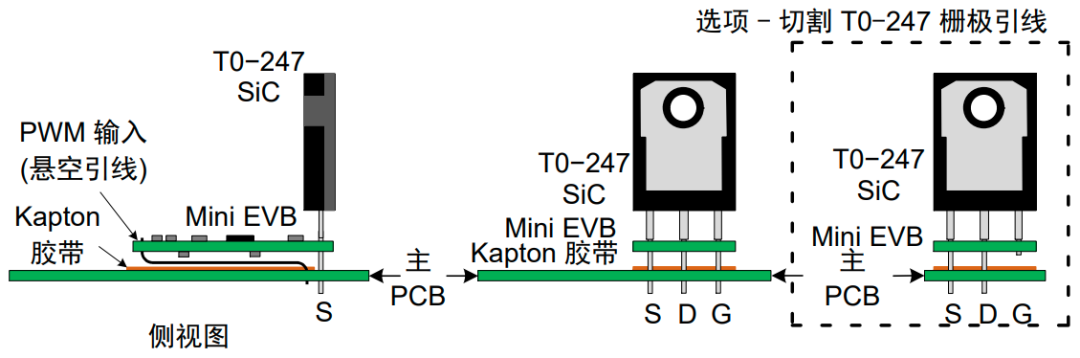

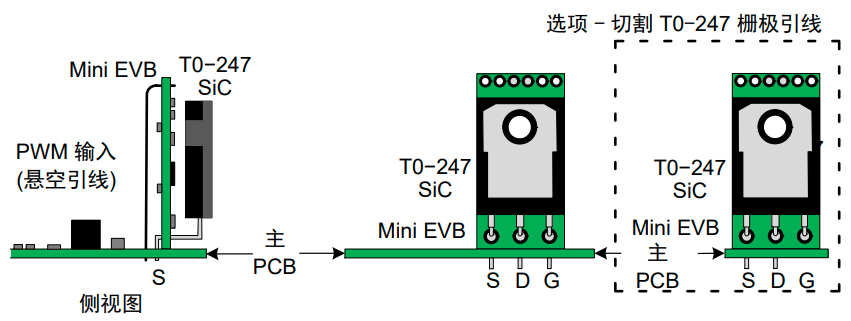

当安装到现有电源设计中,并且TO-247前面有可用的PCB区域时,EVB可以水平安装到主电源板上,如图32所示。如果可能,这应该是首选的安装方法。

图32.水平EVB安装

如果主电源板上的大型组件妨碍水平安装,则第二种选择是垂直安装EVB,使其与T0-247封装平行或略微倾斜。由于驱动器与TO-247漏极接头发出的高dV/dt非常接近,因此不太倾向于采用这种方式安装。在任何一种情况下,TO-247封装的后接头都保持暴露状态,如有必要,可将其连接到散热片上。有关安装和操作详细信息,请参见EVB用户指南。

图33.垂直EVB安装

EVB最初配置为接受正输入逻辑的PWM信号(连接到GND1的 IN-)。但如果需要,IN-可轻松用作主动启用或重新配置为反相输入逻辑。驱动器输出预配置为0V

参数性能

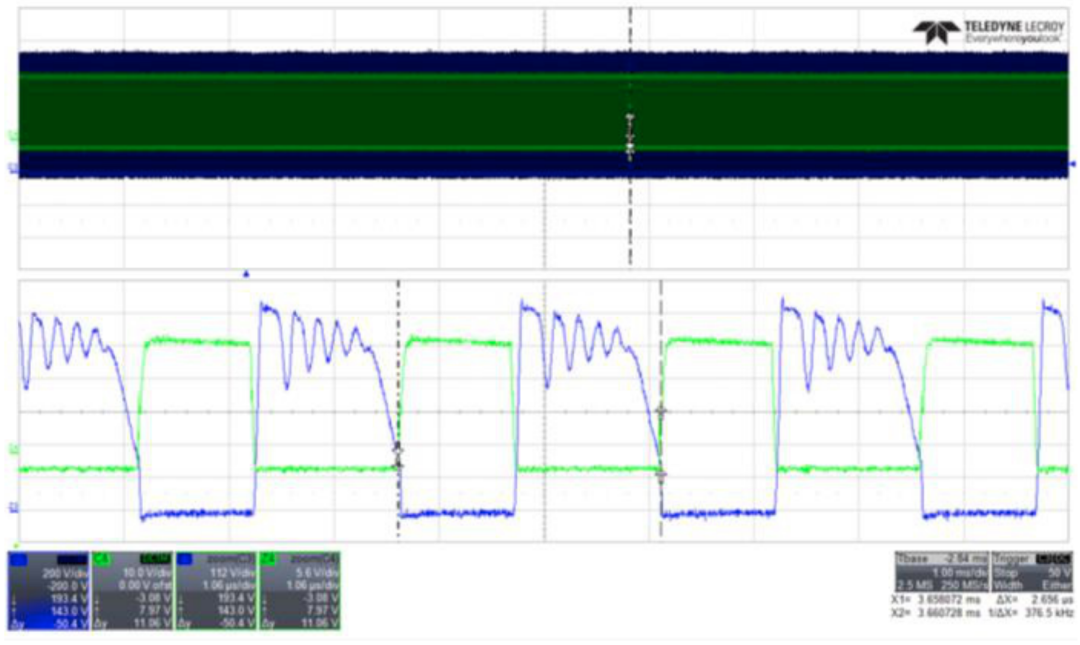

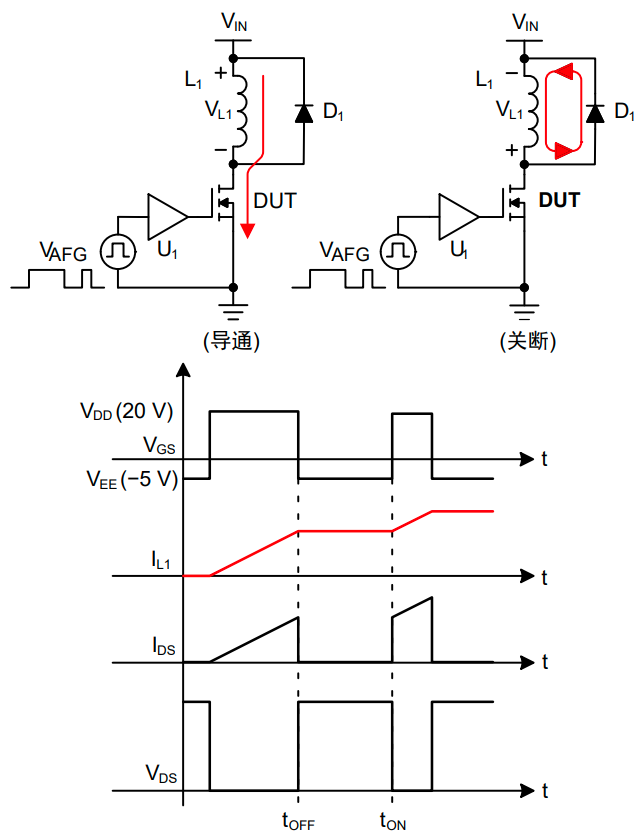

使用众所周知的双脉冲测试平台对MOSFET和IGBT进行参数化表征。双脉冲测试方法基本会向被测器件(DUT)低边SiC MOSFET的栅极-源极施加两个脉冲。DUT被插入到与图34所示的钳位电感开关电路相连的插座中。

图34.双脉冲测试电路和波形

调整第一个脉冲的导通时间,以获得所需的峰值漏极-源极电流。电感器很大,关断时间足够短,因此IL1在关断续流期间几乎保持恒定。因此,第二个更短的脉冲以相同的漏极-源极电流幅度施加。该测试方法可精确控制ID和VDS,这是建立动态开关、参数性能以及对器件进行对比测试所必需的。

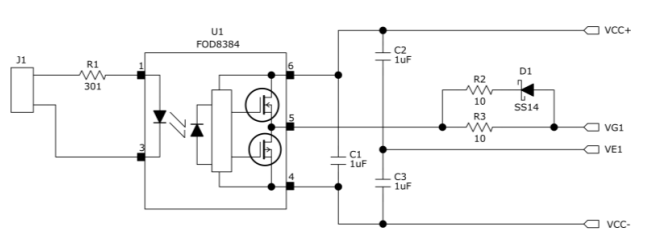

双脉冲测试方法也可用于表征栅极驱动器性能。在SiC、DUT固定的情况下,可以有各种栅极驱动电路组成U1成为新的“DUT”。在图30和图31所示的NCP51705 EVB和图35所示的简单光耦合器栅极驱动电路之间,对dV/dt和dI/dt开关性能进行了比较。

图35.FOD8384 SiC光耦合器栅极驱动电路

FOD8384光耦合器驱动器能够承受高达30V的VDD偏压,因此非常适合-5V

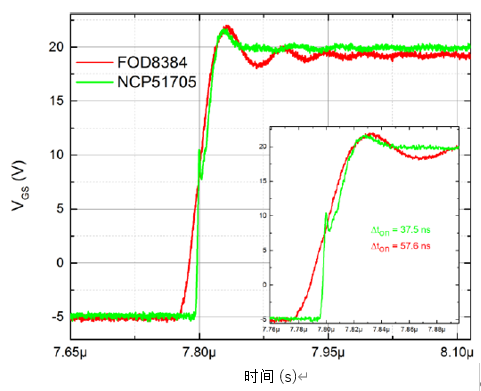

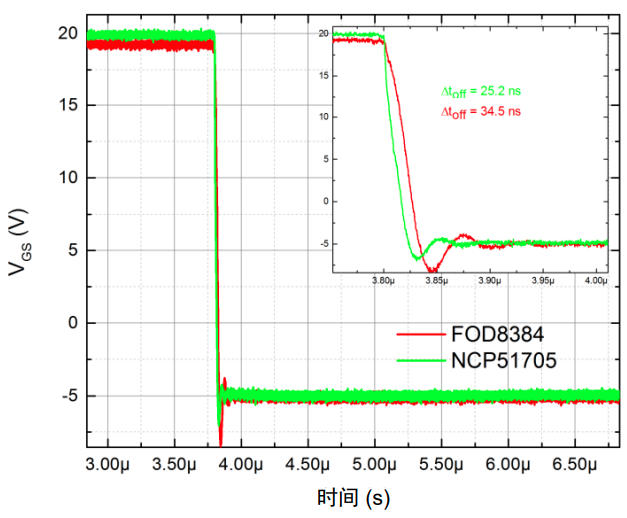

图36和图37分别显示了两种电路的上升和下降VGS波形,以供比较。两种电路都使用了1Ω的灌和拉电阻。这些栅极驱动边缘被显示为驱动1.2kV的SiC MOSFET,VDS上电压为600V,流过ID的电流为30A。NCP51705、VGS上升沿在−5V

图36.VGS上升沿比较

图37.VGS下降沿比较

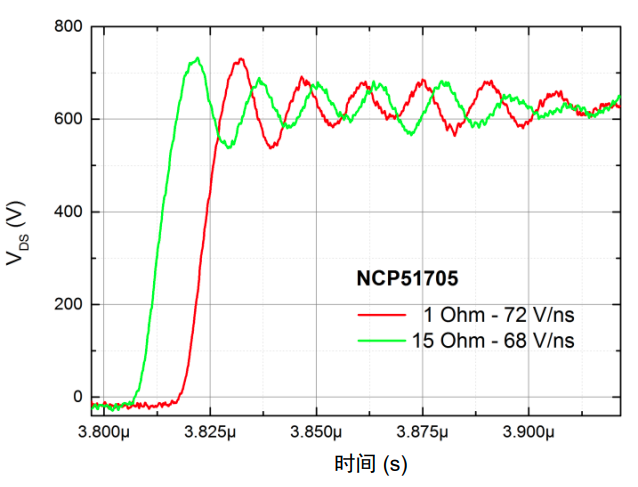

设计良好的栅极驱动器IC包括低源极和漏极阻抗,使得SiC MOSFET漏极可以由栅极精确控制。其次,最大限度地降低驱动器输出阻抗对于允许SiC MOSFET达到最高自然dV/dt至关重要。SiC MOSFET的自然dV/dt限值与RLO+RGATE+RGI成反比。当RLO高于必要值时,SiC MOSFET的自然dV/dt限值降低。这使得器件更容易受到dV/dt引起的导通的影响,并限制了通过选择RGATE可以实现的dVDS/dt控制量。图38所示的NCP51705 VDS波形揭示了改变RGATE即可实现的高度dVDS/dt控制。对于RGATE=1Ω,dVDS/dt=72V/ns。将RGATE从1Ω增加到15Ω会使dVDS/dt从72V/ns降低到68V/ns。这表明,如果需要,可以使用高得多的RGATE来逐步降低dVDS/dt。

图38.NCP51705 VDS上升沿,可变栅极电阻

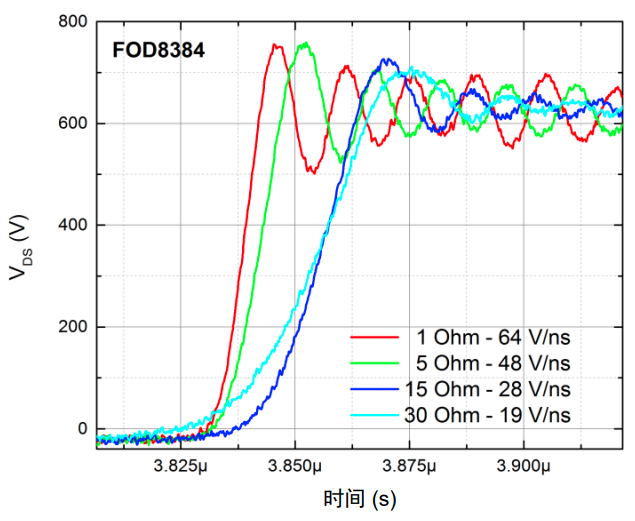

使用FOD8384光耦合器栅极驱动器完成了相同的实验。从图39所示的波形中发现,RGATE从1Ω变成15Ω导致dVDS/dt速率变化超过2:1。由于FOD8384驱动器输出阻抗更高,dVDS/dt控制更受RGATE较小变化的影响。此外请注意,NCP51705的dVDS/dt上升相对而言更为线性。

图39.FOD8384 VDS上升沿,可变栅极电阻

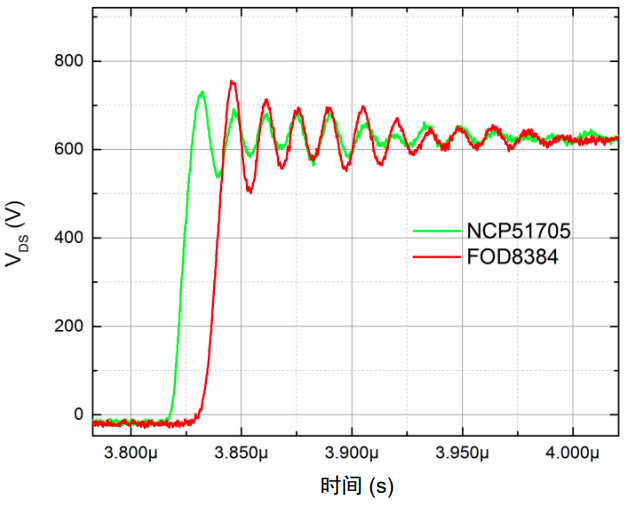

图40所示的波形比较了在RGATE=1Ω的情况下,从−5V

图40.VDS上升沿比较,1Ω栅极电阻

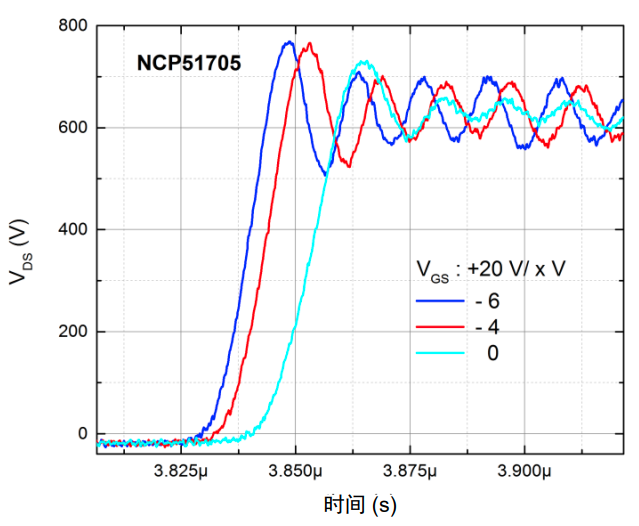

NCP51705实现dVDS/dt控制的另一种方式是通过改变VEE的负振幅电平。这可以通过根据表3配置VEESET引脚或使用施加到VEE的外部负 DC 电源来实现。图 41 中的波形显示了当VEE在−6V

图41.NCP51705 VDS上升沿,可变VEE

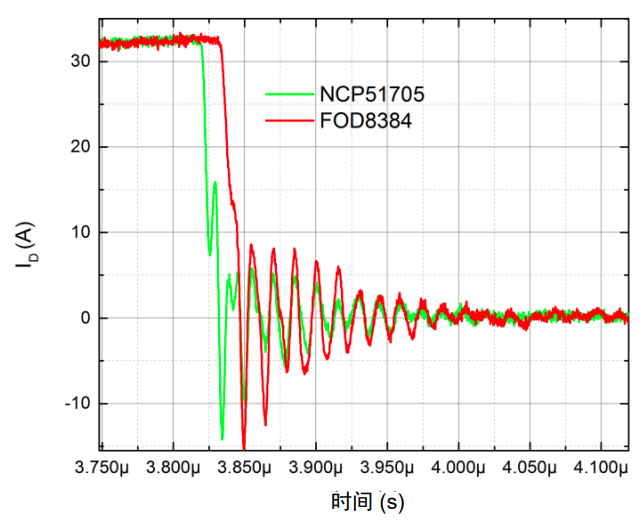

图42所示的漏极电流测量是使用Pearson电流探头进行的。NCP51705电流在dID/dt=3.2A/ns时下降,但与FOD8384驱动电路相比,表现出的振铃较少。NCP51705更快的dID/dt与图37所示的VGS下降沿波形密切相关。

图42.ID下降沿比较

双脉冲测试方法是传统上用于表征分立功率半导体器件的动态开关性能的测试程序。由于在导通和关断期间可以精确控制施加的VDS和初始ID,该测量技术已被证明是表征箝位电感开关应用电路中栅极驱动器IC性能的可靠方法。

结论

本文重点介绍了在设计高性能栅极驱动电路时必须考虑的SiC MOSFET的一些特性。对于栅极驱动来说,与SiC MOSFET相关的低gm或不那么大的跨导 特性尤其棘手。通用低边栅极驱动器经常被使用,但缺乏高效可靠地驱动SiC MOSFET的必要功能。SiC MOSFET 在市场中的广泛采用在某种程度上与其易用性有关。NCP51705为设计人员提供了一种简单、高性能、高速的解决方案,用于高效可靠地驱动SiC MOSFET。

点个星标,茫茫人海也能一眼看到我

原文标题:SiC MOSFET的封装、系统性能和应用

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

-

安森美

+关注

关注

32文章

1682浏览量

92008

原文标题:SiC MOSFET的封装、系统性能和应用

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

瞻芯电子推出采用TC3Pak封装的1200V SiC MOSFET

PCIe延迟对系统性能的影响

SiC MOSFET模块封装技术及驱动设计

SiC MOSFET和SiC SBD的区别

威兆半导体发布新一代高性能SiC MOSFET

SemiQ 1200V SiC MOSFET Module说明介绍

碳化硅模块(SiC模块/MODULE)大电流下的驱动器研究

如何更好地驱动SiC MOSFET器件?

基于NX封装的低杂感SiC MOSFET模块设计

SiC MOSFET短路失效的两种典型现象

沟槽当道,平面型SiC MOSFET尚能饭否?

水下航行器电机的SiC MOSFET逆变器设计

SiC MOSFET的封装、系统性能和应用

SiC MOSFET的封装、系统性能和应用

评论