前言

数字IC设计中为什么要避免锁存器(Latches)?

上学时,老师说判断语句要把条件写全, 不然会生成锁存器,做项目时又说多比特寄存器信号的赋值一定要加if条件,不让出现else的赋值 。就很矛盾,本文主要讲下什么是锁存器,什么情况下会出现锁存器,以及锁存器的危害。

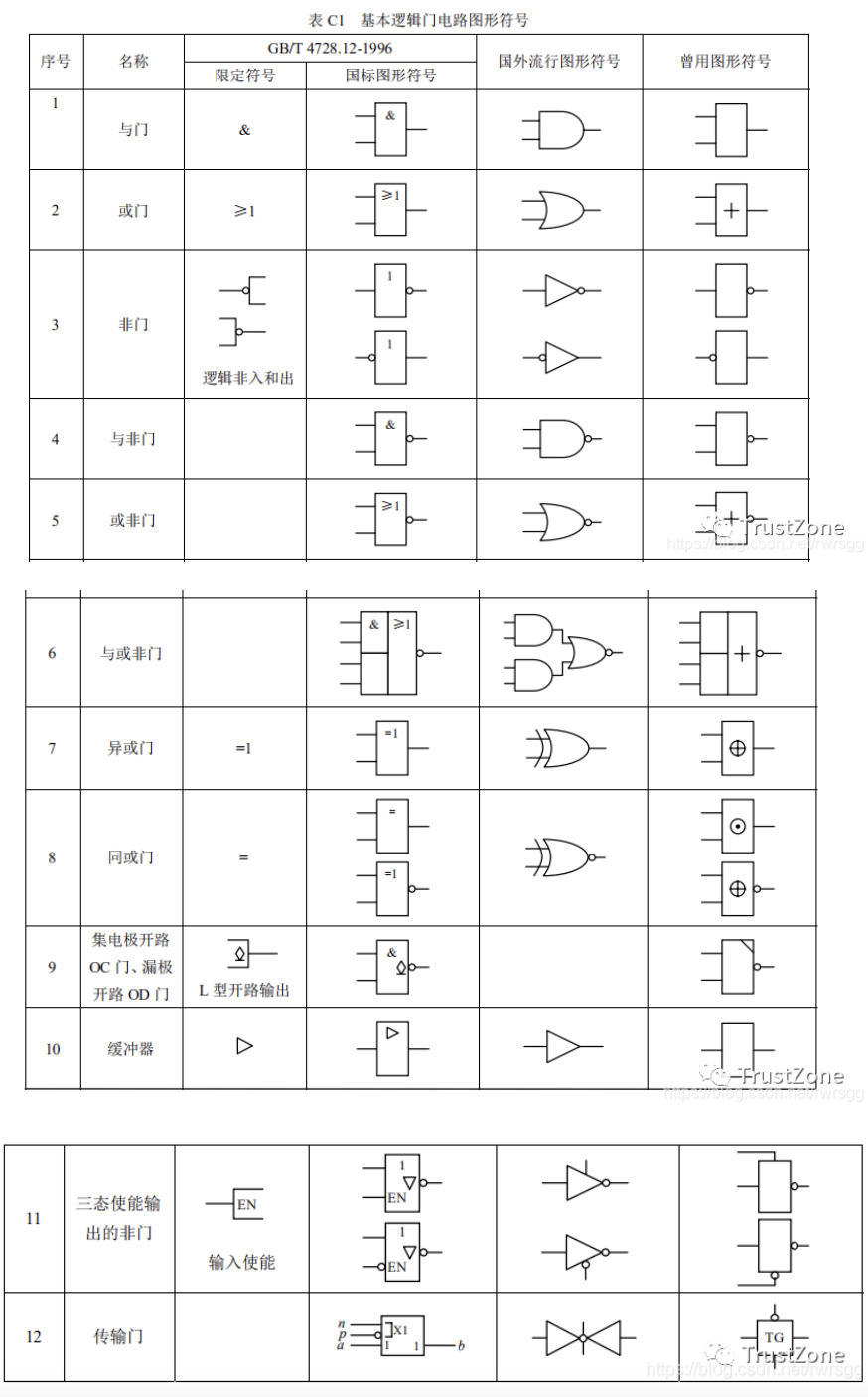

基本逻辑门电路图形符号

零、锁存器,D触发器和寄存器的关系与区别

前言

数字IC设计里,常会出现锁存器,D触发器和寄存器,很多人(比如我)老傻傻分不清,搞不懂他们的区别是什么。这篇博客主要解释锁存器,D触发器和寄存器的工作原理以及他们的关系和区别。

一、锁存器

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态【1】。换句话说,如果一个模块的只有在特定电平的作用下,才会将输入信息更新到他的输出引脚,否则该模块的输出将保持不变,那么这个模块就可以被看成是一个锁存器。

举个例子:

二、锁存器构建D触发器

如图是一个D触发器的示意图,当CLK输入一个上升沿时,D端的输入被传输到Q。而CLK未输入上升沿时,Q保持不变。

如图所示,当CLK = 0时,Q1=D;当CLK=1时,Q=Q1;也就是说,当CLK上升沿来临时,D信号被传输到Q端,因此这两个锁存器组成了一个D触发器;

三、什么是寄存器?

寄存器,是集成电路中非常重要的一种存储单元,通常由触发器组成 , 寄存器是有限存贮容量的高速存贮部件 ,它们可用来暂存指令、数据和地址【2】。也就是说, 拥有缓存数据功能的,都可以被称为寄存器 ,而寄存器常被用于CPU中,因此属于边沿信号敏感器件。

D触发器具有缓存数据的功能 ,当CLK输入上升沿时,D被传输到Q,之后Q将在CLK下一个上升沿到来前保持不变。因此D触发器可以作为寄存器使用,即(D触发器∈寄存器),锁存器状态的变化和特定电平有关(高电平和低电平),而寄存器的状态变化往往需要边沿信号(上升沿和下降沿),因此锁存器notin寄存器,由于两个锁存器可以构建一个边沿信号敏感的触发器(如上节所示),因此锁存器可以搭建寄存器。

四、总结

- 锁存器为电平敏感器件,而D触发器和寄存器为边沿信号敏感器件;

- 两个锁存器可以搭建一个D触发器;

- D触发器属于寄存器;

一、什么是锁存器?

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路 ,它们可以在特定输入脉冲电平作用下改变状态【1】。

换句话说, 如果一个模块的只有在特定电平的作用下,才会将输入信息更新到他的输出引脚 ,否则该模块的输出将保持不变,那么这个模块就可以被看成是一个锁存器。

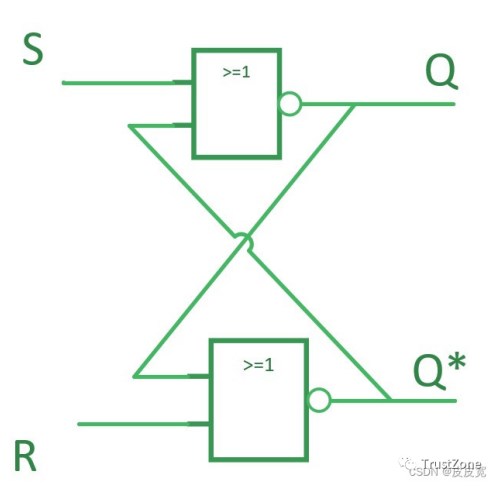

常见的S-R寄存器的结构如下所示:

真值表为

由于S,R为00时,可以使输出Q保持不变,从而达到用组合逻辑来实现存储的目的;

二、什么情况下会出现锁存器?

时序逻辑由于寄存器的存在 ,因此不需要锁存器来存储数据; 而组合逻辑的条件未给全时则会出现锁存器 ;

always@(*) if(vld) a = b;

这时由于没有写vld为0的情况,因此不会例化成二选一的选择器,而是会例化出锁存器,达到当vld为0时,保持数据不变的存储功能;

三、为什么要避免出现锁存器?

锁存器有以下缺点:

- 不能异步复位,在上电后处于不确定的状态。

- 锁存器会使静态时序分析变得非常复杂;

- 如果是FPGA上的搭建电路的话,由于FPGA中基本的单元是由查找表和触发器组成的,若生成锁存器反而需要更多的资源;

- 锁存器对毛刺敏感,会造成电路的不稳定

例化成选择器就能解决这个问题吗?

-

FPGA

+关注

关注

1631文章

21806浏览量

606681 -

IC设计

+关注

关注

38文章

1302浏览量

104354 -

锁存器

+关注

关注

8文章

915浏览量

41682 -

D触发器

+关注

关注

3文章

164浏览量

48068 -

CLK

+关注

关注

0文章

127浏览量

17247

发布评论请先 登录

相关推荐

数字IC设计中为什么要避免锁存器呢?

数字IC设计中为什么要避免锁存器呢?

评论