作为一个资深的FPGA工作者,相信大家对于IBIS模型并不陌生;IBIS模型在进行系统设计时节省时间和降低成本是很关键的。在原型制作之前,系统设计人员可以用模型来进行设计仿真。在高速系统设计中正是如此,进行信号完整性仿真来分析不同条件下传输线中的电路行为,在设计初期就能预防并检测出典型的问题,例如过冲、欠冲、阻抗不匹配、串扰、地弹等。然而,可用的数字IC模型非常少。

当半导体厂商被索要SPICE模型时,他们并不愿意提供,因为这些模型会包含有专有工艺和电路信息。这个问题已经通过采用IBIS模型来(输入/输出缓冲器信息规范)解决。IBIS是一个行为模型,通过V/I和V/T数据,描述器件数字输入和输出的电气特性,而不会泄露任何元器件专有的信息。

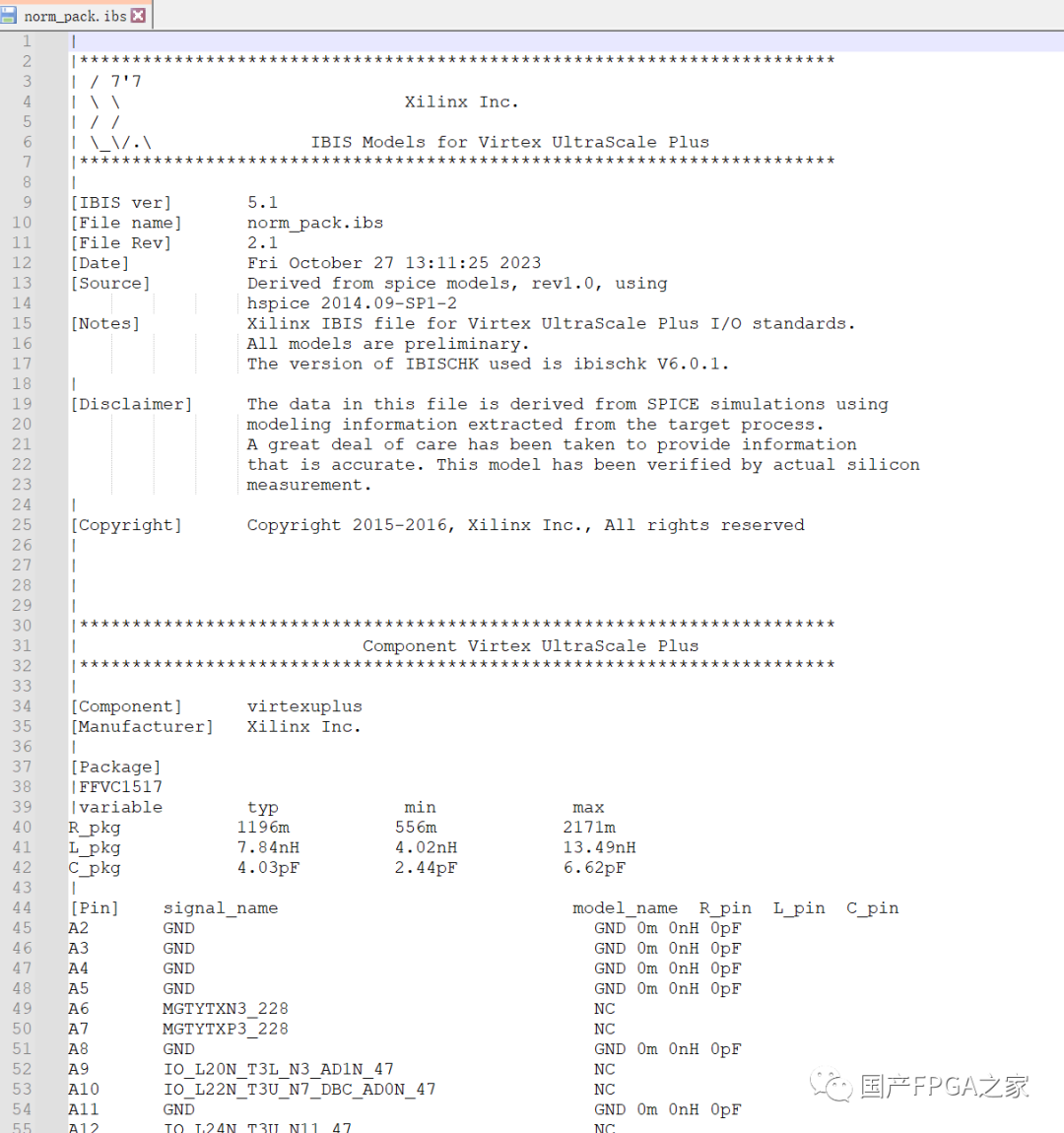

FPGA器件作为高灵活度器件,其管脚属性可以根据用户需求自行设定。FPGA厂商提供一般提供通用IBIS模型,通用IBIS模型文件包含所选系列支持的所有IO标准的模型,模型与具体的芯片封装以及die的尺寸无关,通常这类模型为每个可用的IO设置一个全局RLC参数。在进行少数几个信号的原理图级仿真中,该类IBIS模型是满足需求的,但是在更进一步的PCB仿真中,需要导出自定义的IBIS模型库。 然而在通用IBIS模型中,管脚不是实际封装使用管脚,无法直接使用。

今天我们主要来介绍基于Vivado如何导出FPGA的IBIS文件。

1 IBIS文件生成方法 定义管脚的IBIS文件生成有两种方法。 1)在通用IBIS文件基础上进行编辑。该方法需要一定的IBIS语法基础,需要更新IBIS文件中[Package]、[Pin]、[Diff Pin]、[Model Selector]字段内容。具体操作方法大家可以参考下面博文内容。

Xilinx FPGA IBIS 模型的使用问题,总结+分析都在这里了~ (qq.com)

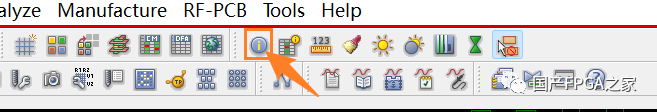

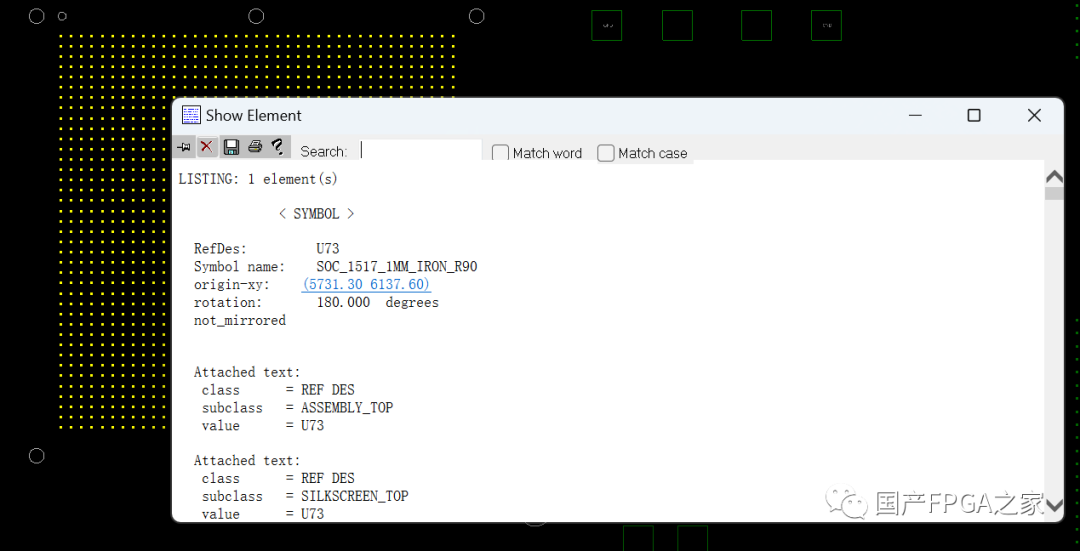

2)通过厂商提供软件自动生成。本篇主要介绍通过vivado 自动生成IBIS软件过程。该方法需要根据管脚与网络映射关系编写XDC文件,涉及4种语法约束。个人感觉更适宜仿真环境快速搭建,此外软件中有DRC分析工具,可以帮助检查芯片原理图设计缺陷。 2 Allegro导出管脚映射关系 本操作从PCB文件中获得FPGA的管脚映射关系。 打开已经导入网表的brd文件,在快捷栏中点击Show Element 快捷键。

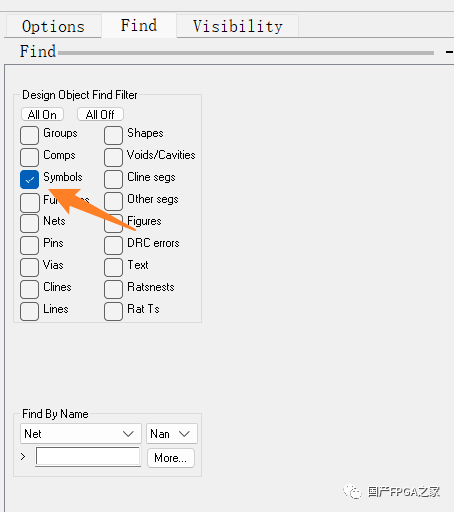

在find 菜单栏中仅勾选Symbols

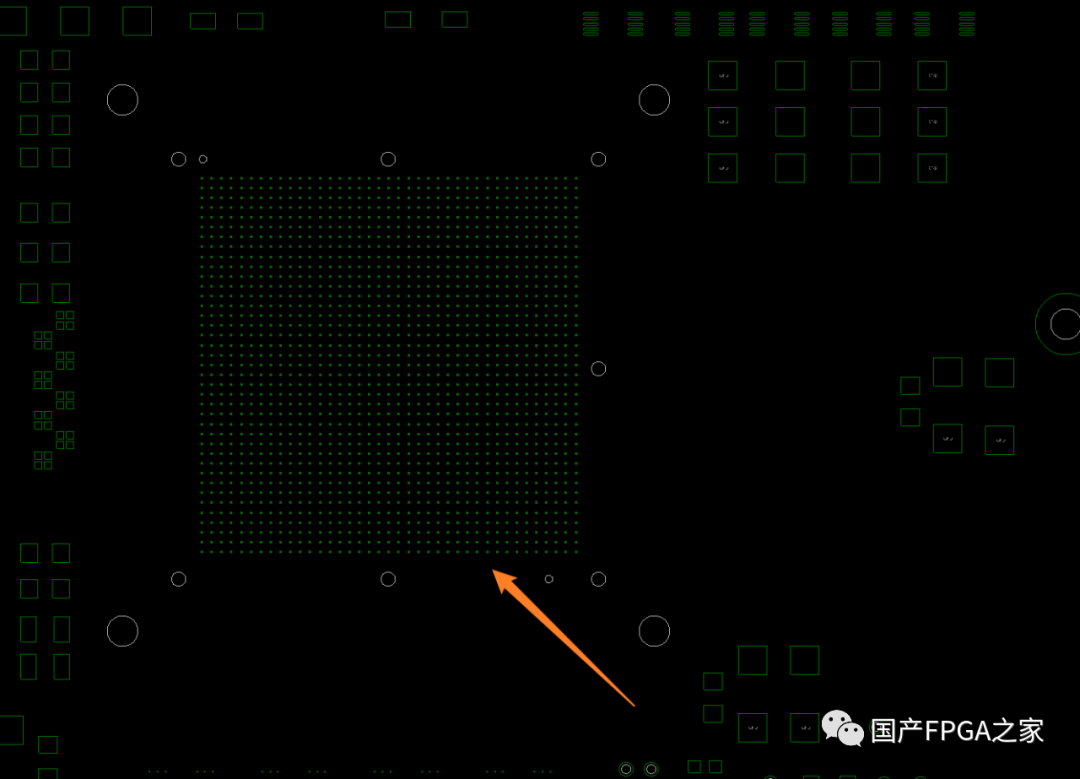

点击PCB 中的FPGA Symbol

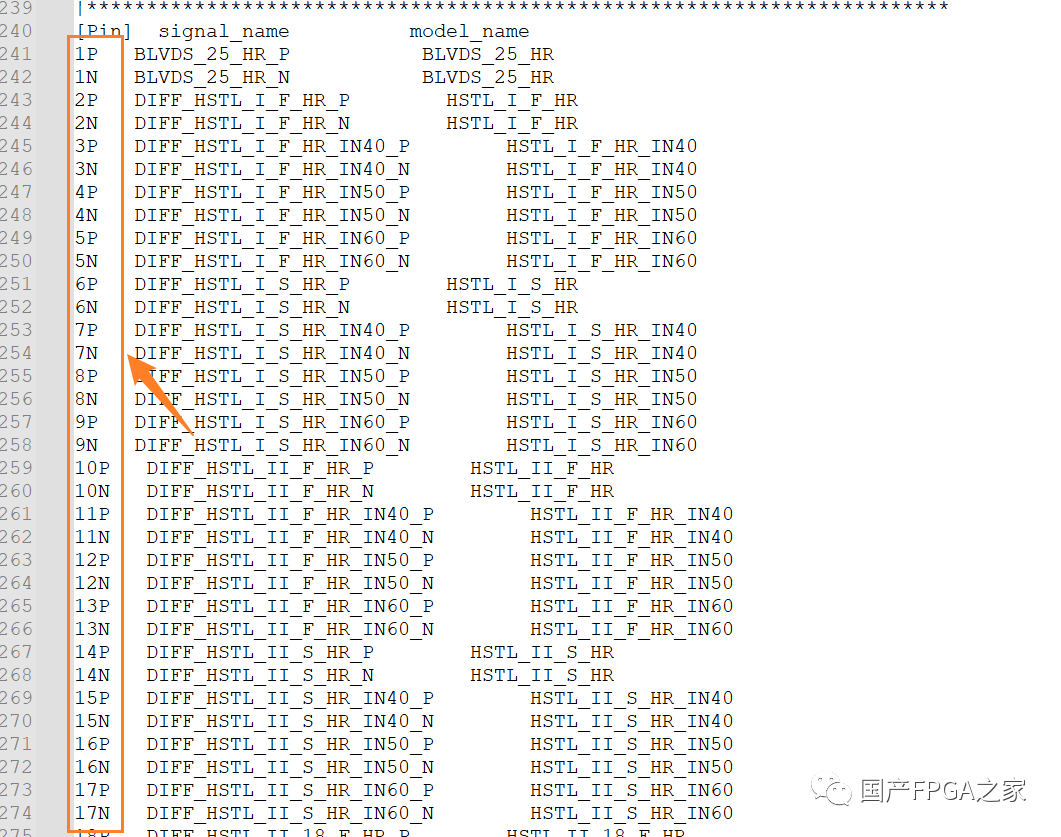

将会弹出fpga元件相关信息,其中包含我们需要的管脚与net的映射关系。

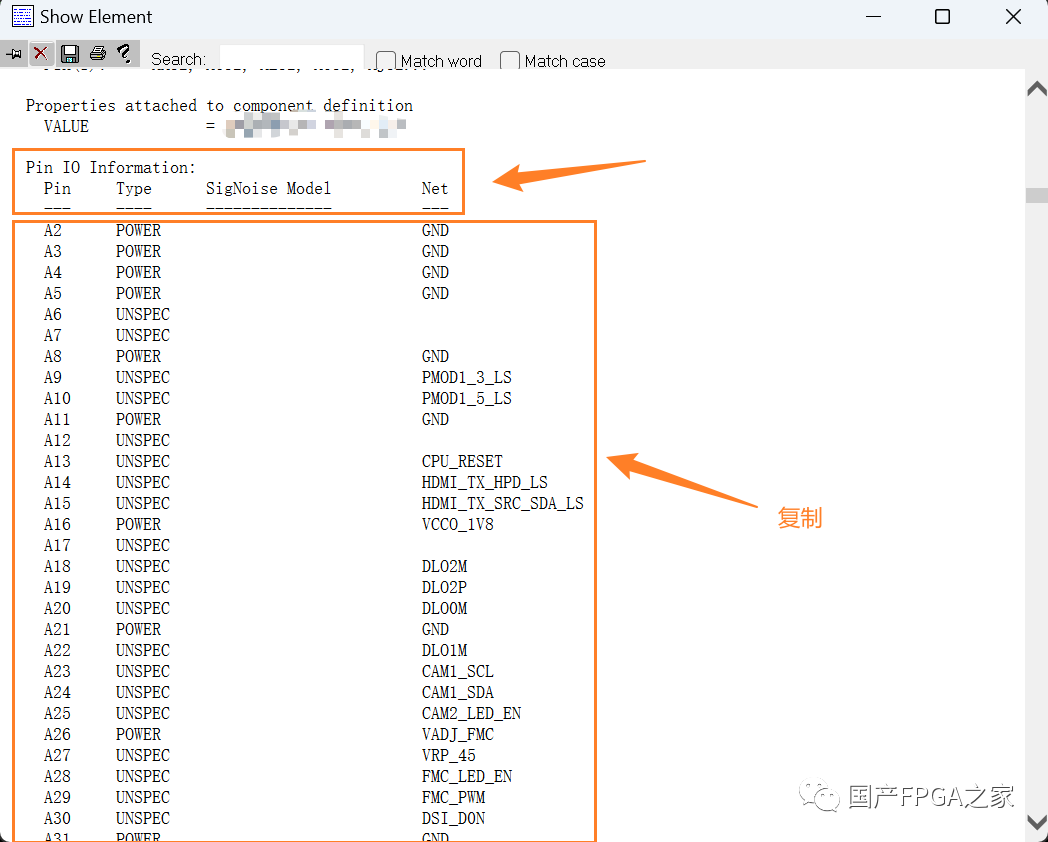

在弹窗中找到 Pin IO information的表格,表格文本信息即是我们需要的PIN与net映射关系,复制到管脚信息到外部txt。

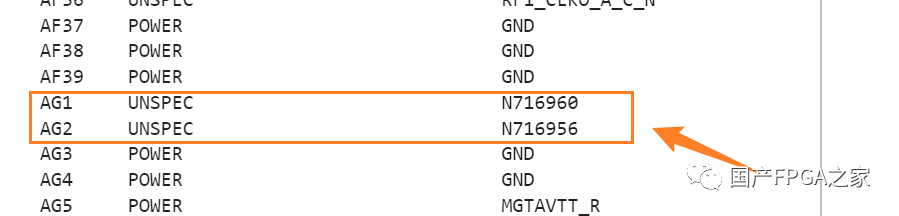

本节导出器件管脚与网络映射关系,需要注意的是如果fpga与外部连接网络没有命名,软件将自动分配网络名。这部分管脚名称,没有实际意义不便理解,可根据需求手动修改。

3 管脚约束/XDC文件生成

本节内容通过上节得到1对差分信号和一个单端信号为例说明编辑过程。

编写约束文件仅需要了解四种固定格式即可。 1、设置管脚到网络映射关系。具体语法格式如下:

set_property PACKAGE_PIN PIN [get_ports {NET}]

将PIN位置替换我们导出文件的管脚名,NET位置填写对应网络名。生成管脚约束示例如下:

set_property PACKAGE_PIN AV20 [get_ports {DDR4_PARITY}]

set_property PACKAGE_PIN AV21 [get_ports {DDR4_DQS5_C}]

set_propertyPACKAGE_PINAV22[get_ports{DDR4_DQS5_T}]

2、设置网络I/O STANDARD 属性。具体语法格式例子如下:

set_property IOSTANDARD PIN_STANDRAD [get_ports {NET}]将PIN_STANDRAD位置替换我们需要的I/O STANDARD标准,NET位置填写对应网络名。生成管脚约束示例如下:

set_property IOSTANDARD SSTL12_DCI [get_ports {DDR4_PARITY}]

set_property IOSTANDARD DIFF_POD12_DCI [get_ports {DDR4_DQS5_C}]

set_propertyIOSTANDARDDIFF_POD12_DCI[get_ports{DDR4_DQS5_T}]

具体电平标准请查阅芯片手册。 3、设置网络输入/输出属性,具体语法格式如下:

set_property DIRECTION DIR [get_ports {NET}]将DIR位置替换我们管脚属性,可以填写INOUT OUT IN三种,分别对应输入输出、输出和输入;NET位置填写对应网络名。生成管脚约束示例如下:

set_property DIRECTION OUT [get_ports {DDR4_PARITY}]

set_property DIRECTION INOUT [get_ports {DDR4_DQS5_C}]

set_propertyDIRECTIONINOUT[get_ports{DDR4_DQS5_T}]

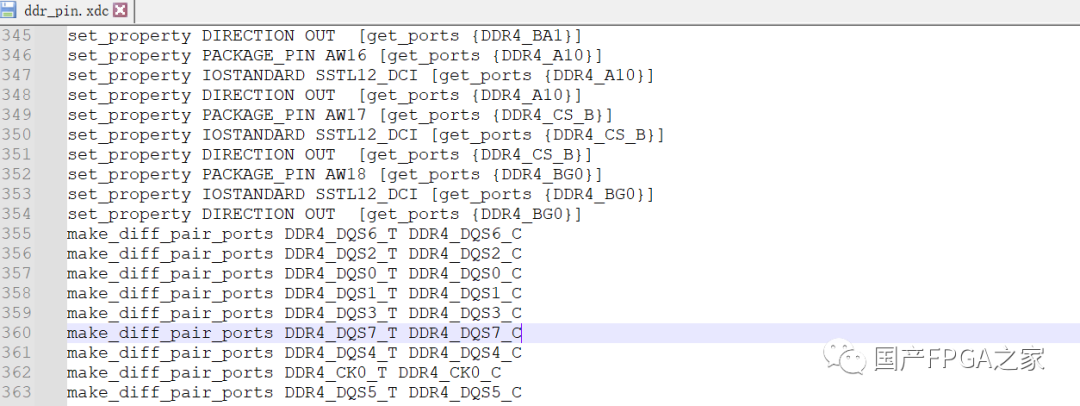

4、设置管脚差分关系。具体语法格式如下:

make_diff_pair_ports NET1 NET2将NET1 NET2位置填写对应差分对的网络名。生成管脚约束示例如下:

make_diff_pair_ports DDR4_DQS5_T DDR4_DQS5_C按照例子,对我们需要关注的管脚编写约束文件,并将文件保存为.xdc格式,我这里保存是ddr_pin.xdc。

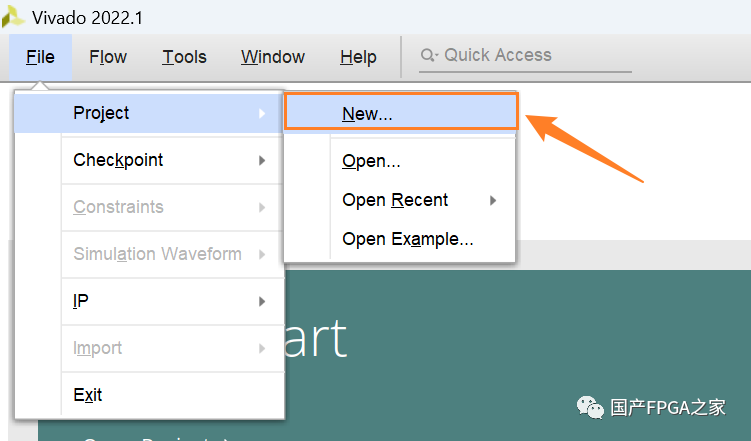

此过程流程操作流程相对简单死板,推荐根据自己网络命名规则编写脚本减轻工作量。 4 I/O Planning 导出 ibis文件 Vivado 的 I/O Planning和RTL工程中均可以导出ibis 文件。RTL工程中导出方法不在此处赘述。 1)新建I/O Planning 工程

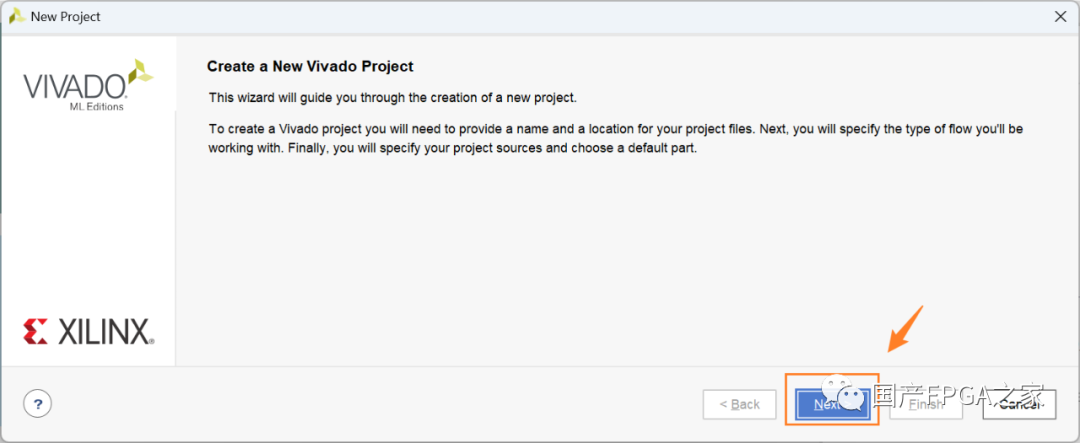

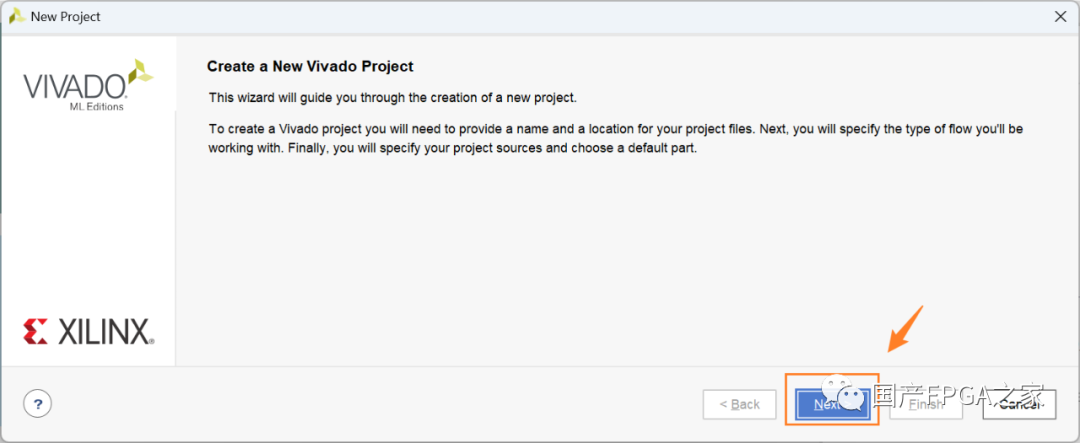

2)出现弹窗

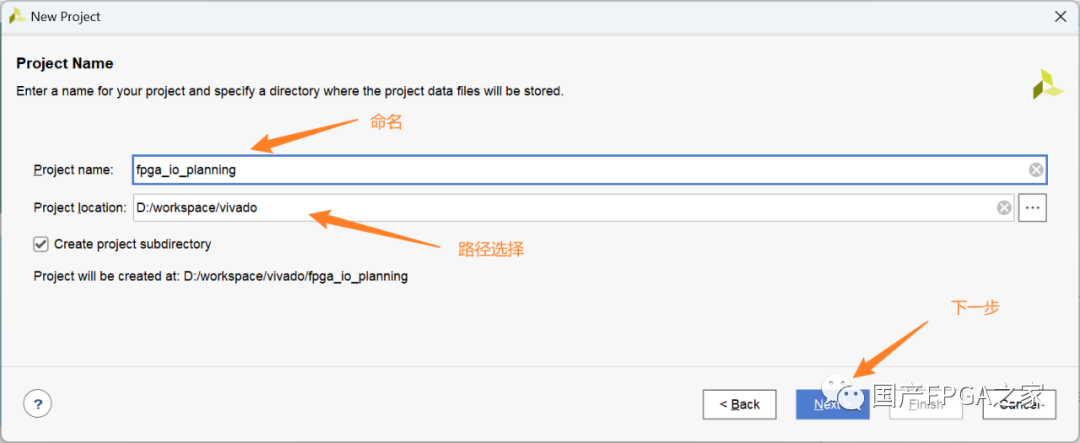

3)工程命名与路径选择

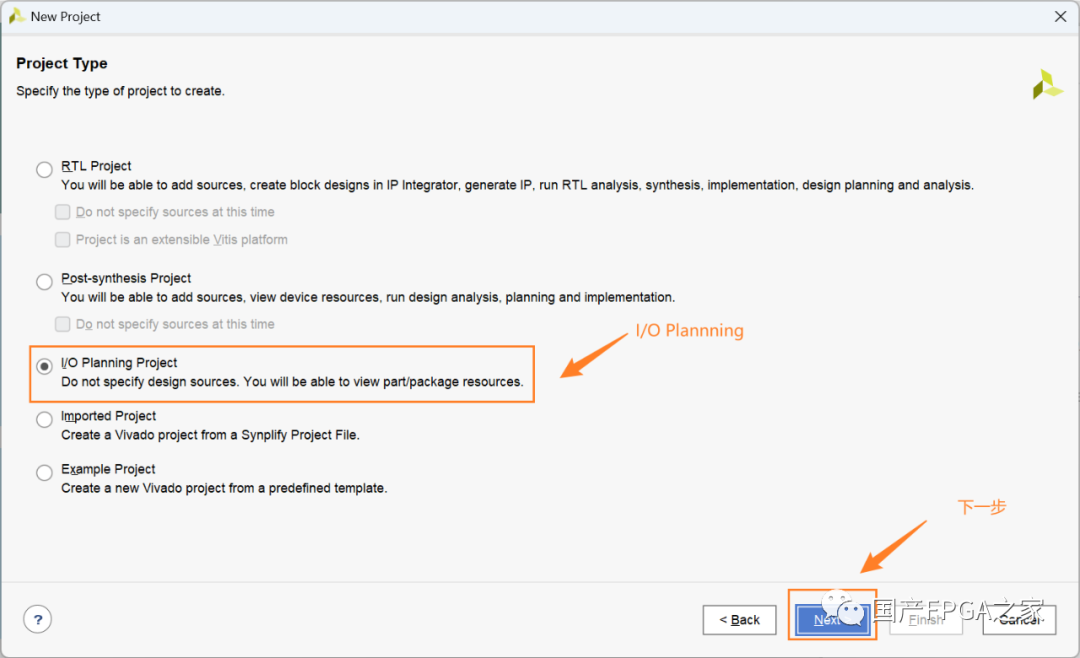

4)选择 I/O Planning 工程类型

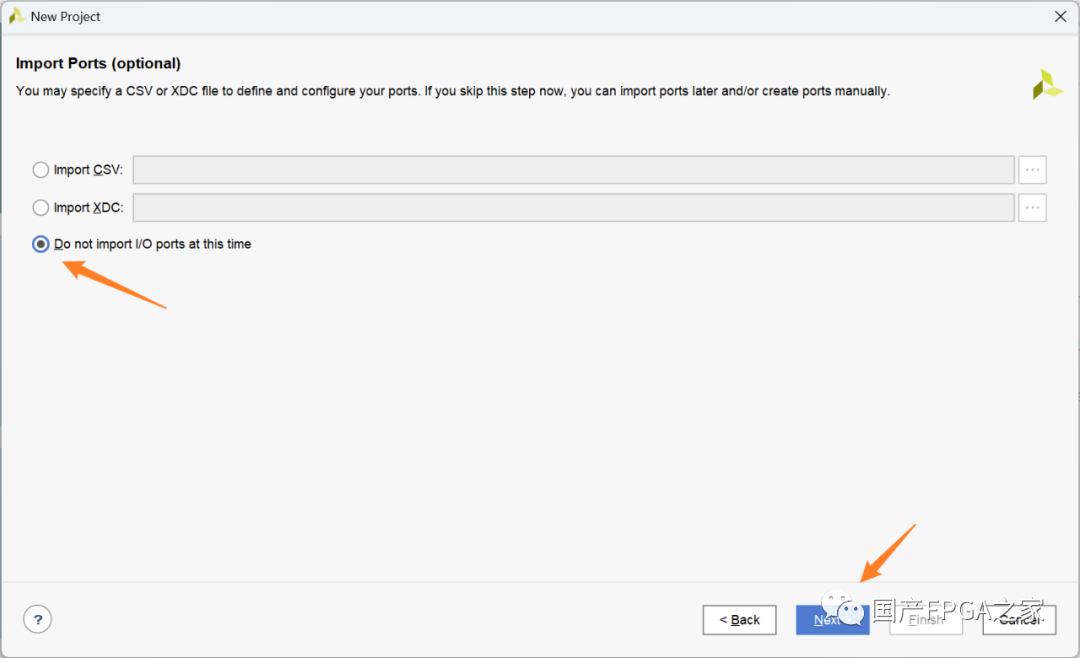

5)不导入文件,点击下一步

6)根据需求选择器件型号,点击下一步后,点击Finish 创建工程

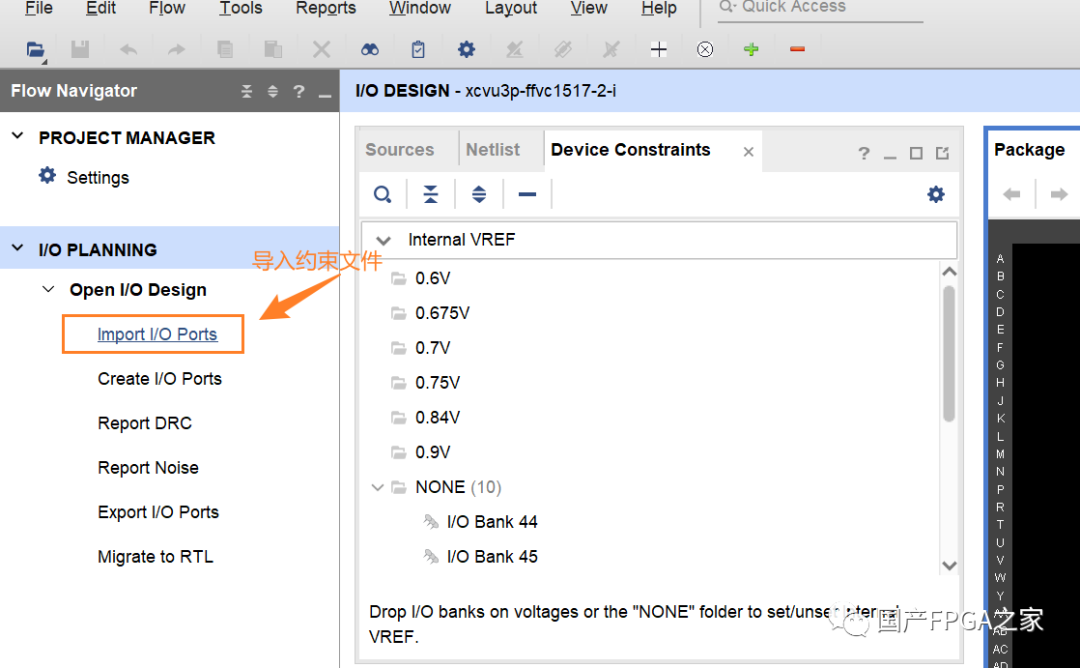

7)出现工程界面后,点击导入I/O Ports

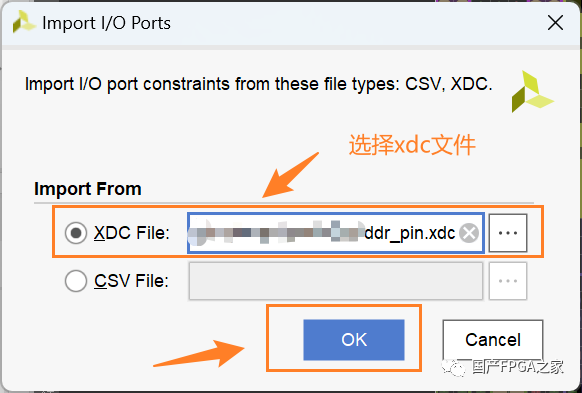

8)弹窗中选择准备好的xdc文件,点击OK。

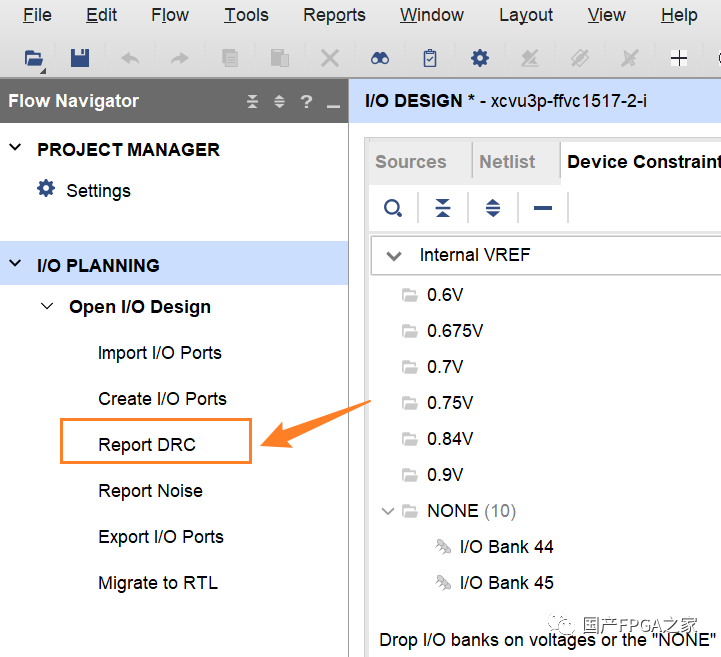

9)点击 Report DRC进行检查。

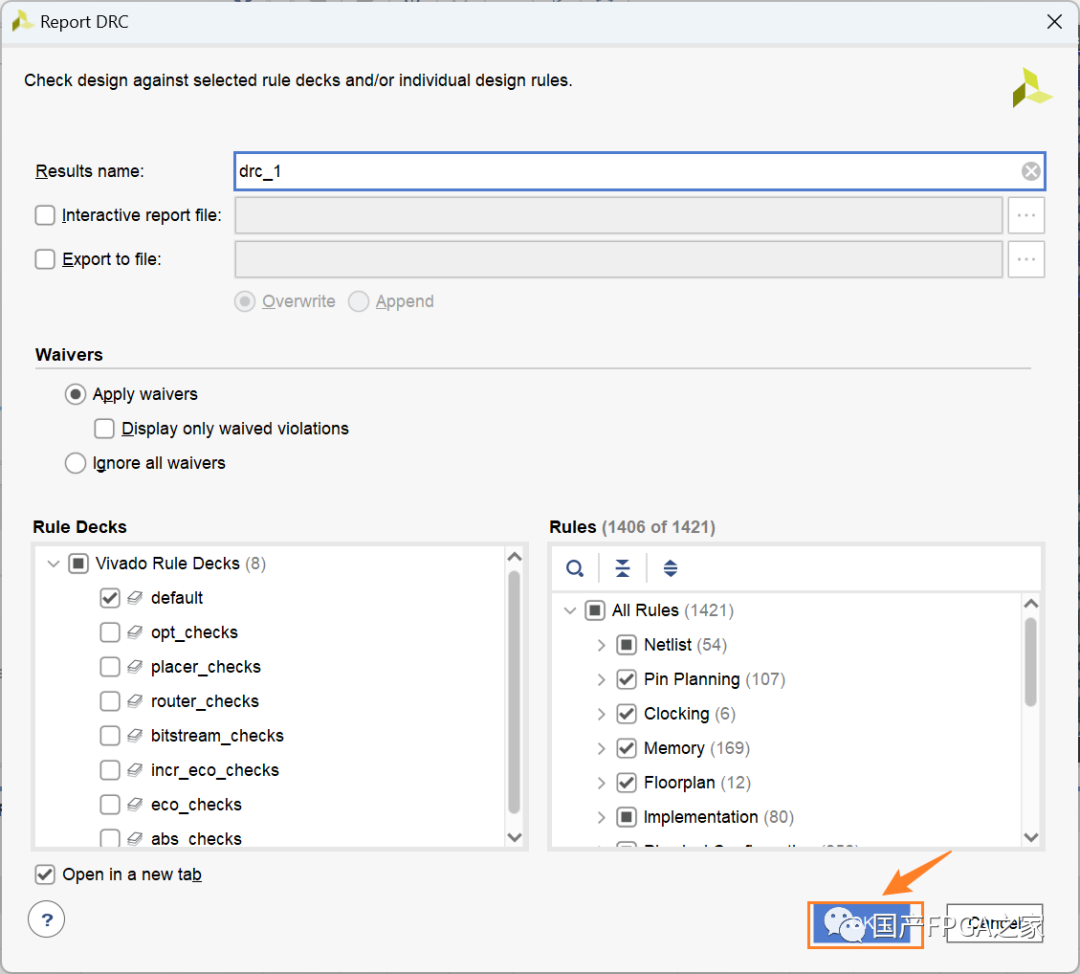

10)弹窗选择OK,如出现DRC报错需要复核硬件设计解决,避免导致硬件设计存在缺陷。

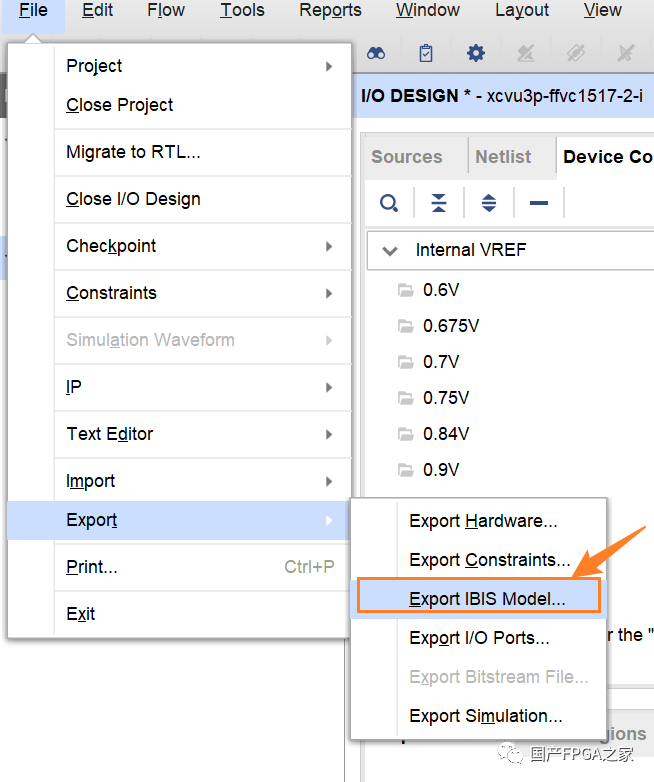

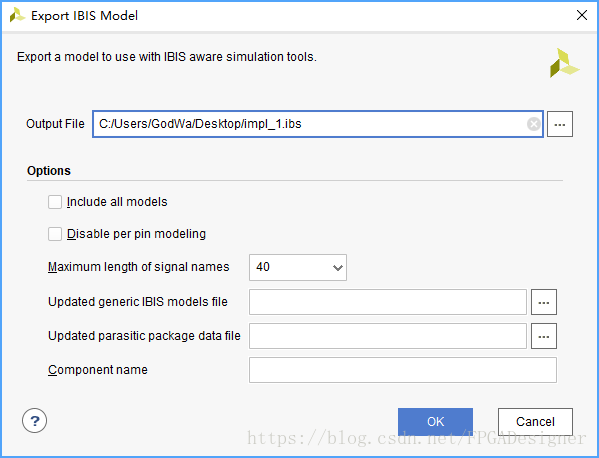

11)如DRC无报错,点击导出IBIS文件

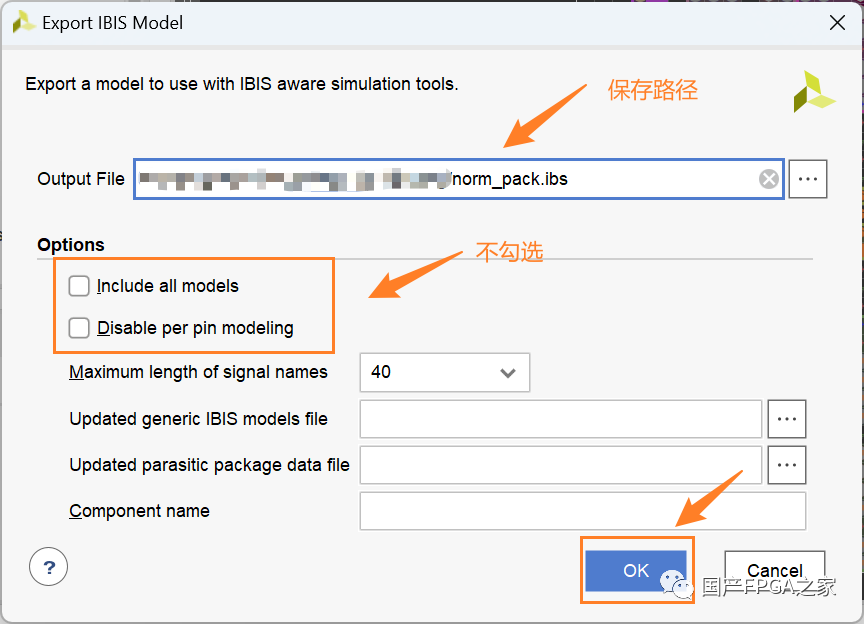

12)弹窗选择保存路径,完成导出。图中两个选项内容均不勾选。Include all models 选项勾选,在IBIS文件中增加我们没有涉及 IO模型内容;Disable per pin modeling 会剔除IBIS文件中包含的封装属性文件。

13)到这里模型生成完成,可以用于实际仿真。

战术总结

今天主要给大家简单介绍了IBIS模型的使用方法以及Vivado如何快速导出IBIS模型进行后续仿真使用的方法,欢迎各位大师在评论区留言讨论。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

传输线

+关注

关注

0文章

376浏览量

24021 -

IBIS模型

+关注

关注

8文章

15浏览量

17554 -

Vivado

+关注

关注

19文章

812浏览量

66470

原文标题:基于Vivado 的IBIS文件导出

文章出处:【微信号:国产FPGA之家,微信公众号:国产FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎么为防御等级Spartan-6生成IBIS文件

dose vivado如何将名称导出到I/O端口列表文件?

如何从VIVADO 2014.3向系统生成器导出设计文件?

如何在IBIS文件中配置SSTL135 DCI阻抗

请问如何在Vivado中导出IO端口跟踪长度?

pcb如何导出坐标文件

基于Vivado的IBIS文件导出

基于Vivado的IBIS文件导出

评论