01简介

在电路设计中,“接地”是一个无法避免的问题。接地需要考虑的主要因素:使用场景,不存在通用的接地方式。本文我们将以一种通俗易懂的方式谈谈接地问题的本质。

02接地分类

接地目的决定了接地的方式,从接地的性能上来说,接地主要可分为以下四类:

安全接地 。

工作接地 。

浪涌接地 。

静电接地 。

03接地目的

接地的主要目的主要有三大类,分别为对地阻抗低、地平面稳定、对地均衡。接下来,主要从这三个方面展开说明:

对地阻抗低

分析 :

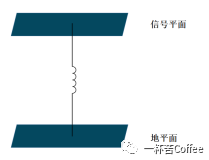

低频信号从信号平面流到地平面时,大电感相当于导线直接接地,此时表现出来的特性就是低阻抗。

高频信号从信号平面流到地平面时,大电感呈现出较大的阻抗,测试表现出来的特征就是高阻抗。

地平面稳定

地稳定是对地的阻抗足够大,电流比较容易直接泄放到地,同时在导线上几乎不会产生压降。将像辽阔的海洋中,汇入多少条河流都波澜不惊。

对地均衡

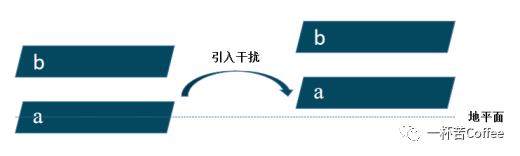

对于电源或者信号,对于我们真正有价值的往往是它们之间的压差。存在一种场景,一个电路当受到外部的干扰时,两个平面上的电压整体上升(差模电压保持不变,共模电压增大),具体见下图。其实电路通常依然能正常工作,并且这种场景其实我们常会遇到。

一个静电脉冲通过空气打到电路板上,针对局部的电路,距离远近的不同,肯定会导致产生静电感应的压差。这时候用一块金属板隔一下的话,即使该金属板浮空,对金属板后面的电路板来说,感应的将是均匀的电场,虽然感应干扰仍然存在,但起码电路上是基本均衡的。当然如果此金属板接地更好啦。当然共模电压一般不会维持住,因为传输线的阻抗不均匀,往往会转成差模电压干扰,地均衡的问题最好不要让我们面对,但没办法的时候,如浮地设备,不得不受到静电冲击的电路板,防护时候要考虑地均衡问题。

04共地耦合干扰

共地耦合干扰这个是处理接地的核心问题。

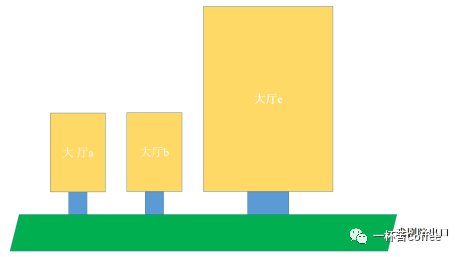

在一个戏剧院里,有三个大厅分别大厅a、大厅b、大厅c,出口仅有一个。当三个大厅同时三场时,大厅c的面积较大,容纳的人也越多。那么大厅c内部的 看客的 退场将会影响大厅a和大厅b内部人员的退场。(大厅a、大厅b、大厅c相当于三条对地的回流路径,走道相当于共地阻抗)

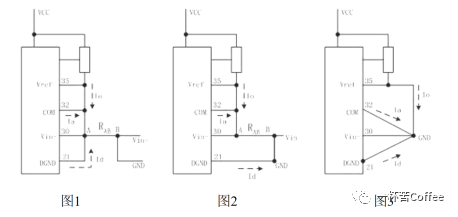

以下图为例,图1中,RAB段的电阻就是共地阻抗部分,流过这段的地电流Io、Ia、Id三部分在这段会相互影响;如果这三个电流差别较大,差出了1-2个数量级的话,相互之间的影响就不可以忽视了,尤其是某个弱地电流支路是用于定量测量、放大或AD转换电路的时候;图2则把Id对另外两个之路的影响隔离掉了;图3则是三个地电流全部分别隔离了。

05常用接地方式

基本思路 :在设计上,把安全保护地、工作数字地、工作模拟地、工作功率地、雷击浪涌地、屏蔽地先确保各自独立的单独连接,最后在系统联调的时候,再根据各地之间要解决的问题,即根据接地的目的,将这几个地按照下列的之间的联接方式处理下,连接方式包括:

| 序号 | 接地方式 | 描述 |

|---|---|---|

| 1 | 直接接地 | 适合中地频率,这类导线上有一定的走线电感和走线电阻,对高频波对地电流,在电感作用下,电缆起到的是大阻抗的作用,相当于低频接地,高频下大阻抗接地了,基本不能实现高频下的可靠导通。 |

| 2 | 大电阻接地 | 大电阻的特点是一旦电阻两端出现压差,就会产生很弱的导通电流,把地线上电荷泻放掉之后,最终实现两端的压差=0V,这个特点在希望电荷泻放,但又不希望快速泻放的时候。 |

| 3 | 小电阻接地 | 小电阻要解决的问题是增加了一个阻尼,阻碍地电流快速变化的过冲,在电流变化时候,使冲击电流上升沿变缓,相当于晶振输出端、总线输出端为减少过冲振铃的匹配电阻。 |

| 4 | 电感接地 | 一般用用在电流电流波动加大的场合,电感具有抑制电路状态变化的特性,通过电感的连接,可以销峰填谷。 |

| 5 | 磁珠接地 | 一般应用在弱信号与地之间,磁珠等同于一个随频率变化的电阻,它表现的是电阻特性,是耗损性质的;电感则是储能性质的,相当于削峰填谷。所以跨接磁珠的地之间一般是有快速小电流波动的状态,因为磁珠会饱和,电流太大了,它消耗不了。 |

注意 :因为雷击浪涌、安全地的电流一般会远大于信号电流对人的危害,这两个接地建议分别单独接到大地,在真正的大地处单点相接,尤其是防雷击接地。

05系统接地思考

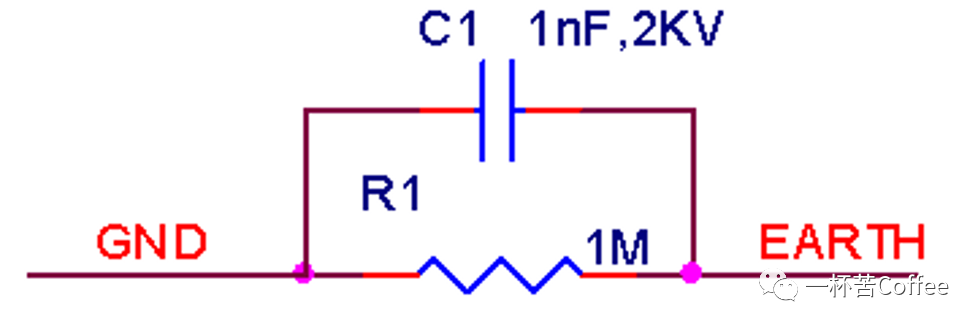

对于PE,电路设计过程中常使用阻容接地方式。很多系统直接两PE和板载GND连接在一起,这种连接方式可以让静电以最快方式泄放至GND。

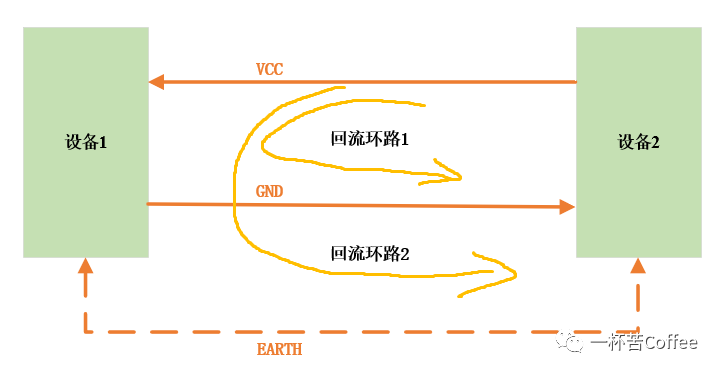

但是这种方式也存在弊端,两个设备直接连接大地,对于整个大系统而言,会造成直流回环和交流回环,即回环连接会增大,这样的系统更加容易引入干扰。并且对于安规来说,漏电流也是有要求的,直接连接地,可能会存在较大的漏电流,在一些较大系统中,要求系统与大地之间至少需要MΩ级别的电路。

但是这种方式也存在弊端,两个设备直接连接大地,对于整个大系统而言,会造成直流回环和交流回环,即回环连接会增大,这样的系统更加容易引入干扰。并且对于安规来说,漏电流也是有要求的,直接连接地,可能会存在较大的漏电流,在一些较大系统中,要求系统与大地之间至少需要MΩ级别的电路。

对于电阻电容选型,封装都为1206既可,需要使用高压瓷片电容,耐压2KV。如果对于安规要求比较严格,电容最好使用安规电容。对于而且对于系统地和机壳地的距离也有要求,比较通用的是华为流传出来标准,系统地和机壳地之间间距2mm。其实可以简单计算这个距离,按照电压空气击穿的30KV/cm,所以2mm间距能够保证6KV不会击穿放电。

而且在设计海思平台时候,华为手册上建议对于浮地系统定位孔直接和机壳相连,对于需要接大地的设备,最好将地进行隔离。

注意事项:

如果设备外壳良好接大地,那PCB应该也与外壳良好的单点接地,这个时候工频干扰会通过外壳接地消除,对PCB也不会产生干扰。

如果设备使用的场合可能存在安全问题时,那必须将设备外壳良好接地。

为了取得更好效果,建议是设备外壳尽量良好接地,PCB与外壳单点良好接地;当然如果外壳没有良好接地,那还不如把PCB浮地,即不与外壳连接,因为PCB与大地如果是隔离的(所谓浮地),工频干扰回路阻抗极大,反而不会对PCB产生什么干扰。

多个设备之间需要互相连接的时候,尽量是每个设备外壳都与大地在单点良好接地,每个设备内部PCB与各自外壳单点接地。

但是如果多个设备互相连接时候,设备外壳没有良好接地,那就不如浮地,内部PCB不与外壳接地。

机壳地可能并不是可靠的接地,如配电网中不符合安规,没有地线;接地棒周围土壤太干燥,接地螺栓生锈或松动。

环境是存在电磁干扰的,工作环境中有大功率变压器、大功率电机、电磁电炉、高压电网谐波等。

PCB内部是会产生高频噪声的,如高频开关管、二极管、储能电感、高频变压器等。

-

电路设计

+关注

关注

6676文章

2453浏览量

204435 -

接地

+关注

关注

7文章

769浏览量

45676 -

浪涌

+关注

关注

3文章

255浏览量

28532 -

数字地

+关注

关注

2文章

49浏览量

10732 -

模拟地

+关注

关注

0文章

53浏览量

11025

发布评论请先 登录

相关推荐

怎么成为硬件电路设计高手?

硬件电路设计的思路分享

电路图接地分析_电路如何接地?电路接地的方法

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之接地问题

硬件电路设计之接地问题

评论