引言:在多相电源控制器里,PWM波输出最为常见,但是HL型也使用较多,与PWM型相比,HL型控制更为独立,更为灵活,抗干扰能力也较好,唯独就是需要两个控制输出,本节简述HL型栅极驱动器。

1.驱动结构

HL型也是以半桥配置驱动两个N沟道MOSFET,支持电源电压高达140V,高侧和低侧驱动器都可以用不同的接地参考来驱动MOSFET,从而提供出色的噪声和瞬态抗扰性。其强大的0.8Ω下拉和1.5Ω上拉MOSFET驱动器允许使用大栅极电容的高压MOSFET。附加功能包括UVLO、TTL/CMOS兼容输入、可调开启/关闭延迟和贯通保护。

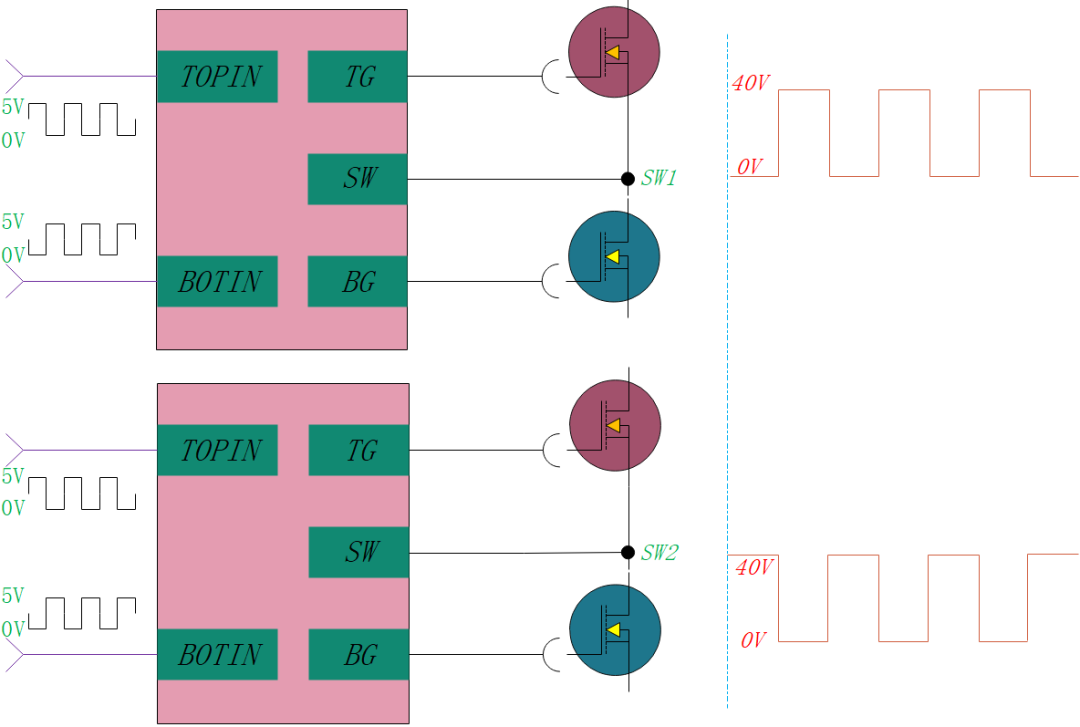

图9-1:HL两态驱动典型使用样式

TOPIN:顶侧驱动器的逻辑输入,如果TOPIN是没有偏置或浮动的,则TG保持在低位。

BOTIN:底部驱动器的逻辑输入,如果BOTIN是没有偏置或浮动的,则BG保持在低位。

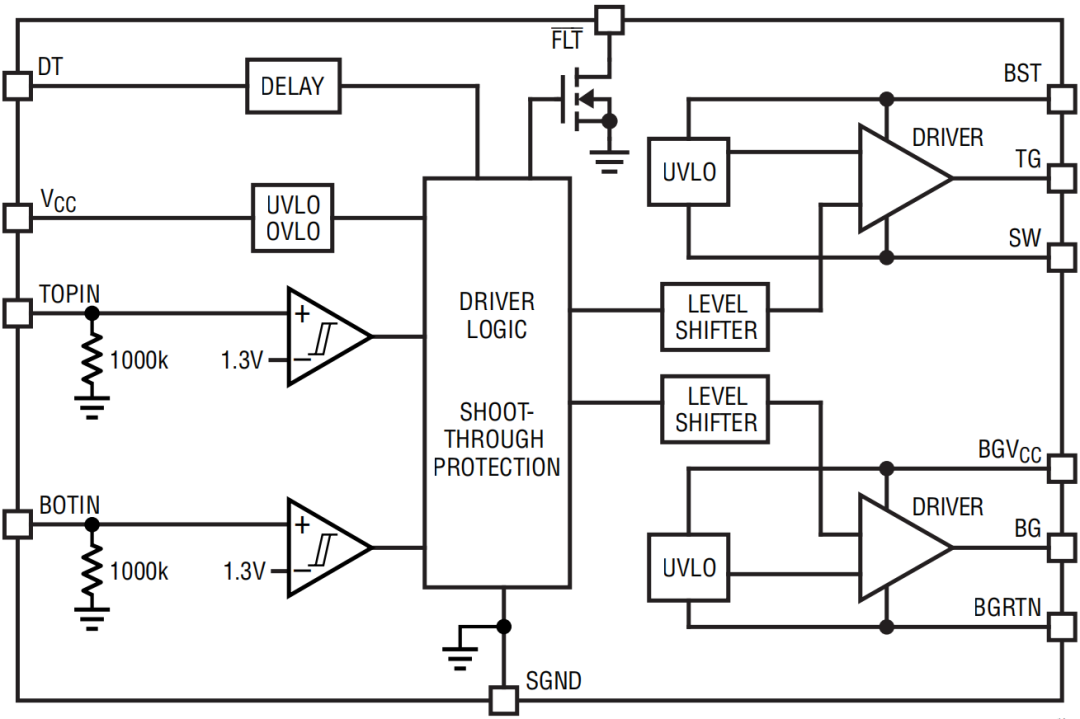

图9-2:HL两态栅极驱动器内部结构

HL型栅极驱动器具有两个接地参考的低电压数字信号输入,用于驱动半桥配置中的两个N沟道功率MOSFET。输出BG被驱动为高或低,在BGVCC和BGRTN之间摆动,这取决于BOTIN引脚,类似地,输出TG在BST和SW之间摆动。每个通道都由其输入引脚(TOPIN和BOTIN)控制,允许独立灵活地控制输出的开启和关闭状态,但不允许TG和BG输出同时变高。具有出色的噪声和瞬态抗扰性,包括开关节点(SW、BGRTN)上的大负接地差容限(−10V),对称设计允许半桥输出是输入逻辑的反相或非反相。

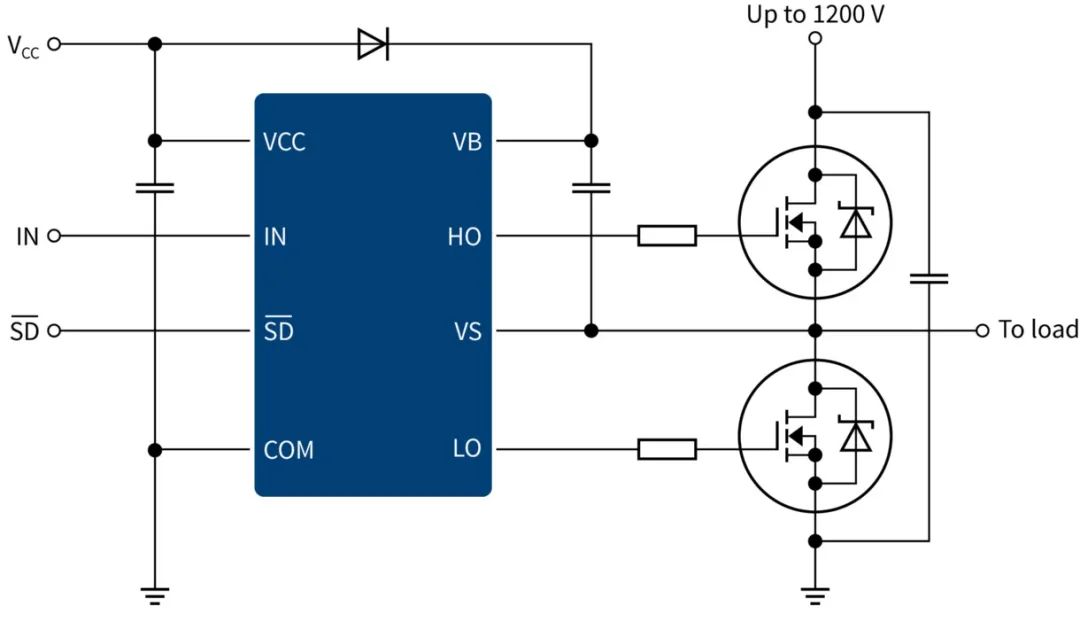

图9-3:半桥驱动IC的基本连接形式

图9-3的输入和图9-1的输入有所不同,图9-3将IN信号经过一个内部施密特触发器之后进行反相,IN信号控制HS,/IN控制LS,然后中间间隔一定的死区时间,所以这种是类似HL型的栅极驱动器。

2.驱动逻辑

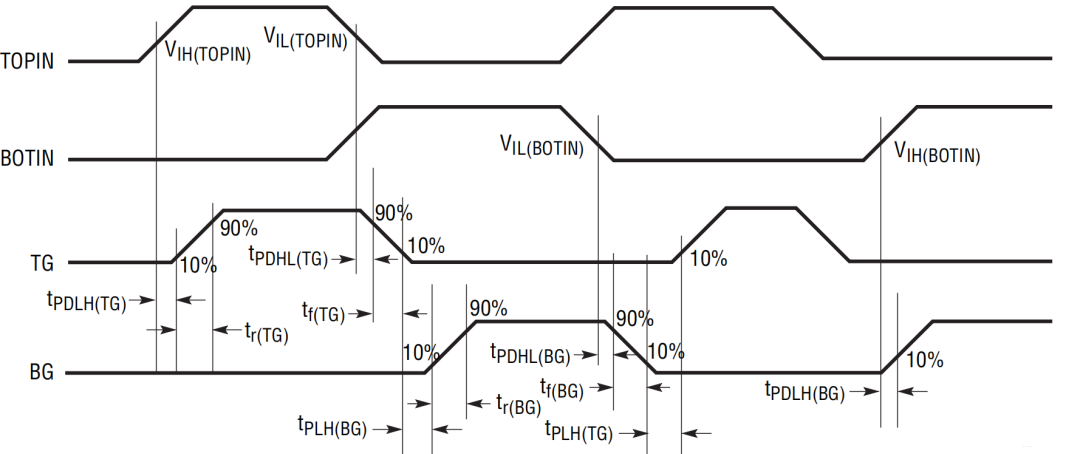

HL栅极驱动器采用两个具有固定转换阈值的逻辑输入,当TOPIN上的电压大于阈值VIH(TOPIN)时,TG被上拉到BST,使高侧MOSFET导通。该MOSFET将保持导通,直到TOPIN下降到VIL(TOPIN)以下。类似地,当BOTIN大于VIH(BOTIN)时,BG被上拉到BGVCC,使低侧MOSFET导通,BG将保持高电平,直到BOTIN下降到阈值VIL(BOTIN)以下。对应的VIH和VIL电压电平之间的滞后消除了由于开关转换期间的噪声而引起的错误触发,但是应注意防止噪声耦合到输入引脚(TOPIN、BOTIN),特别是在高频和高电压应用中。

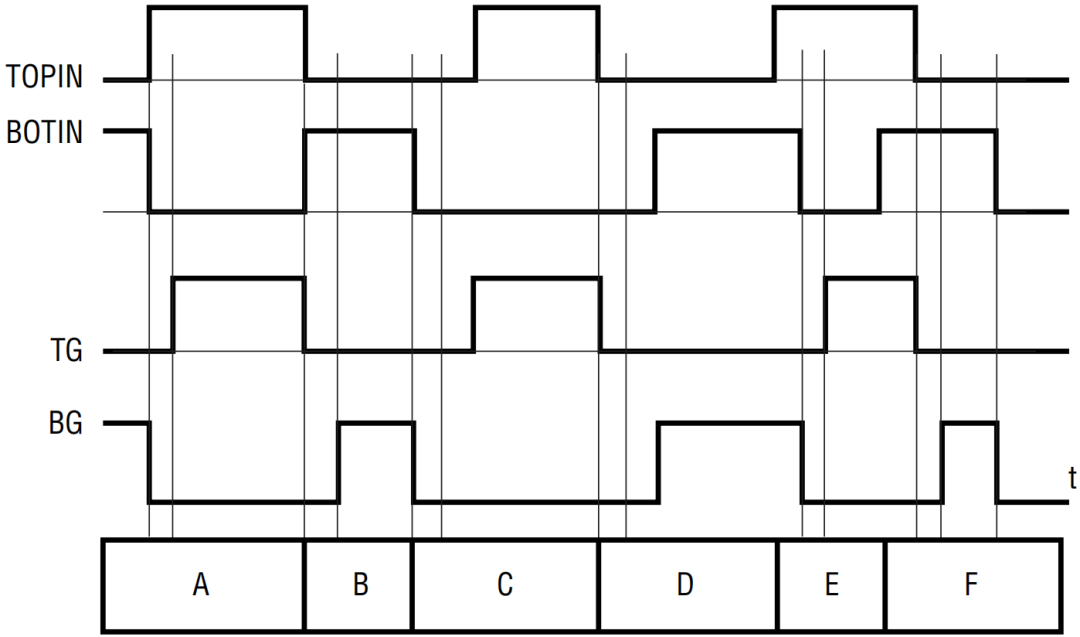

图9-4:两态栅极驱动器时序图

当TOPIN/BOTIN引脚浮动时,从TOPIN/BONTIN引脚到SGND有一个内部1000kΩ下拉电阻器,如果输入未被驱动,则保持TG/BG默认状态为低。PWM控制器IC可以利用TOPIN和BOTIN输入引脚来在开关调节器应用中执行不连续传导模式(DCM)。图9-5表示了输入和输出的逻辑关系:

图9-5:输入和输出的逻辑关系

状况A:TOPIN走高,BOTIN走低,BOTIN立即将BG设置为低,允许TG在tdt之后变高。

条件B:TOPIN变低,BOTIN变高,TOPIN立即将TG设置为低,允许BG在tdt之后变高。

条件C:TOPIN上升,BOTIN下降自身停滞时间大于tdt,因此当TOPIN变高时,TG立即被设置为高。

条件D:TOPIN下降和BOTIN上升自身停滞时间大于tdt,因此当BOTIN变高时,BG立即被设置为高。

条件E:TOPIN高,而BOTIN仍然高,BOTIN压制TOPIN上升沿,在BOTIN变低加上tdt之后,允许TG变高。

条件F:BOTIN高,而TOPIN仍然高,TOPIN压制BOTIN上升沿,在TOTIN变低加上tdt之后,允许BG变高。

注:TG指SW,BG指BGRTN。

此外,驱动器输出上的强下拉防止了交叉传导电流,例如,在图9-1所示的半桥配置中,当BG关闭低侧功率MOSFET,TG打开高侧功率MOSFET时,SW引脚上的电压可能会非常迅速地上升到VIN。该高频正电压瞬态将通过低侧功率MOSFET的CGD电容耦合到BG引脚。如果BG引脚没有被充分压下,BG引脚上的电压可能会上升到低侧功率MOSFET的阈值电压以上,从而瞬间使其重新导通。因此,高侧和低侧MOSFET都将导通,这将导致大量的交叉导通电流通过MOSFET从VIN流到地,从而导致相当大的功率损失并且可能损坏MOSFET。因此,建议使用BG和TG引脚的短PCB迹线,以最大限度地减少寄生电感。

3.功耗

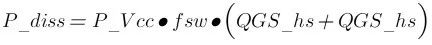

驱动器的功耗主要由外部功率MOSFET的栅极电荷提供,下列公式成立:

fsw是开关频率,QGHS和QGLS分别是PVCC驱动电压下的高侧MOSFET的栅极电荷和低侧MOSFET栅极电荷。

考虑具有一个高侧MOSFET(BSC50NE2LS)和一个驱动电压为5V和开关频率为500KHz的低侧MOSFET的降压转换器应用,功率耗散是:

驱动器本身也有少量功耗,在300KHz的开关频率下,驱动器的功耗在10mW的范围内,该功耗由IPVCC_300kHz乘以驱动电压(5V)得出。

- layout注意事项

HL栅极驱动器需要在VCC、VBST-SW和VBGVCC-BGRTN电源上进行适当的旁路,因为它具有ns级高速开关和A级大交流电流。不小心的元件放置和PCB布线可能会导致过度振铃和欠调/过调。并且PCB和功率器件封装(上下MOSFET)的寄生电感会导致严重的振铃,超过器件的绝对最大额定值,优秀的布局可以帮助最大限度地减少这种不必要的影响。

1:在VCC和SGND引脚、BGVCC和BGRTN引脚以及BST和SW引脚之间安装尽可能靠近的旁路电容器,引线应尽可能缩短,以减少引线电感。保持去耦回路(PVCC-GND和BOOT-PHASE)尽可能短。

2:使用低电感、低阻抗接地平面来减少任何接地跌落和杂散电容,驱动器开关的峰值电流大于5A,任何显著的接地压降都会降低信号的完整性,最小化走线电感,尤其是在低阻抗线路上,所有电源走(UGATE、PHASE、LGATE、GND、PVCC)应尽可能短且宽,PHASE节点也应该是短而宽的。最小化PHASE节点与高侧MOSFET源极和低侧MOSFET漏极之间的距离,以避免效率损失。

3:仔细规划电源/接地布线,了解大负载开关电流的来源和去向,为输入引脚和输出功率级保持单独的接地回路。

4:Kelvin将TG引脚连接到顶部MOSFET栅极,将SW引脚连接到顶级MOSFET源极。Kelvin将BG引脚连接到底部MOSFET栅极,将BGRTN连接到底部FET的源极,保持驱动器输出引脚和负载之间的走线短而宽。

5:确保将驱动器封装背面的外露焊盘焊接到板上,如果暴露的背面和铜板之间没有良好的热接触,将导致热阻远大于封装的规定值。

6:最小化输出和输入传导的电流回路,将下部MOSFET的源极连接短接至接地,尽可能靠近晶体管引脚,输入电容器(尤其是陶瓷去耦)应尽可能靠近上部MOSFET的漏极和下部MOSFET的源极。

为了优化散热,无论IC是否有暴露的焊盘,都应将铜皮铺满IC下方,铜区域可以延伸超过IC的底部区域和/或通过热过孔连接到埋铜平面,用于垂直散热的过孔、延伸的铜平面和用于散热的埋平面的这种组合可以实现IC全部散热能力。

5.layout示例

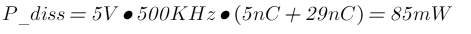

在图9-6中,示出了具有SuperSO-8高侧MOSFET和低侧MOSFET的局部布局示例,驱动器的相位连接尽可能靠近高侧MOSFET的源极,并且为了提高连接本身的可靠性和寄生电感,过孔被加倍。

VCC和PVCC的两个去耦电容,以及BOOT电容,都放置在驱动器所在的底部,为了与低侧MOSFET具有非常好的热耦合和非常小的寄生电感,使用多个过孔将驱动器的露焊盘连接到GND,GND最终是低侧MOSFET的源极。

图9-6:5相位电源示例

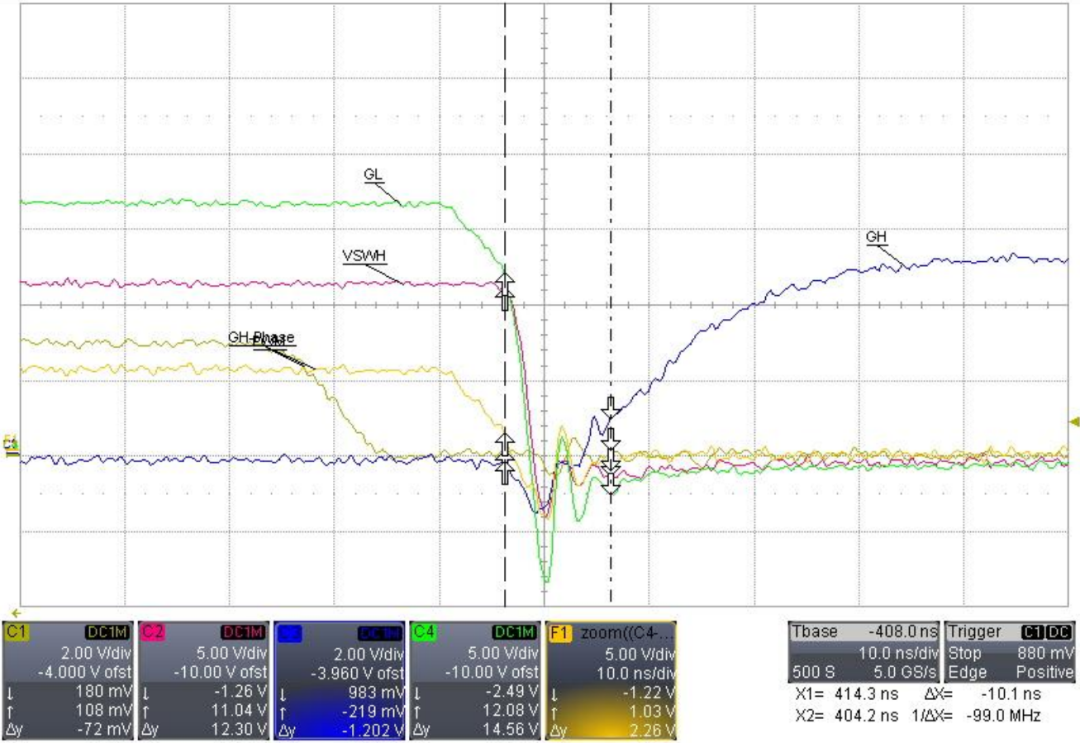

如图9-7所示,从高侧开启到高侧关闭和低侧开启的过渡时间非常小,VSW引脚的下降沿在4ns的范围内,同时完全切换高侧栅极所需的时间在6ns的范围内。由于噪声,从VSW/PHASE节点识别高侧MOSFET关断和低侧MOSFET导通之间的死区时间可能很困难,参考由低侧MOSFET栅极信号在其克服1V值时给出,在这种情况下,死区时间可以估计在6ns左右。

图9-7:TURN OFF

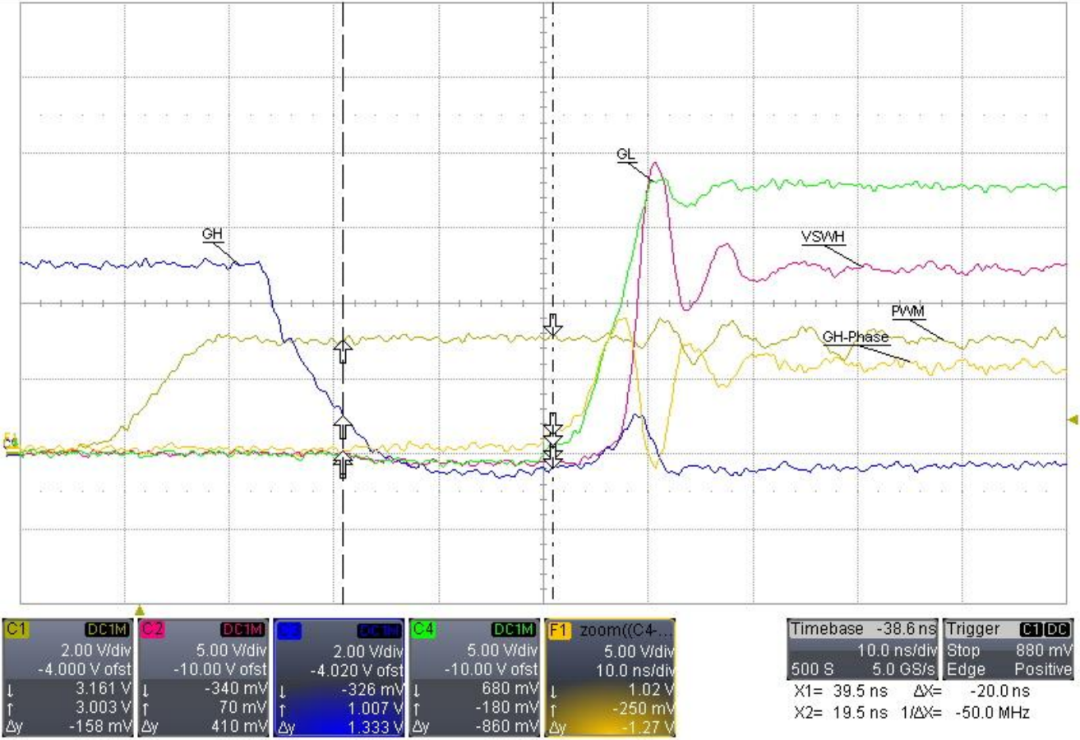

从低侧MOSFET开启到高侧MOSFET打开的转变如图9-8所示。在这种情况下,VSW/PHASE节点的上升沿在4ns的范围内,考虑到低侧栅极何时跨过1V阈值,死区时间的持续时间更多地在10ns的范围内。在高侧MOSFET的上升沿期间,可以在低侧MOSFET栅极上看到尖峰,该尖峰通常被理解为感应导通的标志(在VSW/PHASE节点)。大多数时候,由于封装或走线连接的寄生电感,栅极上的尖峰只不过是尖峰,换句话说,尖峰不会立即转换为在低侧MOSFET的VGS上的尖峰。

图9-8:TURN ON

-

MOSFET

+关注

关注

152文章

10892浏览量

235393 -

驱动器

+关注

关注

54文章

9125浏览量

156870 -

控制器

+关注

关注

114文章

17909浏览量

195728 -

PWM

+关注

关注

116文章

5903浏览量

227054 -

栅极驱动器

+关注

关注

8文章

1514浏览量

40534

发布评论请先 登录

HL型栅极驱动器内部结构解析

HL型栅极驱动器内部结构解析

评论