01摘 要

针 对 图 像 传 输 过 程 中 的 多 路 径 、非 通 视 和 高 速 移 动 等 特 点 ,提 出 了 一 种 FPGA+ W5300 架 构 的C0FDM 无 线 图像 传 输 系 统 ,实 现 图 像 的 无 线 发 射 和 接 收 。该 架 构 中采 用 Xilinx 公 司 Spartan-6 系 列 XC6SLX150 FPGA 作 为 主 控 芯 片 ,用于 实 现 C0FDM 数 字 调 制 、射 频 芯 片 的 配 置 ,同 时 为 A /D 转 换 器 和 D /A 转 换 器 提 供 工 作 时 钟 。采 用 W5300 硬 件TCP/IP 协议 栈 通 过 网 络 进 行 数 字 信 号 的 传 输 ,提 高 数 据 的 传 输 速 率 ,外 加 ADL5385、LT5506 等 上 下 变 频 芯 片 及 其 相 关 外 设 电 路 ,最终 实 现 一 个 收 发 一 体 、发 射 频 率 可设 、高 灵 敏 度 的 无 线 图 像 传 输 系 统 硬 件 平 台 。测 试 结 果 表 明 ,该 硬 件 平 台 能 够 实现图像的无线传输 ,具 有 良 好 的 抗 多 径 和 高 动 态 性 能 。

02引言

无线图像传输在民用和军事应用范围都发挥着十分关键的作用,从一般的无线视频监控到智能机器人和空中无人机等,无线图像传输都是其中十分重要的关键技术[1]。随着分辨 率 日 益 提 高 ,视频和图像的数据量与日俱增,在有限的频谱资源中是很难进行直接传输的 。一 般在进人无线信道之前都需要将传输的数据进行视频和图像数据的压缩编码。然 而 ,这些视频和图像数据在压缩编码之后对于无线信道中所引人的误码十分敏感,很难在时变的无线 衰 落 信 道 中 进 行 高 速 率 高 可 靠 性 传 输 [2]。而正交频分复用(O FDM) 多 载 波 调 制技 术 ,具有频谱利用率高、抗干扰能力强、对抗多径及均衡器简单等优点 ,非常适合上述高速率数据的传输[3]。基于以上优 点 ,提 出 了 一 种 基 于 F P G A + W5 3 0 0 的 C O FD M 无线图像传输系统硬件平台的设计方案[4]

03整体架构设计

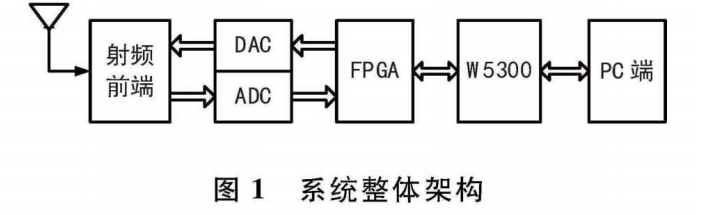

COFDM 无线图像传输系统,主 要 包 括 发 射 、接收和数据传输三大部分,其中发射和接收部分又可分为射频前端模拟信号的处理,以 及 FPGA 实现基带 部 分 对 数 字 信 号 的 COFDM 的 调 制 解 调 ,而衔接这 2 部 分 的 桥 梁 通 过 ADC 和 DAC 来 实 现。FPGA 调 制 和 解 调 的 数 据 传 输 通 过 硬 件TCP/IP 协议栈 W5300 来 实 现 ,大大提高了数据传输的速率 0 由此设计的系统整体框图如图 1所 示 。

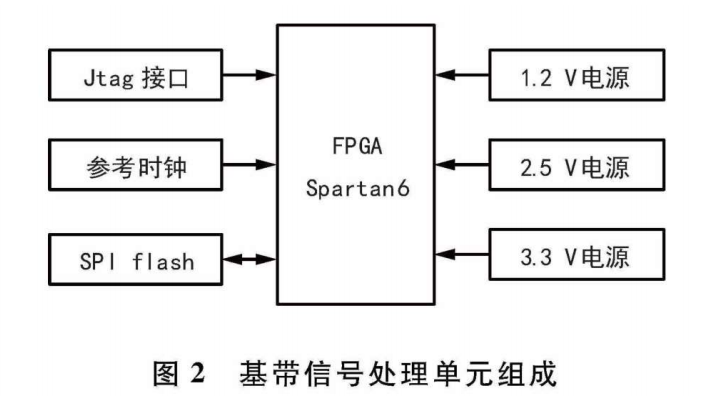

基带单元的设计在无线图像传输系统中,由 于 FPGA 的极强并行 处 理能力[5],因而可以对数字信号进行实时处理 ,同时,由于它可以通过面向芯片结构的软件编程来实现其相对应的功能,具有很强的灵活性,并且开发成本相对较低,所以 选用FPGA实现基带数字信号处理是完全可行的。本设计中选择Xilinx 公司的sPartan6 系 列 FPGA 作 为 基 带 处 理 单 元 [6],系统框图如图2所示 。

基带处理单元的系统框图包括 FPGA 工作模式配置、参考时钟、电源、Jtag 接 口 电 路 和 SPI flash 接口电路等。FPGA 提 供 射 频 载 波 发 生 器 写 配 置 字 ,并 且 完 成 COFDM 的 数 字 信 号 的 调 制 解调 @,提供 A/D 转 换 器 和 D/A 转换器的工作时钟以及数据接口,同时控制网络协议芯片 W5300[8]进行数据的转换 ,其中 SPI flash 选择 Winbond 公司的 W25Q64FV 用 于 verilog 逻辑代码的固化以及控制指令的存储。

参 考 时 钟 选 择 20 MHz 的 有 源 温 补 晶 振 E3113-20 MHz 为 FPGA 提供稳定的参考时钟,同时此晶振也为本振提供参考时钟输人。

04发射部分设计

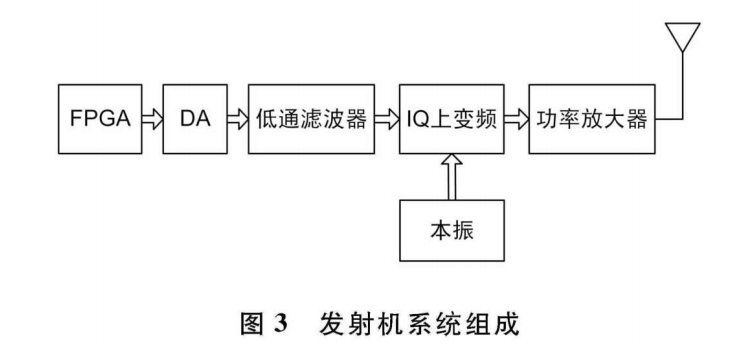

发 射 机 的 系 统 框 图 如 图 3 所 示 ,通过网口接收数 据 ,传 人 FPGA,FPGA 进行数据格式转换,重新分段 打 包 ,然 后 做 COFDM 数 字 调 制 ,分 I、Q 两 路 ,输人 到 双 路 D/A,由 于 D/A 转 换 之 后会 带 来 镜 像 杂波 ,所 以 D/A 转 换 之 后 进 行 低 通 滤 波 ,集成压控震荡器[9]提供载波频率,并且可以 通 过 FPGA 配 置,IQ 上变频器调制到射频,再经功放进行功率放大,之后通过天线进行发射 e

在 FPGA 中 进 行 COFDM 调 制 之 后 为 I、Q 两路输 出 ,所 以 选 择 了 双 路 十 位 的 D/A 转 换 芯 片AD9763 将 并 行 数 字 信 号 转 换 为 I、Q 两 路 模 拟 信号 。FPGA 提 供 D/A 转换器的工 作 时 钟 ,易于控制时钟与输出数据的同步。由于A/D 转换芯片的模拟输出端为差分输出,所以对低通滤波器的设计需要进行4 路信号的滤波,并且把4路信号的功率差控 制 在 1.5 dB 范 围内# 为了后期易于调整通频带带宽 ,这里选择 LC 滤 波 器 ,LC 的级数以及每级电感 电 容 值 的 大 小 通 过 ADS 仿 真 得 到 ,为了保证载波 频 率 为 130 MHz、350 MHz 以 及 550 MHz,综合考虑 载 波 频 率 和 D/A 的 输 出 信 号 格 式 ,这 里 选 择 IQ 上 变 频 芯 片 为 ADL5 3 8 5 进 行 IQ 上 变 频 ,选用ADF4 3 5 1 可 配 置 的 差 分 输 出 集 成 压 控 振 荡 器 为 ADL5385 提 供 载 波 。ADL5385 正常的输出功率为 4.7 dBm,而发射机的发射功率要求为 30 dBm,所以需要选择的功率放大器芯片增益至少为 25.3 dBm,并且1 dB压 缩 点 不 能 低 于 30 dBm,综合以上考虑选 择 功 放 芯 片 型 号 为 RF6886。功率放大口经射频开关进人天线进行发射,此处射频开关需满足发射信号的特性,保证信号的完整性,射频开关芯片的型号为HMC544A。

05接收部分设计

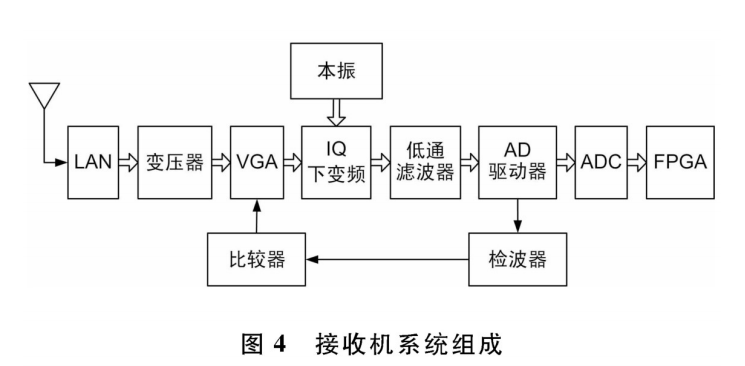

接收机的系统框图如图 4 所 示 ,天线接收信号,经低噪声放大器进行放大,之后进行下变频到基带,由低通滤波器进行滤波之后,进 行 A/D 转 换 ,将基带模拟信号转换成数字信号,由 FPGA 实 现 COFDM的解调

为了能使接收机的灵敏度达到-100 dBm,并且动态范围能达到 60 dB。综合考虑硬件电路板的体积等原因,选用了集成VGA、IQ 下变频和低通滤波器 的 下 变 频 芯 片 LT5506,并 且 输 人 信 号 范 围 为-79〜-22 dBm,满足设计要求。

由于接收机天线接收信号的动态范围是-100〜-40 dBm,考虑到信号传输的损耗,所 以 选 用 23 dB放大倍数的低噪声放大器RF3376 对 接 收 信 号 进 行 初 始 放 大 ,之后进行 IQ 下变频。由 于IQ下变频 芯 片 为 差 分 输 人 ,并且阻抗为 200 H ,为了减小信号的损耗,在低噪放之后选 用 1 : 4 的 射 频 变压 器 ,将 单 端 信 号 转 成 差 分 信号 ,同 时 完 成 阻 抗 的 转 换 。下 变 频芯片LT5506 的驱动能力弱,为 了 达 到 A/D 转 换 器 的 输 人 精 度 ,在 IQ 下 变 频 输 出 之 后 接 人 ADC驱动器ADA4940-2 提高驱动能力,此驱动器为差分输人差分输出,下一级 连 接 到 A/D 转换芯片,并且把其中一路引人到功率 检 波 器 AD8361,用 于 检 测 信 号 的 功 率 ,之后连接比 较 器 LT1783,将 输 出 信 号 的 功 率与 设 定 信 号 做差 ,比较 器 的 输 出 连 接 到 VGA 的电压控制引脚,组成反馈环路,调整信号的功率 ,使 A/D 输人信号稳定 。由于发射部分用的是双路十位 D/A 转 换 芯 片 ,所 以 接 收 与 之 对 应 选 择双 路 十 位 A/D 转化芯片 AD9 2 1 8 进 行 模 数 转 换 ,A / D 转 换 之 后 的数字信号输 人 F P G A 进 行COFDM 解 调 ,得到原始数据。

06数据传输

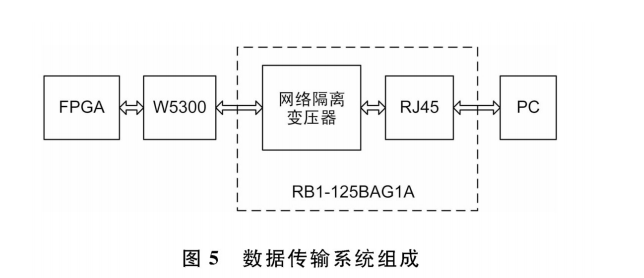

通常发射机需发射的原始图像数据,以及接收机 经 F P G A 解调之后的数据,数据量巨大,有时需要远程控制和数据传输,以太网以其成本低、易于集成和传输距离较远的优势得到广泛的应用,而利用硬件协议栈芯片实现以太网的数据传输,具有开发难度小 、集成度高且运行稳定等优势,成为本设计中的首选方案,由此设计数据传输系统框图如图5所示 。

F P G A 与 P C 数 据 传 输 ,设 计 了 F P G A 控制 W5 3 0 0 以 T C P / IP 为协议进行以太网数据传输的系统 ,其 中 硬 件 协 议 栈 芯 片 W5 3 0 0 完 成 T C P / IP 协议栈的处理[1°]。W5 3 0 0 是 W IZnet 公司的一款单芯片器 件 ,采 用0.18 pm 的 C M O S 工 艺 ,内 部 集 成 10/100 M 以 太 网控制器,M A C 层 协 议和 T C P / I P 协议栈 。

因 此 本 设 计 中 只 需 F P G A 控 制 W5 3 0 0 即可实现 网 络 协 议 转 换 ,F PG A 的网络通信。为了滤除电磁 干 扰 ,以及隔离网络上不同网络设备间的不同电平 ,保护设备,经 W5 3 0 0硬件协议转换之后,需经网络隔离变压器才能连接网络接口进行传输。为了节省 空 间 ,简化硬件电路的复杂度,选用了 U D E 公司集成网络隔离变压器的 RJ4 5 接口 R B 1-125B A G 1A 。

07测试结果与分析

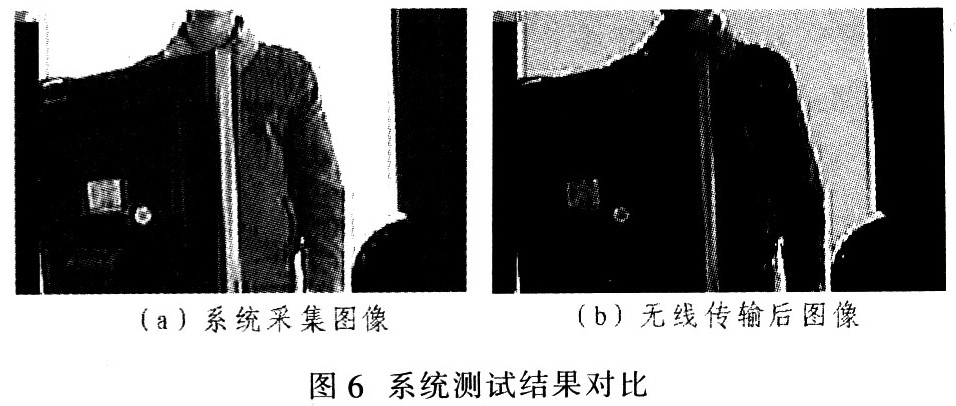

根据设计方案,实现了工程样机的研制,该硬件平 台 能 够 实 现 C O FD M 无 线 图 像 的 发 送 和 接 收 ,其中 发 射 机 的 发 射 功 率 为 1 W,发 射 频 率 可 通 过 PC 端 设 置 ;接收机的 灵 敏 度 为 -100 dBm,并且动态范围 为 60 dB,通 过 网 络 传 输 数 字 信 号 速 率 不 低 于 10 Mbps,样 机 实物如图 6 所示 。

为了测试发射和接收部分的工作性能,将板卡发射部分最终输出的模拟信号,连接可控衰减器之后 ,与接收部分的7 / 37模拟信号输人端相连,PC 端通过网络调试助手设置需要发射的数据,查看接收到的数据是否与发射的数据相同。本文中设置发射内容“数据测试”,通 过 网 口 发 送 1 0 次 ,测试结果如图 7 所 示 ,接收到的内容与发送的内容相同。

08结 束 语

根据目 前 高 质 量 图 像 传 输 信 息 无 线 传 输 的 需求 [11],提 出 的 FPGA+W5300 的 方 案 实 现COFDM 调制 解调,结 合 FPGA 实现数字信号处理的优势,以及 W5300 硬件协议栈实现网络协议的转换优点,有效地解决了图像数据传输过程中实时性、大数据量的要 求 。测试结果表明,该平台具有优越的性能,高功率发射机与高灵敏度的接收机相结合,提高了传输距 离 ,可以用于飞机、坦克等移动载体进行图像的实时传输。

审核编辑:汤梓红

-

FPGA

+关注

关注

1627文章

21685浏览量

602324 -

转换器

+关注

关注

27文章

8653浏览量

146944 -

调制解调

+关注

关注

0文章

75浏览量

21614 -

FlaSh

+关注

关注

10文章

1627浏览量

147819 -

图像传输系统

+关注

关注

0文章

5浏览量

7968

原文标题:基于 FPGA 的无线图像传输系统硬件设计与实现

文章出处:【微信号:gh_9b9470648b3c,微信公众号:电子发烧友论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

[推荐]COFDM无线图像传输系统

无线图像传输系统,求指导

基于zigbee的无线图像采集

基于FPGA+W5300与PC机TCP/IP协议通讯

ARM-v8架构分析

如何利用ARM和FPGA设计一种高速图像数据采集传输系统?

x86架构的最大特色在哪

基于 FPGA 的无线图像传输系统硬 件设计与实现

基于FPGA和W5300的以太网数据传输系统的设计与实现

一种FPGA+W5300架构的C0FDM无线图像传输系统设计

一种FPGA+W5300架构的C0FDM无线图像传输系统设计

评论