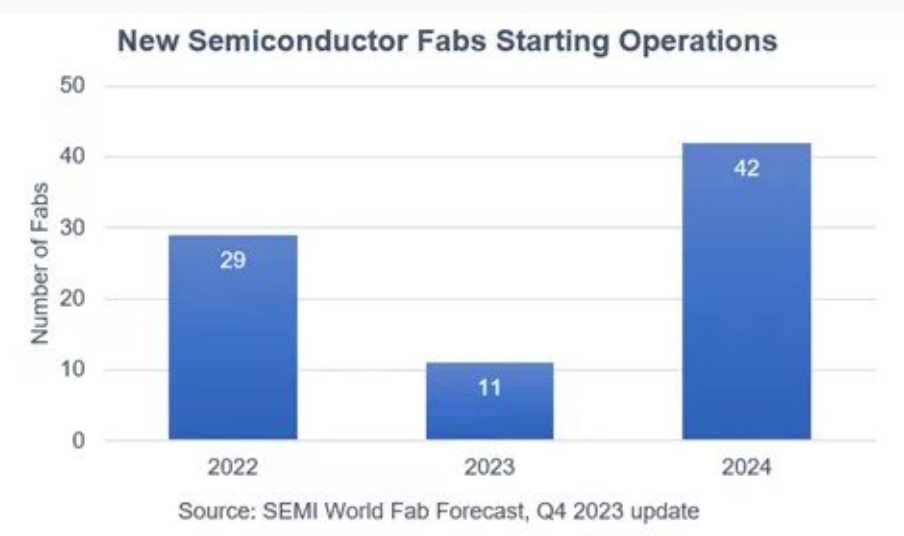

景芯SoC培训营40nm工艺,mask成本大概在60-90万美金,量产之后,每片wafer的3000-4000美金。所以前期生产4-25片进行产品验证时,主要成本就是Mask,量产时,Mask成本被平摊到每片晶圆后占比就很小了,出货量越大,占比越小。要降低芯片价格,产量至关重要。

以苹果最新的M3芯片为例,mask掩膜成本高达10亿美元,国内玩得起的 您可以扳扳手指头。

国内大部分公司都是采用40/28nm等工艺,一方面技术非常成熟,一方面成本可控,学员们不用一味追求高端工艺,毕竟国内能用7nm设计的屈指可数,而用成熟工艺的有几千家,景芯很多学员拿到的50w+ offer的也是去做的成熟工艺,这也是景芯SoC培训采用40nm工艺的原因。

但是景芯SoC训练营设计采用的低功耗设计,40nm低功耗工艺的掩膜成本为200万美元,设计先进了,功耗低了,出货量大了,工艺厂就把40nm普通mask价格从60-90万美金拔高到200万美金了,有账算啊。

40nm普通工艺mask成本大概在60-90万美金,40nm低功耗工艺的mask成本为200万美元左右;28nm SOI工艺为400万美元;28nm HKMG成本为600万美元。初创公司也不一定能cover的,初创公司更多选的90nm、130nm工艺去试水。

而芯片定价策略是8:20定价法,即mask+wafer+封测成本等为8的情况下,芯片定价为20。Intel一般定价策略为8:35,AMD历史上曾达到过8:50。一枚芯片采用8:20定价法,如何计算呢?参见知识星球。

假设产量为10万颗,一张wafer切割为2000颗,参见知识星球。硬件成本计算了,别忘记了设计成本啊,包括工程师的工资、EDA工具费用、IP费用、专利授权费用,定价失败很容易亏损。

以苹果最新的M3芯片为例,mask掩膜成本高达10亿美元,但是果粉多,出货量大,即便只出货1亿颗,分摊到每一枚芯片上,其成本也就10美元,而苹果手机多少钱一部呢?但是如果芯片的产量只有100万的话,一枚芯片的掩膜成本就高达1000美元,一部手机多少钱?想想都是恐怖的,芯片设计是赢家通吃。

【景芯SoC培训营使命】:让每个人都能设计一款MCU芯片!

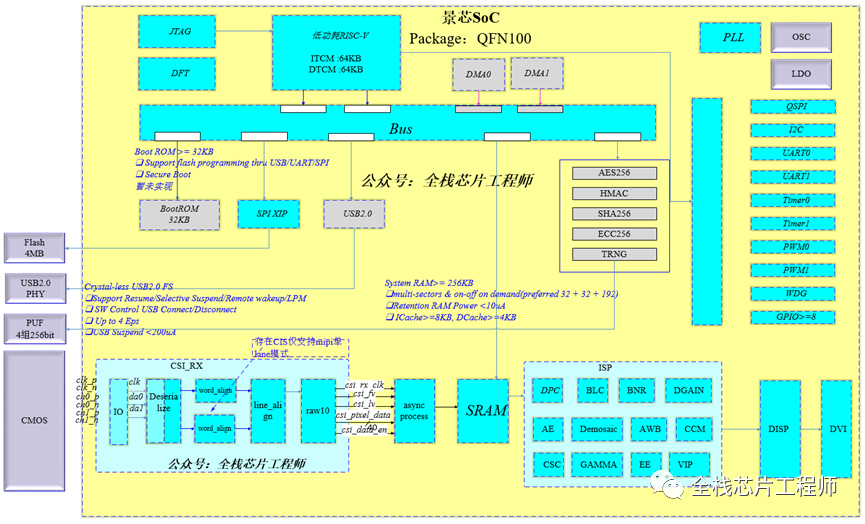

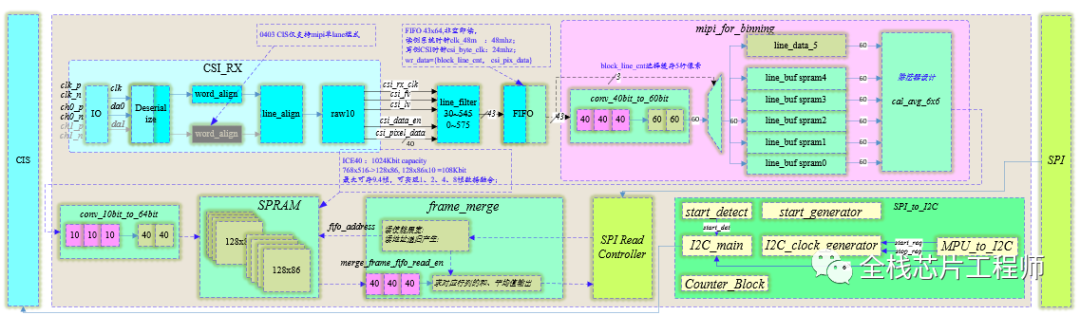

【全网唯一】景芯SoC是一款用于芯片全流程培训的低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、USB、QSPI、UART、I2C、GPIO、以太网MAC控制器等IP,采用SMIC40工艺设计流片。

ITCM: 64KB

DTCM: 64KB

外设:MIPI/USB/HDMI/UART/I2C/QSPI

系统时钟:100MHz

MIPI RX解码

ISP图像处理

HDMI接口

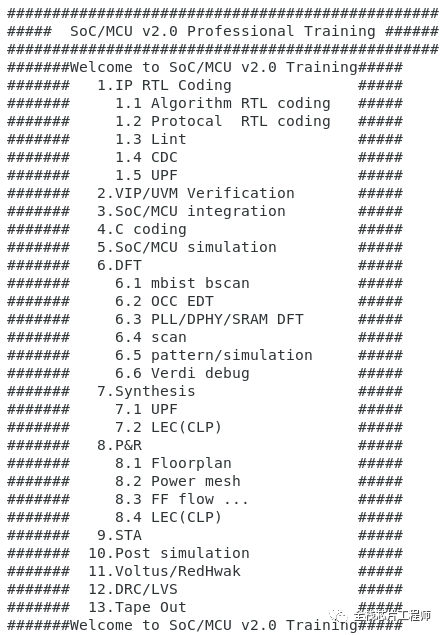

(一)SoC前端课程,您将学会

高速接口的Verilog设计实现

图像算法及Verilog设计实现

MIPI通信协议的Verilog实现

Lint、CDC检查及UVM验证

后仿真

仅前端一门课程内容就抵得上其他培训机构的5-6门课程。

(二)SoC中端课程,您将学会

DFT设计(芯片级)

Synthesis逻辑综合(芯片级)

低功耗UPF设计、CLP技术

formal验证等技术

仅中端一门课程内容就抵得上其他培训机构的4-5门课程。

(三)SoC后端课程,您将学会

布局布线(低功耗FF flow)

StarRC/QRC

STA/Tempus

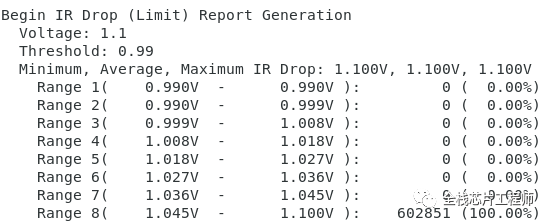

功耗分析

DRC/LVS设计

仅后端一门课程内容就抵得上其他培训机构的3-4门课程。

课程提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容,请联系号主报名,登录服务器实践,工程数据分割为如下三个部分。

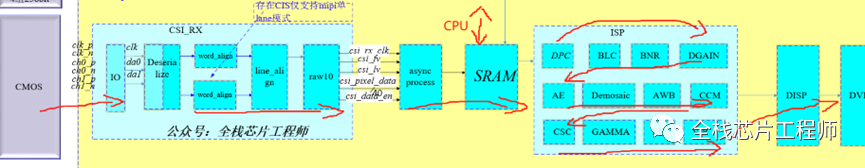

图像处理的数据通路:

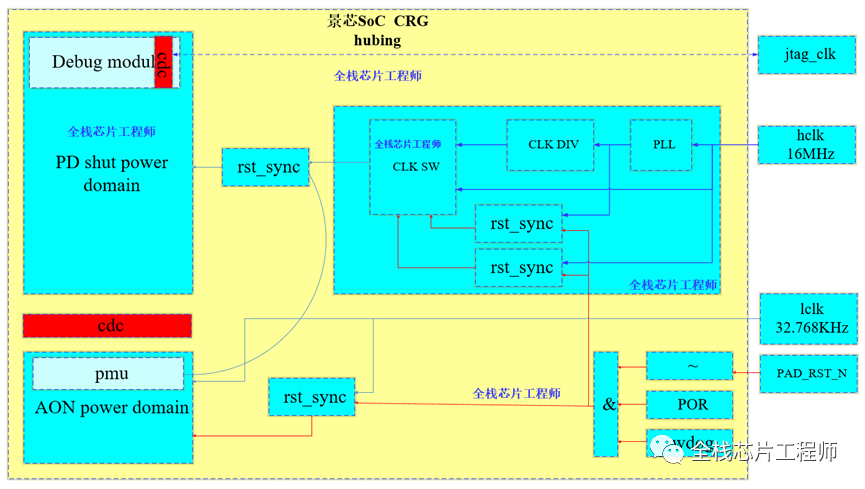

景芯SoC的CRG设计:

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、STA分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。升级后的芯片设计工程V2.0 flow如下:

SoC一键式执行flow

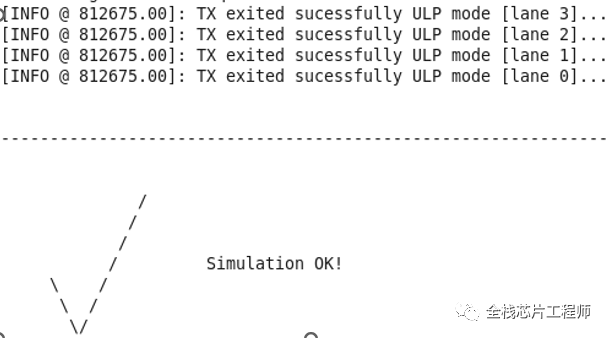

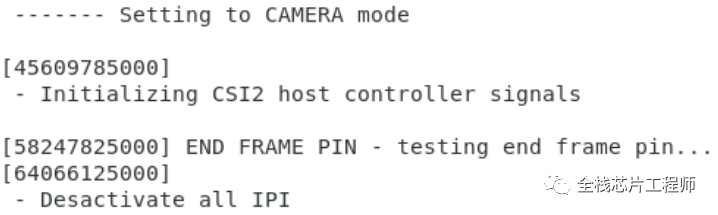

MIPI DPHY+CSI2解码

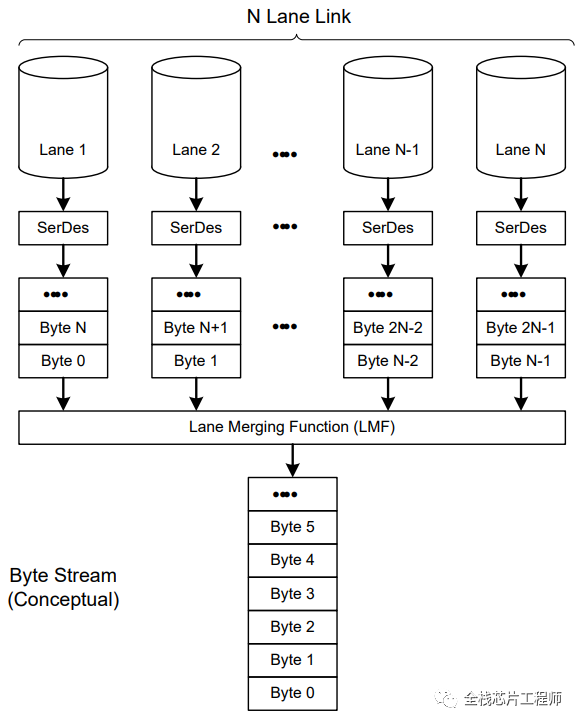

数字电路中经典设计:多条通信数据Lane Merging设计实现

数字电路中经典设计:多条通信数据Lane Distribution实现

UPF低功耗设计

全芯片UPF低功耗设计(含DFT设计)

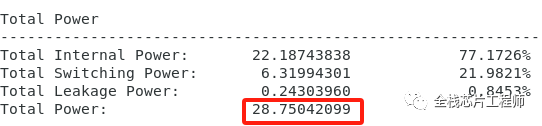

低功耗设计前,功耗为28.75W

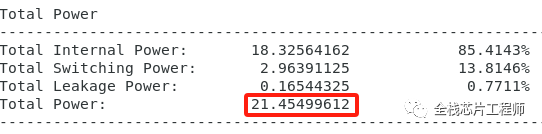

低功耗设计后,休眠时,功耗为21.45mW,降低7mW

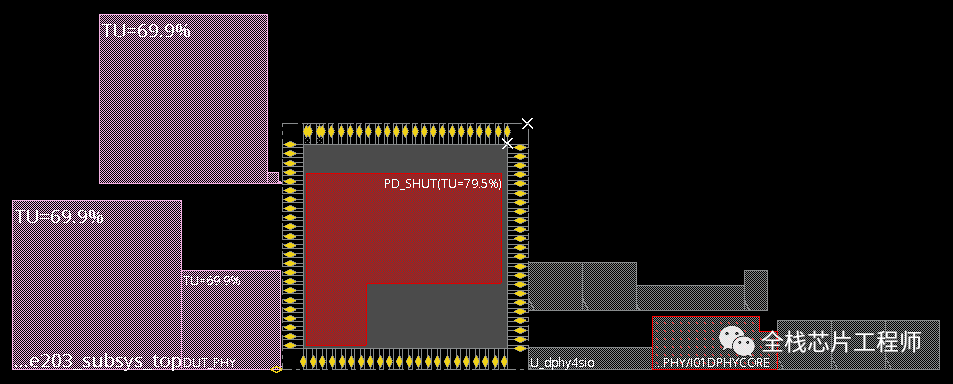

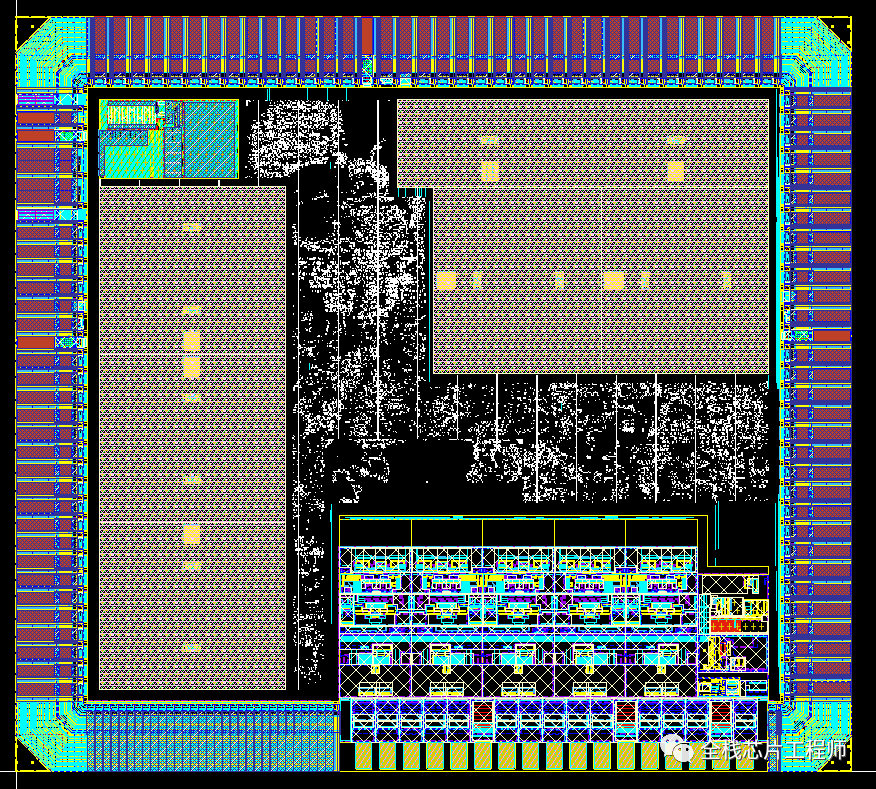

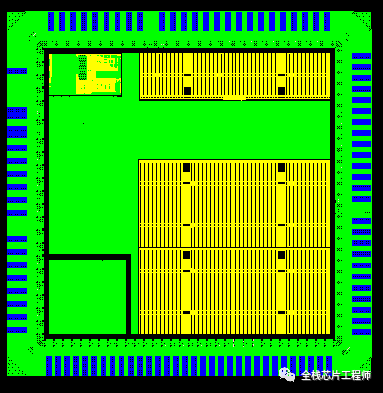

芯片的版图设计V1.0

芯片的版图设计V2.0

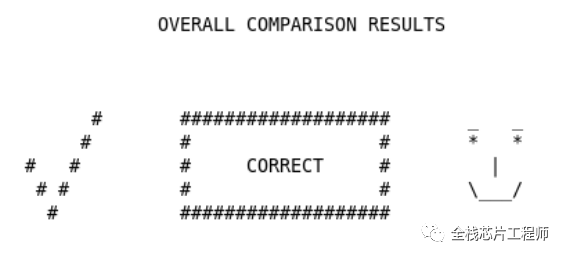

低功耗设计的DRC/LVS,芯片顶层的LVS非常具有挑战性!业界独一无二的经验分享。

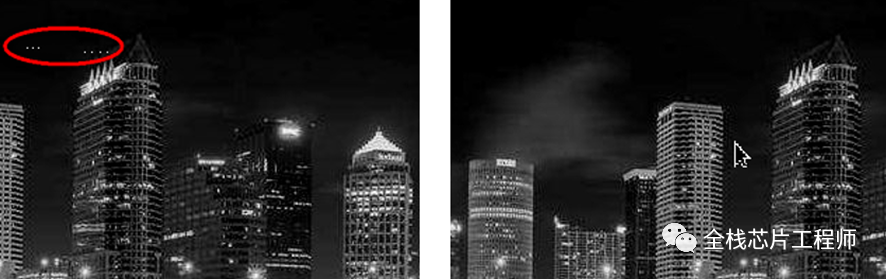

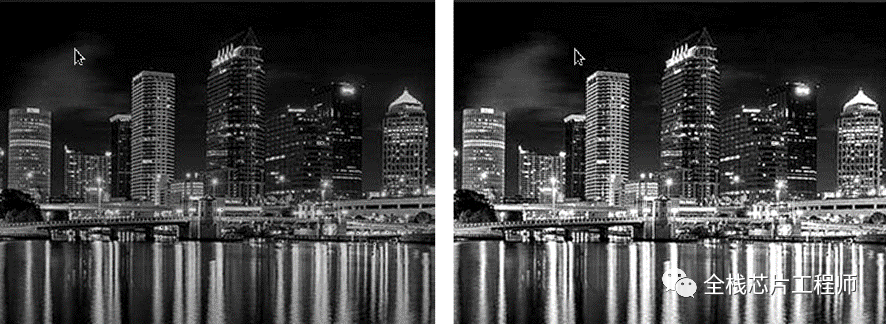

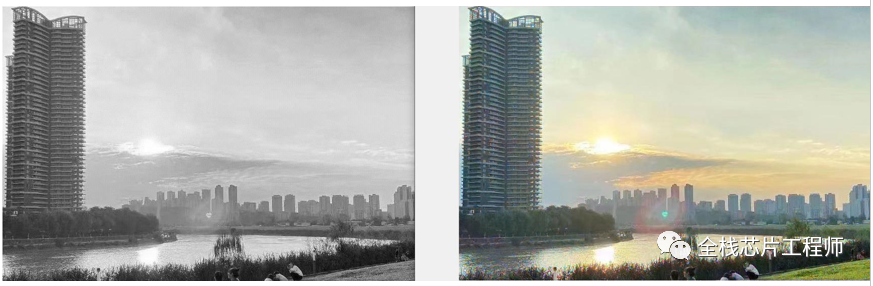

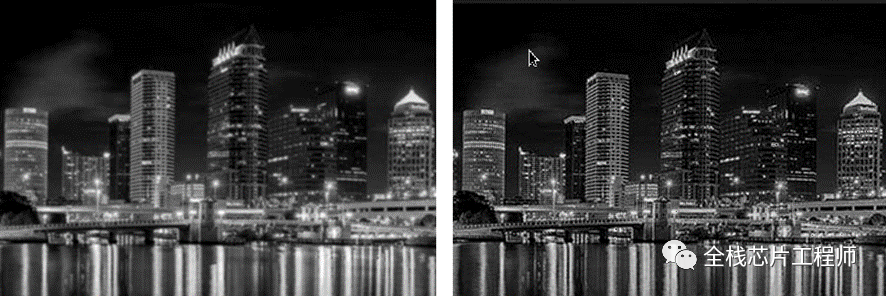

ISP图像处理

dpc - 坏点校正

blc - 黑电平校正

bnr - 拜耳降噪

dgain - 数字增益

demosaic - 去马赛克

wb - 白平衡增益

ccm - 色彩校正矩阵

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

ee - 边缘增强

stat_ae - 自动曝光统计

stat_awb - 自动白平衡统计

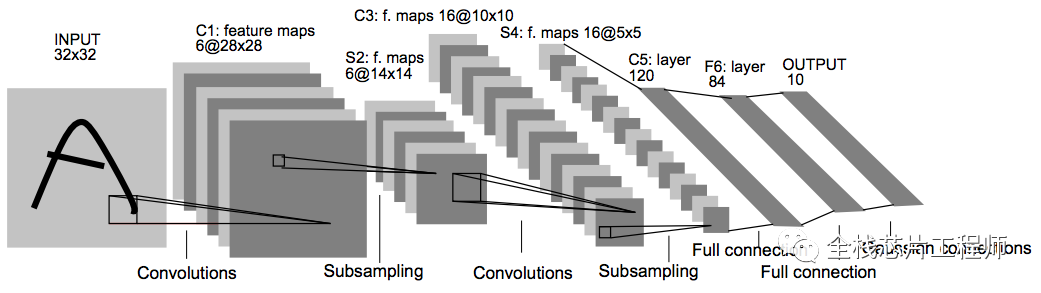

CNN图像识别

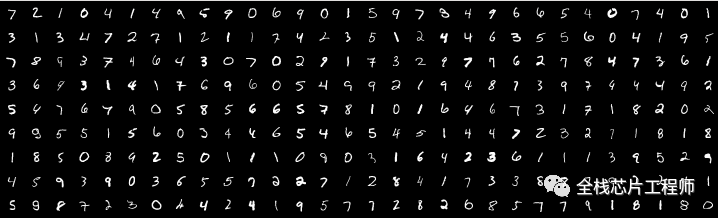

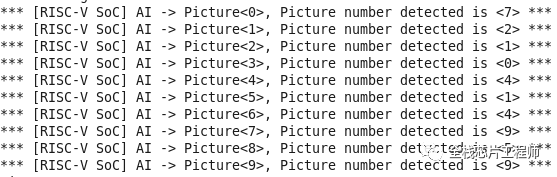

支持手写数字的AI识别:

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

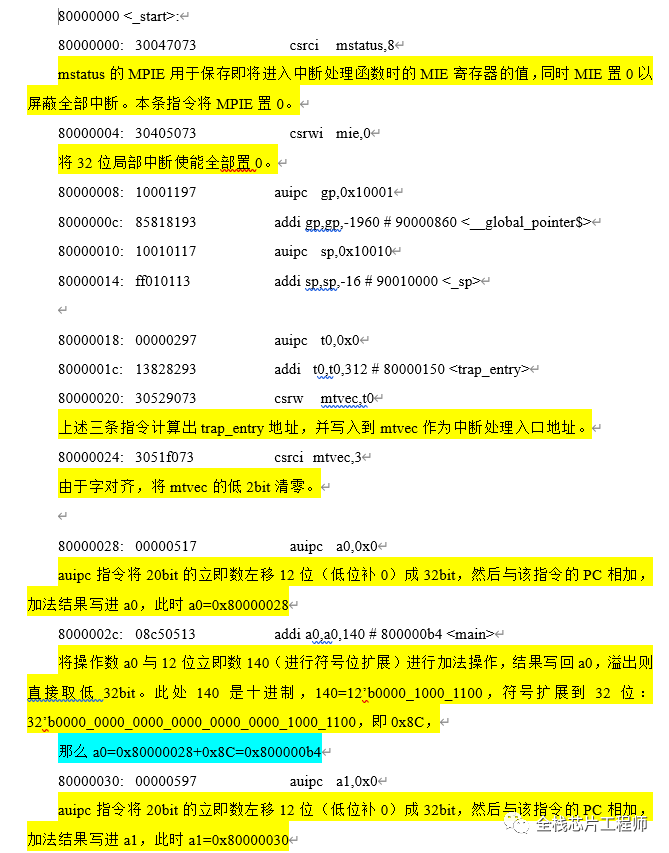

CPU启动指令分析

-

芯片

+关注

关注

455文章

50851浏览量

423913 -

mcu

+关注

关注

146文章

17162浏览量

351312 -

苹果

+关注

关注

61文章

24411浏览量

198868

原文标题:芯片花了500万投片,怎么定价呢

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电容投切开关没投为啥电容有电

方正微电子:2025年车规SiC MOS年产能将达16.8万片

昕感科技完成晶圆厂首批投片

ram芯片为什么要设置片选引脚

北京芯片独角兽芯驰科技:出货量破600万片,加速驶向全球舞台

张雪峰1600万投资的风投基金,还投了这些传感器公司

英伟达Blackwell GB200 AI芯片今年预估出货50万片

麦斯克电子年产360万片8英寸硅外延片项目封顶

三星电子NAND晶圆投片量上调约30%,谨慎对待市场发展

片上系统代表芯片吗

2024年DRAM投片量:一季度微增,下半年剧增

2024年全球半导体产能将达每月3000万片

芯片花了500万投片,怎么定价呢

芯片花了500万投片,怎么定价呢

评论