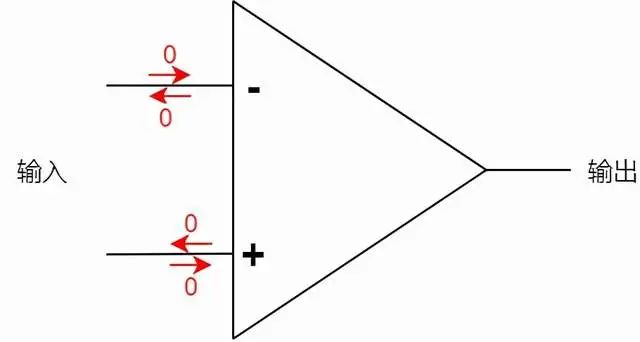

一、运放电路上的延时有哪些

1、Ts:运放的建立时间

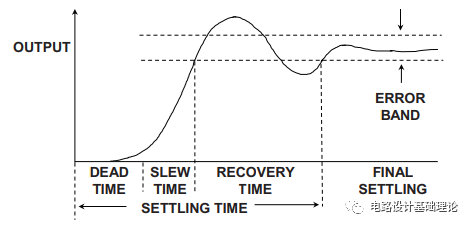

运放的建立时间主要分为两阶段,第一阶段主要是运放输出电压从初始值到达目标值附近,这阶段变化为非线性并且这段时间与压摆率有关 (压摆率的大小决定了给运放补偿电容充电的快慢),第二阶段是输出已经接近目标值了,这阶段变化为准线性,主要受运放的零-极点影响;在高速运放中,第一阶段的时间很短,主要的建立时间都受第二阶段影响。

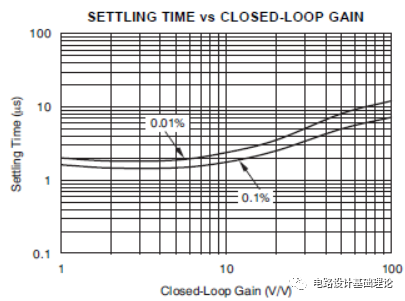

根据运放的特性来看,运放的建立时间会受大信号-压摆率,小信号-闭环增益影响

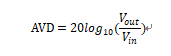

根据GBW=G*Freq,当闭环增益变大时,Freq就会变小,进而导致输出误差的环路增益(AolB)变小,从而影响运放建立时间变长。

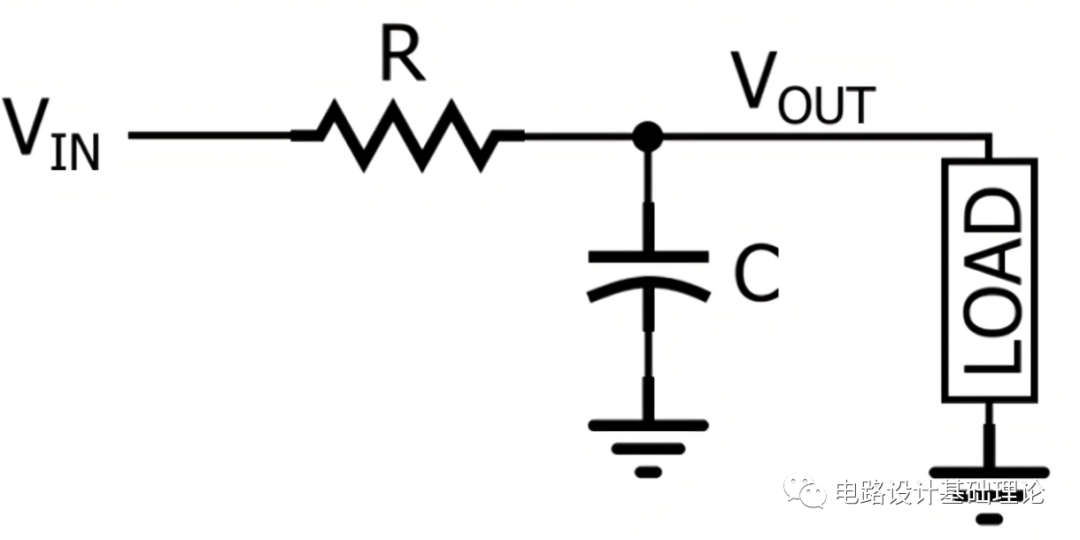

2、Trc:RC滤波电路延时

RC低通滤波器用于防止震荡电路,这种设计通常被应用于输入端以及输出端 通过电容充放电的反应时间来使信号稳定不变但同样也使信号下降延迟了时间 。

二、如何选取合适的参数

1、运放的参数选取

影响到运放建立时间的主要参数为压摆率、增益带宽积两个参数

压摆率:Slew rate

SR=2ΠFreqVp

增益带宽积:gain-bandwidth product

GBW=G*Freq

选择运放时我们也应该注意以下两点:

失真特性:对于ADC的驱动运放来说,我们通常需要选择输入输出轨对轨的运放,防止不必要的输出失真。

噪声特性:对于运放的噪声特性来说,为了不让运放的噪声对ADC的精度产生影响,一般会使运放的总噪声在ADC噪声的1/5左右。

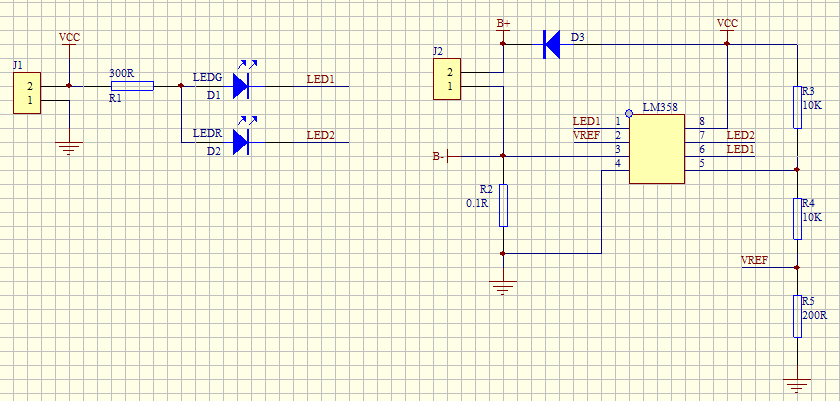

2、rc参数选取

运放rc滤波分为输入滤波与输出滤波

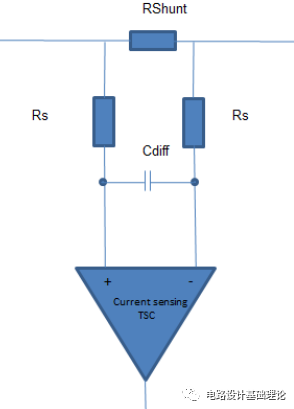

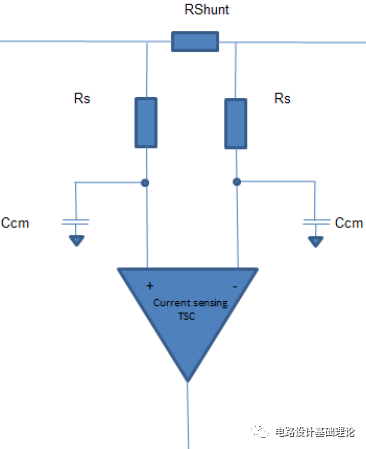

a:差模滤波:

F=1/(2Π2Rs*Cdiff)

b:共模滤波:

F=1/(2ΠRs*Ccm)

以上两种输入滤波电路根据信号频率选择合适的参数即可,本文不过多介绍,有些电路可能应用差-共模滤波电路,主要注意Cdiff容值要大于Ccm,平衡Rs1-Ccm1、Rs2-Ccm2时间常数不匹配带来的影响,一般取值Cdiff=Ccm*10

c:输出滤波:

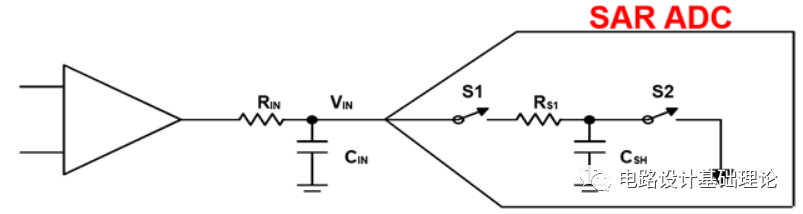

该图为常见的SAR-ADC结构,针对该结构展开如何设计RC电路,首先RC电路在该结构中的作用有两部分:

1、是对ADC的Csh进行充电,由于ADC采样保持阶段需要给采样电容Csh充电。开始采样时,Csh的电荷由输入部分和RC滤波电容提供,保证在一定时间内达到精度的要求。显然,随着采样精度和采样率的不断提高,驱动ADC的难度加大,因为必须在有限的时间内将Csh上的电压达到满足精度要求。所以我们在ADC前加入电容,当采样保持阶段时对Csh进行充电,保证采样的精度。电阻则作为隔离作用,避免运放直接驱动容性负载,提升系统的稳定性。

2、RC网络同时也限制了输入信号的带宽,并且降低了运放带来的噪声量,但是此时,带宽的限制会使信号的延长建立时间,引起信号的失真。

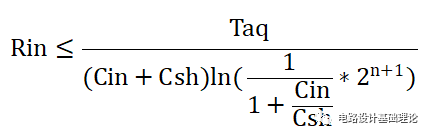

基于以上两点我们设计RC的目标就是在有限的的时间内将Csh上的电压满足精度要求。

Tap:采集时间、n:ADC采集位数

Cin选取参考MCU内部的采样电容(sampling capacitance),一般取值为采样电容的20倍左右。

-

运放电路

+关注

关注

38文章

361浏览量

34978 -

滤波器

+关注

关注

161文章

7859浏览量

178897 -

adc

+关注

关注

99文章

6533浏览量

545693 -

运放

+关注

关注

47文章

1169浏览量

53262 -

滤波电路

+关注

关注

46文章

639浏览量

69819

发布评论请先 登录

相关推荐

TINA仿真运放电路时,运放的参数中是否可以增加温度参数呢?

从零学运放—02怎样分析运放电路

揭开运放电路神秘面纱:如何选型运放?

什么是运放 反相比例运放电路图

运放电路上的延时有哪些 运放如何选取合适的参数

运放电路上的延时有哪些 运放如何选取合适的参数

评论