一、概述

晶振是有源晶振的简称,又叫振荡器。英文名称是oscillator。

晶体则是无源晶振的简称,也叫谐振器。英文名称是crystal,电路上简称为XTAL。

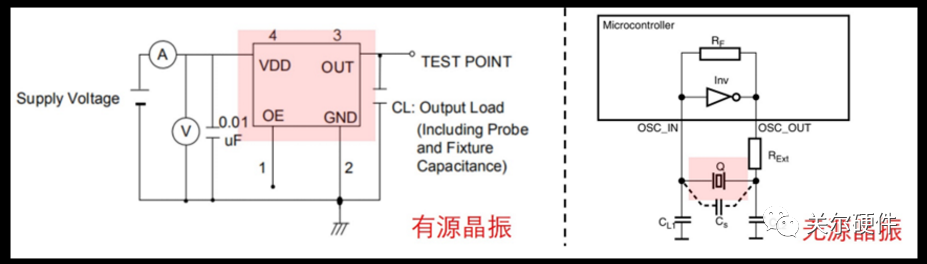

有源晶振(晶振):内部有时钟电路,只需供电便可产生振荡信号。

有源晶振内部是包含了一个无源晶振,然后再将阻容、放大等电路也包含进去。

晶体单元的特性取决于切割工艺,不同的切割方式决定了晶振的性能或参数,主要有三种:

音叉型(Turning Fork):频率主要是KHz级,比如32.768KHz;

AT-Cut型:频率主要是MHz,比如12MHz、26MHz、125MHz;

SAW型:频率为百MHz、甚至GHz。

石英晶振结构图:

晶体振荡原理是压电效应:

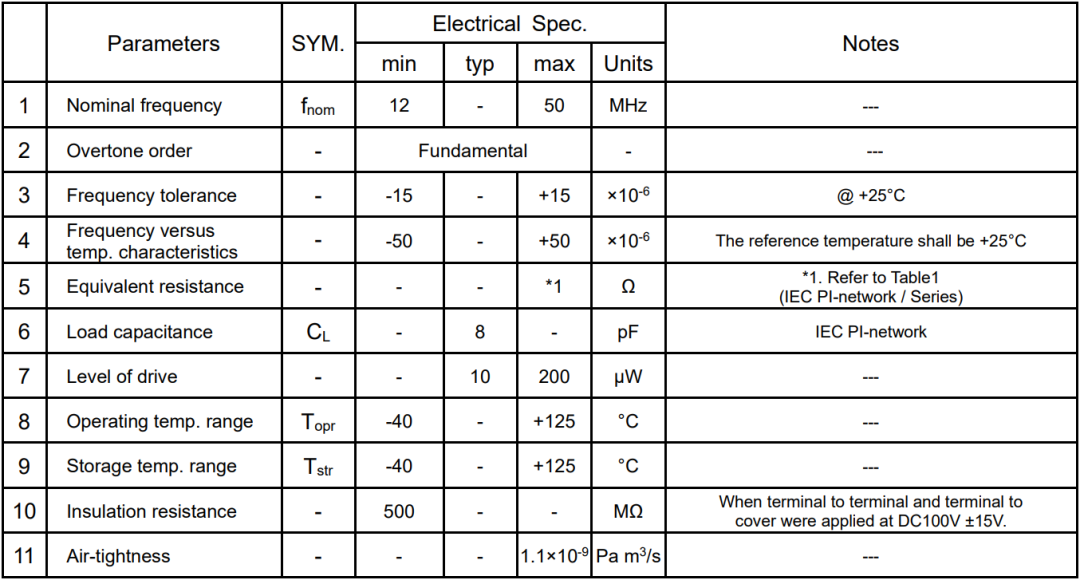

二、参数

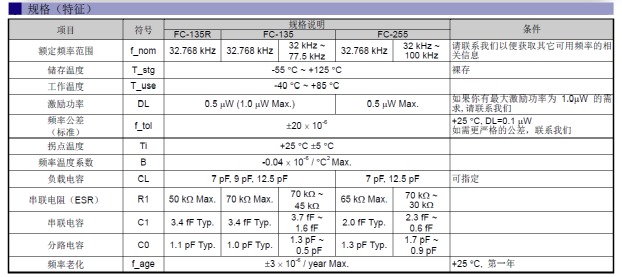

标称频率(Normal Frequency) F0:电路设计上所需的实际频率。

振动模式(Mode of Oscillation):按照切割工艺来划分的。

负载电容(Load Capacitance)CL:在电路中跨接晶振两端总的外界有效电容;要等于或接近晶振数据手册给出的数值才能使晶振按照预期工作;比较通常使用的24MHz晶振负载电容是20pF;

静态电容C0:以石英晶片为介电材料和两个电极之间的电容;很多晶振规格里是<3pF的;

等效电阻:晶体上的等效ESR。

调整频偏(Frequency Tolerance):在确定的负载电容下,振荡频率的偏差。

频偏:常温频偏+温度频偏<芯片要求频偏。

温度频偏(Temperature Tolerance):高温时所带来的频率偏差。通常有温度要求的,要选用10ppm。

激励功率:振荡需要的功率。主控端的输出激励功率不能太大,正常会串电阻,防止给到晶体的激励功率偏大,造成晶体的损坏。

老化率:随着使用时间,频偏会加大。

三、设计电路

Xin和Xout的内部一般是一个施密特反相器,反相器是不能驱动晶体震荡的。因此,在反相器的两端并联一个电阻,由电阻完成将输出的信号反向180度反馈到输入端形成负反馈,构成负反馈放大电路。

Rf:反馈电阻(主控端内置或外接);

Rd:限流电阻(预防晶振过驱,限制振荡幅度);

Cg和Cd:负载电容;

电路中负载电容计算法:

CL=Cg*Cd/(Cg+Cd)+CPAR

Cg、Cd:负载电容;

CPAR:电路布线杂散电容及引脚寄生电容(2pF---9pF)。

输出频率F与寄生电容是反比的:

当电路中心频率偏大时,说明负载电容CL偏小,增加Cg、Cd容值。

当电路中心频率偏小时,说明负载电容CL偏大,减小Cg、Cd容值。

四、负阻

4.1 负电阻

英文:Negative Resistance

英文简称:– R

单位符号:Ω

负电阻不是晶振的内置参数, 但却是振荡线路设计时,很重要的性能指标。

是电路放大器(AMP)注入能量的大小用电阻来表示(是提供功率的器件,相当于激励源)。

是保证振荡器稳定振荡并具有一定余量的重要指标。

是用阻抗表示的振荡电路信号放大能力。

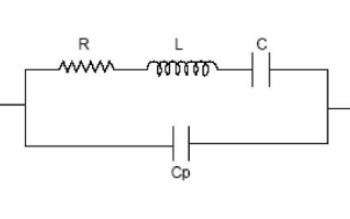

4.2 等效电路

在石英晶体振荡状态下,从石英振荡体的两端看振荡回路时,能以等值输入电容Ci和等值输入电阻-Ri的串联回路来表示,而石英晶体本身则成为等值的有效电感LL和有效电阻RR的串联回路。

4.3 测试负阻方法:

量测负性阻抗:输出端串接一个可变电阻,可变电阻调至最小,上电源让电路正常动作,调整可变电阻,将之调大,直至振荡器不起振,确定不起振后,再将可变电阻转小,观测波形,持续将可变电阻调小到振荡器开始振荡波形正常后,关闭电源,再打开电源,若振荡器依旧可以起振,这时候可变电阻上的阻抗值再加上仪器所测得振荡器单体的电阻值即为负性阻抗值。

若要获得稳定的振荡电路,振荡电路IC的负电阻值(-R)至少为晶振的5倍以上,即绝对值|-R|>5R。举例来说:如果晶振电路阻抗总值为30Ω,那么IC的负电阻值需要至少在-150Ω,这样才能有效保障振荡回路的稳定性。

若负性阻抗的能量源大于振荡电路的损耗时,能源回路为平衡状态,此回路为稳定振荡,负性阻抗不是产品规格参数,但却是振荡线路设计时很重要的性能指针。

负性电阻振荡器模型:

振荡器描述为负性电阻 (Rn)、电路电抗 (Xc)、谐振器电抗 (XR) 和谐振器电阻 (RR) 的组合。当Rn>RR时,电路将以使Xc=-XR的频率振荡。

4.4 负阻调整

调整负载电容CL大小;

选用内阻较小的晶振;

修改电路上的其他参数,增大电路负性阻抗;

五、激励功率计算及测试

有两种办法可以用来计算晶振的激励功率:

5.1 通过电流计算

DL = ESR x (IQ)^2, IQ表示通过晶振电流的有效值, 通过示波器如下测量电流 ,如果过大的话, 则需要增加Rext电阻进行限流, 测量电流的话,晶振引脚空间小,不好操作。

5.2 通过电压计算

电流IQ(RMS) = 2 π F x VRMS x Ctot,因此,可以通过电压来计算激励功率。通过示波器测量晶振引脚的Vpp电压,及相应示波器探头的电容Cprobe, 晶振的外部负载电容CL1。

计算公式如下:

六、晶体Layout

6.1 不能放置在板边

如下图所示,如果产品的晶体置于板边,DUT产品的高速器件就会与实验台的参考接地板形成一定的电场,且寄生电容的存在,出现共模辐射,寄生电容越大,共模辐射也就越强。

下图左边的电场被板子隔开,不会产生很强的辐射。

虽然晶体是辐射源头,但是晶体影响的是近场辐射,造成EMC测试的远场辐射的直接原因是电缆或产品中最大尺寸与辐射频率波长可比拟的导体。

6.2 邻层挖空处理

主要有两方面原因:

a)邻近晶体的铜皮会与晶体之间,形成电容器,即寄生电容,影响到晶体的负载电容计算。当然,只要实际测试晶体频偏没有问题,这个寄生电容不影响到可靠性。

b)邻近晶体的铜皮会产生热,热会影响到晶体的频偏(温度频偏)。在手机电路设计方面,会在晶体正下方挖空两层,起到隔热传递。

七、案例

7.1、高温导致频偏大;

WIFI模组的尺寸比较小,发送数据过程中,功率比较大,WIFI模组上的温度就比较高,就会导致WIFI模组上40MHz无源晶振频率偏差变大。这种情况下,只能更换温度偏差10ppm的物料。

另,WIFI的频偏要求比较高,正常要选用频率偏差10ppm的。

7.2、负阻电阻过小,导致概率开机有问题

某机器在可靠性开关机测试时,小概率的1%左右开不起来的现象。热风枪加热测试,不开机概率增加,负性阻抗是120欧姆,而晶体的内阻是50欧姆,也就是负性阻抗偏小,晶体振荡不稳定。设计电路上的Rd改为100欧姆,测试的负性阻抗由250欧姆,重新老化开关机测试,测试OK。

7.3、辐射超标

某个产品在做EMC测试时,160MHz出现超标,是板子上16MHz晶体的倍频。从板子上,16MHz晶体放置在PCB板上边缘。解决方案:a)16MHz晶体往板子里面移动;b)在晶体四周做guard ring,起法拉第电笼作用。

(法拉第电笼:由金属或良导体形成的笼子。可防止电磁场进入或逃脱笼子。原理:根据接地导体静电平衡的条件,笼体是一个等位体,内部电势差为零,电场为零,电荷分布在笼体的表面。)

-

振荡器

+关注

关注

28文章

3831浏览量

139017 -

有源晶振

+关注

关注

1文章

887浏览量

20580 -

无源晶振

+关注

关注

1文章

829浏览量

15935 -

晶振

+关注

关注

34文章

2856浏览量

67994

发布评论请先 登录

相关推荐

晶振概述、参数及原理

晶振概述、参数及原理

评论