前面星球分享了在ICC2里面直接调用ICV signoff DRC与修复DRC的教程,今天Innovus读入Calibre DRC报告自动做修复的教程来了。

某些DRC在Innovus里面检查可能没有问题,但是到了Calibre/ICV检查可能发现有DRC问题。有以下几种可能性:

1. 可能是你在Innovus里面检查DRC的命令有问题,bypass了某些检查,可以仔细检查一下你check DRC的命令和option,保证没有问题;

2. 可能是Cell LEF和GDS有mismatch,可以对比Innovus和GDS里面的同一个地方的metal shape看看是否有差异,是否是Cell LEF有问题,有问题的话可以修改Cell LEF,然后更新Innovus里面的Cell LEF,然后检查DRC,再ecoRoute -fix_drc,如果数量非常庞大,工具修复不掉的话可能要回到Route重新绕线。

3. 如果前面两种问题都不存在,只是Innovus里面没有相关的Rule(Innovus的Rule是很难将Signoff DRC的Rule全部包含在里面的,也无法做到完全一样的Check,因为PV的Rule是很多很复杂的,尤其是先进工艺下),没办法检查出来的话,分以下几种情况去处理:

a) 如果是PG上的DRC,可以去修改PG plan的时候上面的一些参数,比如PG的宽度,Via的种类等去修复;如果不是的话继续往下看:

b) 如果这种错误非常多的话,可以向Foundary反馈,也可以自己尝试去tech LEF里面添加这种Rule。

c) 如果问题非常少,在几个到十几个的数量级内,那么可以完全手工搞定;

d) 如果数量不少,但是也不是非常多,比如在几十到几百的范围,那么也可以向Foundary反馈,如果他们能提供修改后的tech LEF的话那自然是好的,如果没办法优化tech LEF了(一个刚开发的新的工艺节点很容易有这种问题),或者时间进度比较赶的话就可以用到这个教程的内容了,我们可以在Innovus里面加载Calibre的DRC结果,让Innovus去自动修复这些DRC。方法如下:

为了加快Calibre DRC检查的速度,可以把一些规则比如Density检查的Rule关掉,或者只勾选一些关心的Rule进行检查。检查完毕之后:

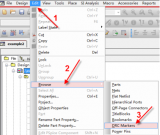

innovus中load drc results并自动fix,命令如下:

Legacy UI:

loadViolationReport -type Calibre -rulemap rule_map.txt -filenamecalibre_drc.rpt

route_fix_signoff_drc

对应的CUI:

read_markers -type Calibre -rule_map_file rule_map.txt calibre_drc.rpt

route_fix_signoff_drc

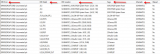

rule_map.txt示例如下:

...

‘route_fix_signoff_drc’命令支持的DRC类型有:

...

这个命令无法解决的DRC违反有以下几种:

...

编辑:黄飞

-

DRC

+关注

关注

2文章

148浏览量

36158 -

Calibre

+关注

关注

0文章

18浏览量

9746 -

Innovus

+关注

关注

1文章

20浏览量

2668

原文标题:Innovus教程 - 读入并自动修复Calibre DRC

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎样去改用calibre过DRC时的错误?

基于calibre的MIC总线控制器专用集成电路版图检查

Laker & Calibre Bandgap 实例教程

Intel晶圆代工厂扩展服务利用 Calibre PERC做可靠性检查

Mentor Graphics 推出针对 Tanner 模拟/混合信号 IC 设计环境的 Tanner Calibre One 验证套件

EDA明导国际Calibre平台已支持最新的TSMC 12FFC制程设计

到底谁能提升Calibre的效率?

Calibre DRC报告自动做修复的教程分享

Calibre DRC报告自动做修复的教程分享

评论