在进行模块设计时,我们经常需要统计报文的数量,以供软件(or 主机)读取,有些统计仅仅用于debug,有些统计是协议要求,有些统计是为了便于功能实现。 当需要统计的数量较多时,为了降低功耗和减少面积,我们通常采用RAM去实现。

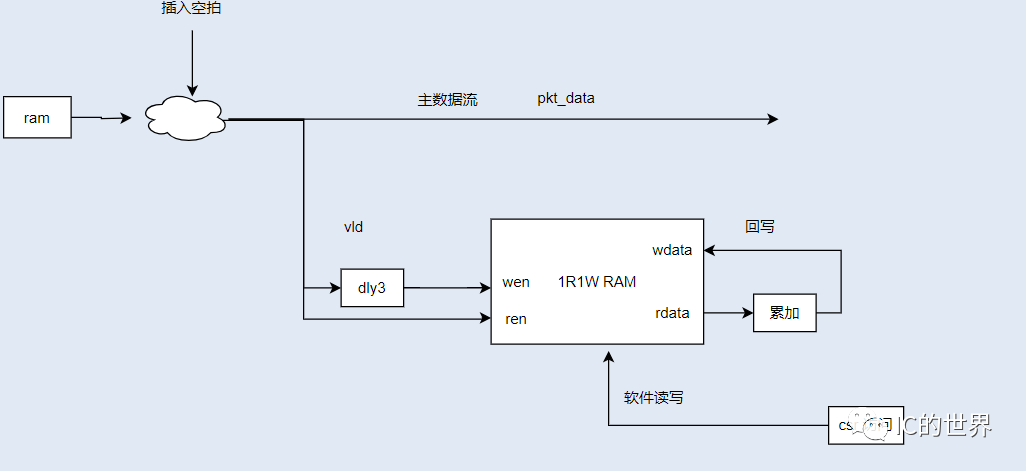

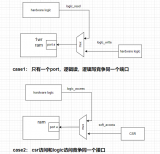

如下案例中,统计有效数据包的个数。 假设数据中存在pkt_id,pkt_id为0~63,则ram的深度为64。pkt_id用于作为读写地址。RAM读延时为3个时钟周期。 有数据来临时,pkt_vld作为读使能,读出当前包计数rdata,三个周期后,rdata加1回写到ram。 如下图所示:需要有三个注意事项 NOTE1:需要有读写保护,因为可能出现连续4个周期内,pkt_vld为1,且pkt_id相同,此时会出现同一个周期对相同的地址进行读写,因此需要RAM需要添加读写保护模块,保证数据能够正确写入,且读出的都是最新值,否则就会出现统计错误。 NOTE2:图中既有软件读、又存在硬件读,且硬件读优先级更高,软件读优先级低,因此为了保证软件读能够在有效周期内得到响应,因此需要在主数据流上插入空拍,避免出现软件读长时间无法响应而产生超时。

编辑:黄飞

-

IC设计

+关注

关注

38文章

1294浏览量

103897 -

RAM

+关注

关注

8文章

1368浏览量

114630 -

读写保护

+关注

关注

0文章

4浏览量

5868

原文标题:IC设计:ram的应用 - 统计计数

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于QMSS中link ram的地址问题

关于Ram on Net的设想

屏幕自动刷新RAM和负液晶技术的介绍

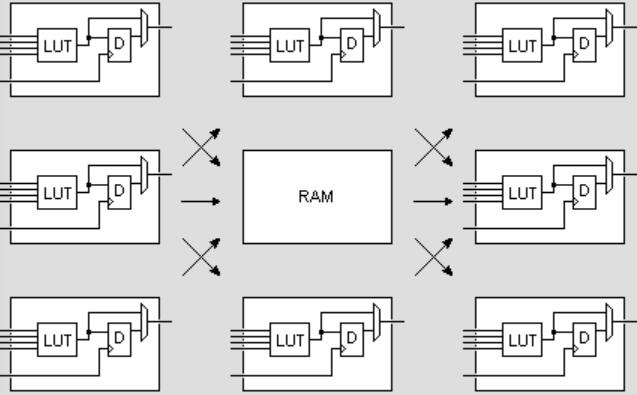

详细介绍关于FPGA开发板内部ram是如何操作的

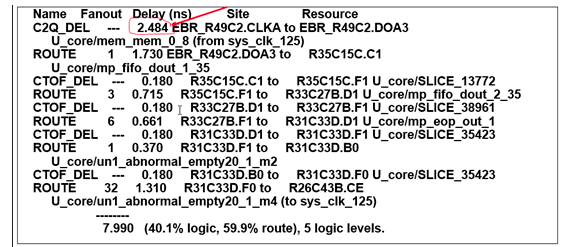

关于Block RAM的寄存器输出

在STVDCOSMIC在RAM中运行代码stm8 ram中运行程序

关于RAM以及单片机内存少的几点内容

关于dsp28035的adc在ram中运行和rom中运行的问题

IC设计中关于ram的应用

IC设计中关于ram的应用

评论