1 简介

泄放电路就是将一部分电能转换成热能或者其它形式能量的电路。相信大家应该都有碰到过下面这些问题:

单板下电但是LED依然未熄灭。

通过示波器测试单板下电波形,显示掉电速度十分缓慢。

今天主要就是解决这个两个问题。

2 应用场景

泄放电路即放电电路,主要应用在以下两种场景:

用在需要快速反复开关电源。

负载电路上有大容量电容的场景。

分析 :断开电源开关后,如果负载电路有大电容,会引起负载电路上的电压下降缓慢。此时如果重新接上电源开关,负载电路在未完全掉电的情况下重新上电,可能会导致电路不能正常复位启动,进而电路工作异常,出现开机死机等情况。

3 泄放电路设计

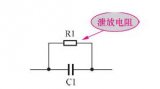

电阻实现泄放电路

下电时,大电容储存电能通过10KΩ直接泄放到地平面。

优点:电路设计简单,仅需一个电阻就能满足设计要求。

缺点:功耗增加,不满足低功耗要求,且泄放效果不明显。

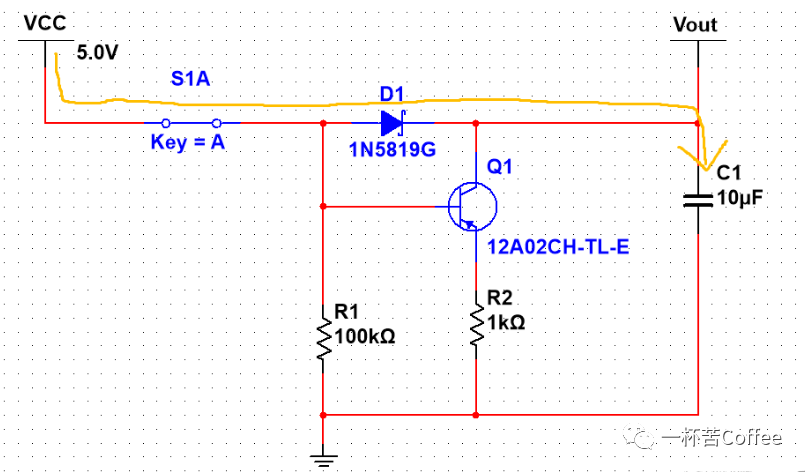

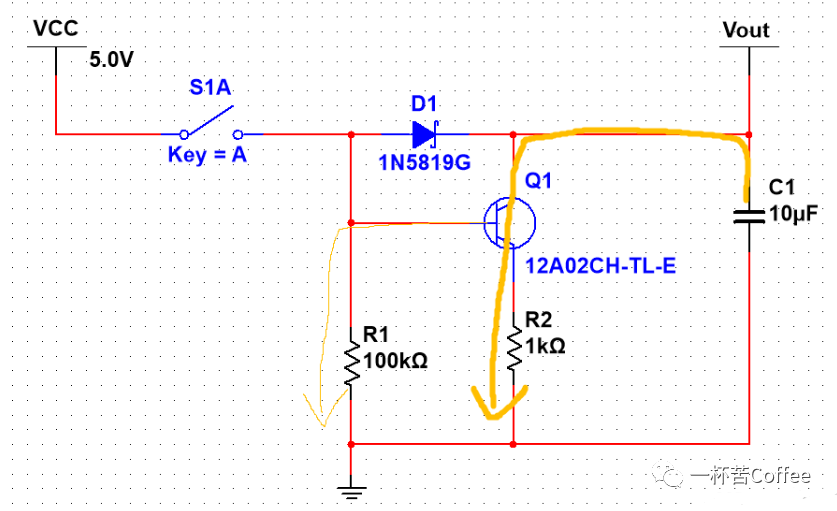

三极管实现泄放电路

上电过程

上电瞬间,三极管的基极b为高电平,VCC通过D1给板卡正常供电,三极管Q1截止,VCC通过D1给C1进行充电。

下电过程

下电瞬间,三极管Q1的基极b被电阻R1拉低,D1由于其单向导电性,相当远断开,电流从Q1的集电极流向发射极,最终构成回路。注意电阻R2的阻值不宜过大,否则会影响泄放的速度。

优点 :这种方式电路泄放效果好,泄放回路不需要经过电源IC,极大地提高了电路的可靠性。

缺点 :如果前级VCC的下电较慢,可能会导致后级VOUT下电减慢。

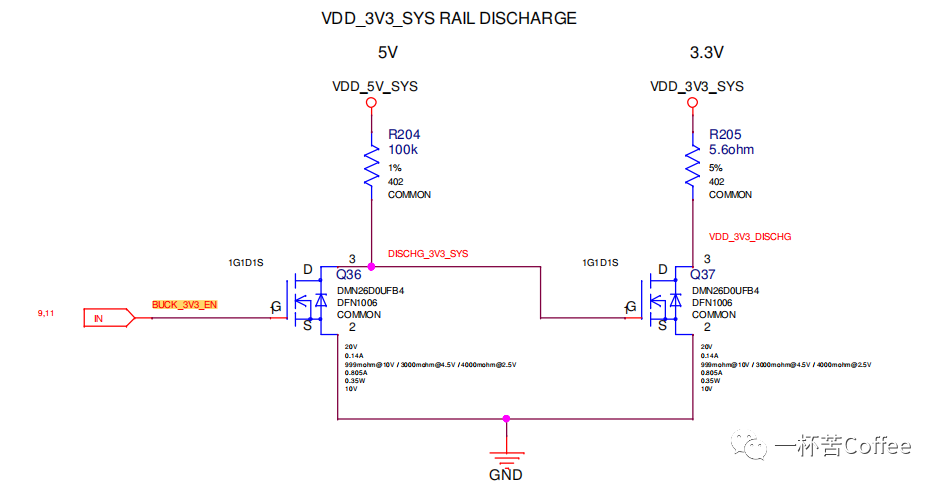

单片机实现泄放功能

这种泄放电路设计是在英伟达的官网参考设计上面看见的,没有使用过, 优点与缺点暂不评论。

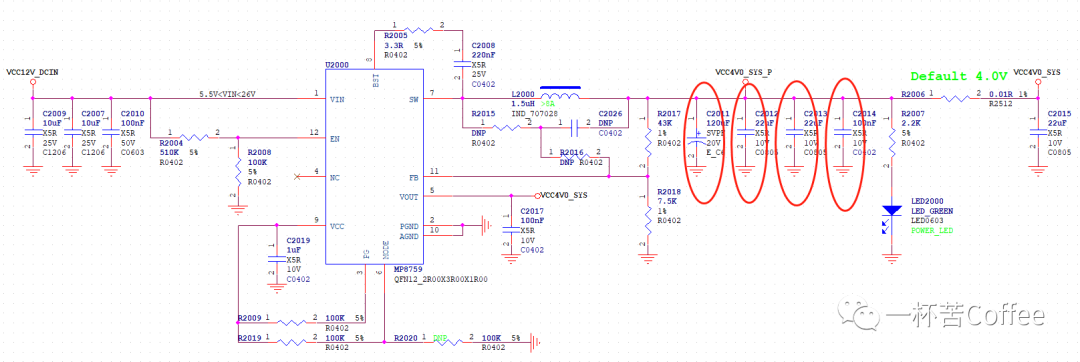

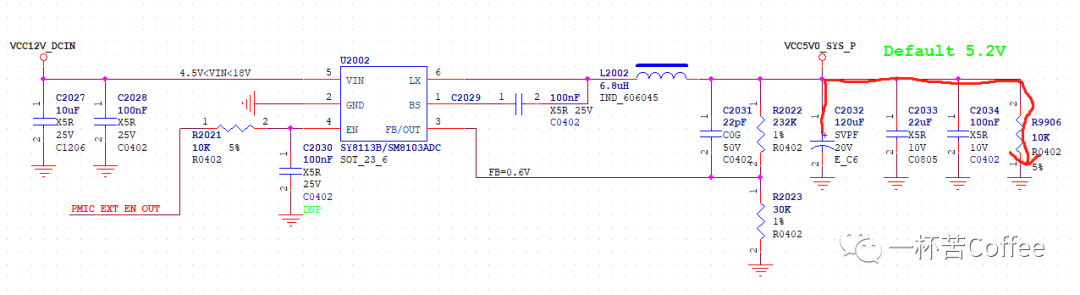

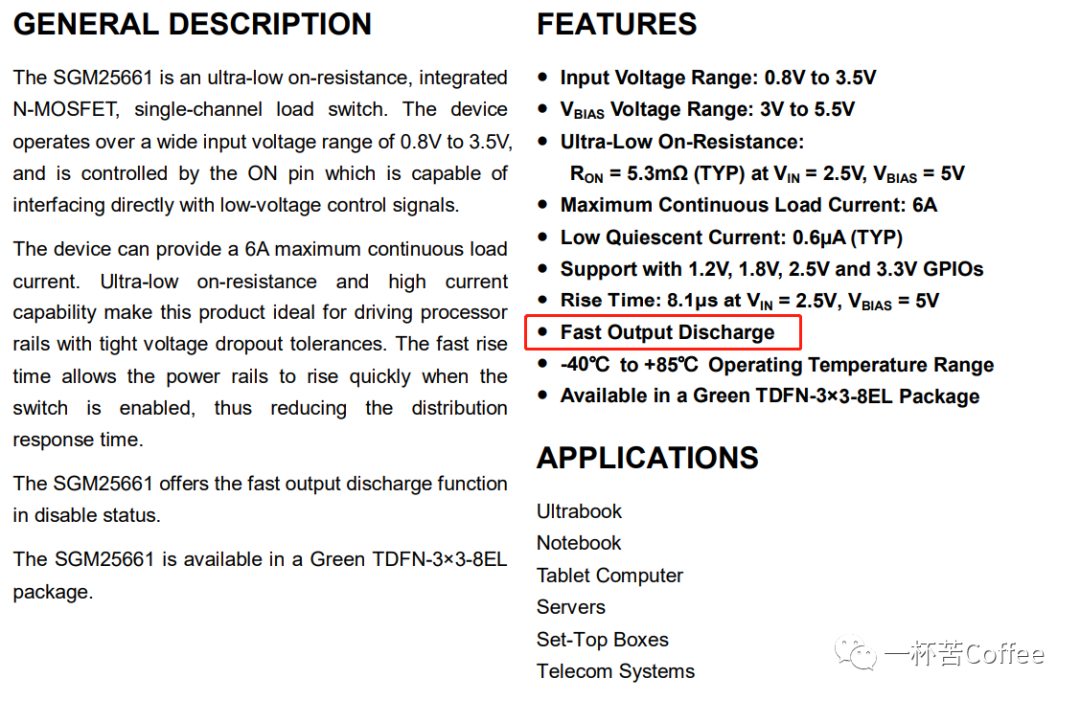

带泄放功能电源芯片

此处介绍的芯片是SGM25661,输入电压范围0.8~3.5V,输出电压为1.2V、1.8V、2.5V和3.3V,最大的输出电流高达6A,且支持快速放电功能。

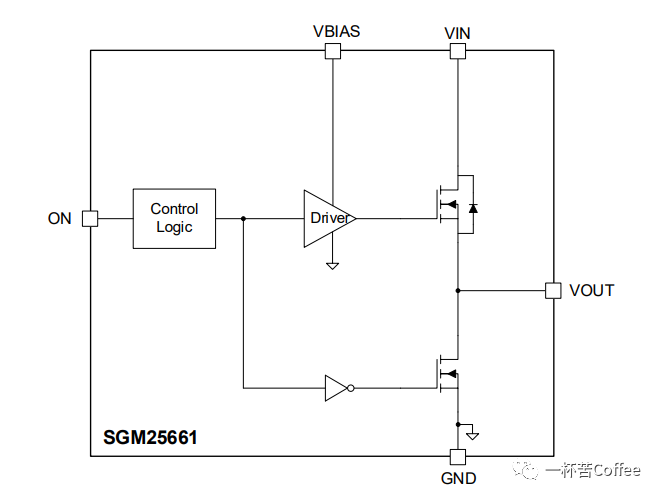

SGM25661的内部结构见下图:

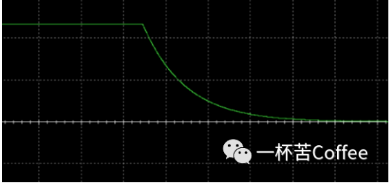

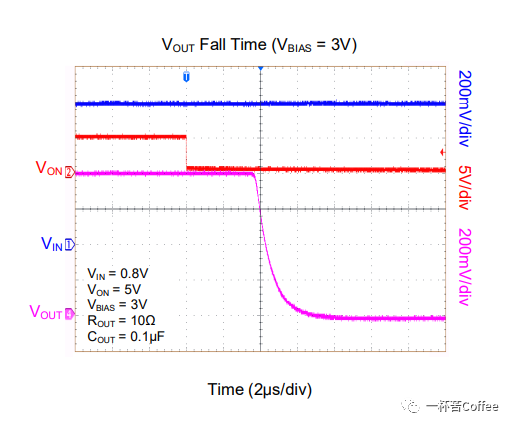

当ON引脚为低电平时,经过非门后变为高电平,下管(NMOS管)导通,实现快读放电过的过程。下电的波形见下如:

优点:不需要额外的电阻元器件,即可实现快速放电的功能。

缺点:这种方式需要在下电时,迅速将ON拉低,否则无法实现快速功能,且这种芯片较少。

4 总结

通过使用泄放电路,可以控制电容器的放电速度,从而避免对其他元件造成损害。泄放电路的实现方式有很多种,其中最常见的是使用电阻。电阻器可以限制电容器的放电速度,从而控制电路中的电流。另外,还可以使用二极管或晶体管等元件来实现泄放电路。这些元件可以在电容器需要释放电荷时,将电荷导向地面或其他地方,从而实现电容器的放电。泄放电路是一种非常重要的电路,它可以控制电容器的放电速度,保护其他元件,确保电路的正常运行。

-

三极管

+关注

关注

142文章

3611浏览量

121856 -

单片机

+关注

关注

6035文章

44554浏览量

634583 -

示波器

+关注

关注

113文章

6240浏览量

184792 -

电路设计

+关注

关注

6673文章

2451浏览量

204125 -

电源芯片

+关注

关注

43文章

1092浏览量

77029

发布评论请先 登录

相关推荐

怎么成为硬件电路设计高手?

硬件电路设计的思路分享

运放电路设计中无源元件的选择,selection of passive components in OPAMP circuit

硬件电路设计之“磁珠”的应用资料下载

硬件电路设计之泄放电路设计

硬件电路设计之泄放电路设计

评论