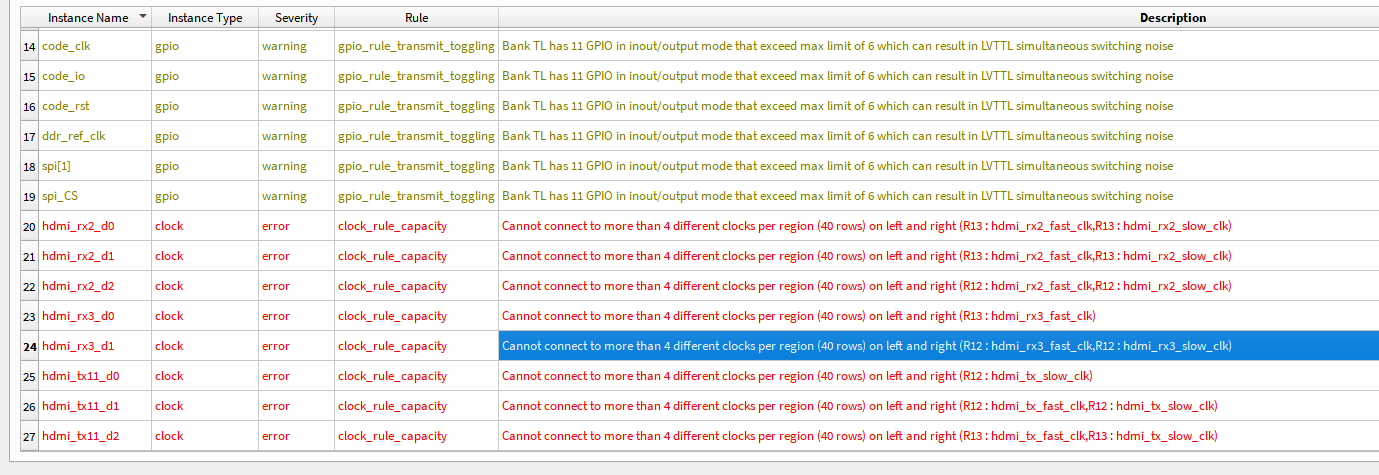

报错:cannot connect to more than 4 different clocks per region on left and right

今天在Ti180分配LVDS的时候出现了这个错误。原因是在pinout文件中对应的Clock Region中,不能超过4个时钟去驱动。

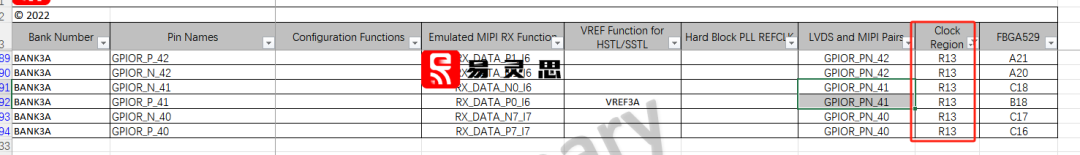

也就是GPIOR_PN_42,41,40三组差分对,不能由两组LVDS来驱动,因为每组LVDS时钟有lvds_fast_clk和lvds_slow_clk两个,两组就会有4个时钟在Region clock R13区域。

| Emulated MIPI RX Function | LVDS and MIPI Pairs | Clock Region |

| RX_DATA_P1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N1_I6 | GPIOR_PN_42 | R13 |

| RX_DATA_N0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_P0_I6 | GPIOR_PN_41 | R13 |

| RX_DATA_N7_I7 | GPIOR_PN_40 | R13 |

| RX_DATA_P7_I7 | GPIOR_PN_40 | R13 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时钟

+关注

关注

10文章

1733浏览量

131469 -

lvds

+关注

关注

2文章

1043浏览量

65803 -

易灵思

+关注

关注

5文章

47浏览量

4862

发布评论请先 登录

相关推荐

易灵思FPGA产品的主要特点

近年来,全球半导体供应链屡受挑战,芯片短缺问题一度对行业产生深远影响。易灵思通过优化供应链管理、强化产能规划,确保客户的FPGA需求得到及时满足。面向工业控制、机器视觉、医疗影像、消费电子、汽车智驾等一众终端领域,

需要在3105上实现这样的功能,将line1的音频信号从3105的left_lop和right-lop输出,为什么没有声音?

我现在需要在3105上实现这样的功能,将line1的音频信号从3105的left_lop和right-lop输出。

方法有三种:

1、通过寄存器R108直接将line1接到left

发表于 11-08 08:26

TLV320AIC3101寄存器配置,PGA_L/R直接到left_lop/right_lop没有声音怎么解决?

我有如下问题:

mic1l/line1接的是从PC电脑输出的音频信号,left_lop,right_lop接着音响的左右声道。

我想从PGA_L/R直接输出到音响(left

发表于 11-08 07:28

请问TLV320AIC3101的LEFT_LOM/LEFT_LOP可否接成RCA单端输出?

手册中描述TLV320AIC3101音频输出包括:HPLCOM/HPLOUT,HPRCOM/HPROUT,RIGHT_LOM/RIGHT_LOP,LEFT_LOM/LEFT_LOP,

发表于 10-25 17:11

TLV320AIC3101左右声道LEFT-ADC与RIGHT-ADC采集相互之间会串音,为什么?

问题:使用TLV320AIC3101芯片,左右声道分开,软件配置完全按照左声道LEFT-ADC只接入MIC1LP/M,右声道RIGHT-ADC只接入MIC1RP/M,MIC2L/R电路上没有任何

发表于 10-11 07:18

I2S Master bits_per_sample != bits_per_chan情况下工作不正常是怎么回事?

32位宽(datasheet要求SCK频率为WS的64倍)。

现象:

使用逻辑分析仪抓包发现每个channel的sck数量始终等于代码中定义的采样深度(bits_per_sample),与通道深度无关

发表于 06-19 06:14

ESP32从机设置bits_per_sample为32的情况下,从机无法向主机发送数据的的原因?

,.bits_per_sample = 32,.channel_format = I2S_CHANNEL_FMT_RIGHT_LEFT,//2-channels.communication_format

发表于 06-17 06:51

使用cypress ezpd_dockupdatefw.exe烧录FW(.BIN)时, 提示“Length of FWCT is more than maximum value” 烧录fail,为什么?

使用 cypress ezpd_dockupdatefw.exe 烧录FW(.BIN)时, 提示“Length of FWCT is more than maximum value” 烧录fail, 这个FWCT 是什么,怎么修改?

发表于 06-03 07:58

易灵思RAM使用--Update5

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目录

国产FPGA应用专题--易灵思Efinity软件使用心得

做为FPGA的集成开发环境,不同的厂家其实大同小异。很多国产厂家,如安路,高云,会在软件上贴近Xilinx和Intel,以节省客户的软件使用成本。而国产厂商的易灵思的集成开发环境Efinity似乎

易灵思RAM使用--Update4

易灵思RAM在使用时可以会遇到一些问题,这里把常用的问题总结下。 1、ram初始化文件路径是工程路径 在对ram进行初始化时需要指定文件路径,这里要注意'/'的方向。 (1)如果文件放在工程目录

易灵思Jtag_bridge_loader生成-v2

Efinity版本:2023.1及以前版本。 易灵思器通过jtag bridge烧写flash时需要自己生成一个jtage birdge文件。jtage bridge 工程的目的是为了打通JTAG

易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

易灵思Ti180报错分析cannot connect to more than 4 different clocks per region on left and right

评论