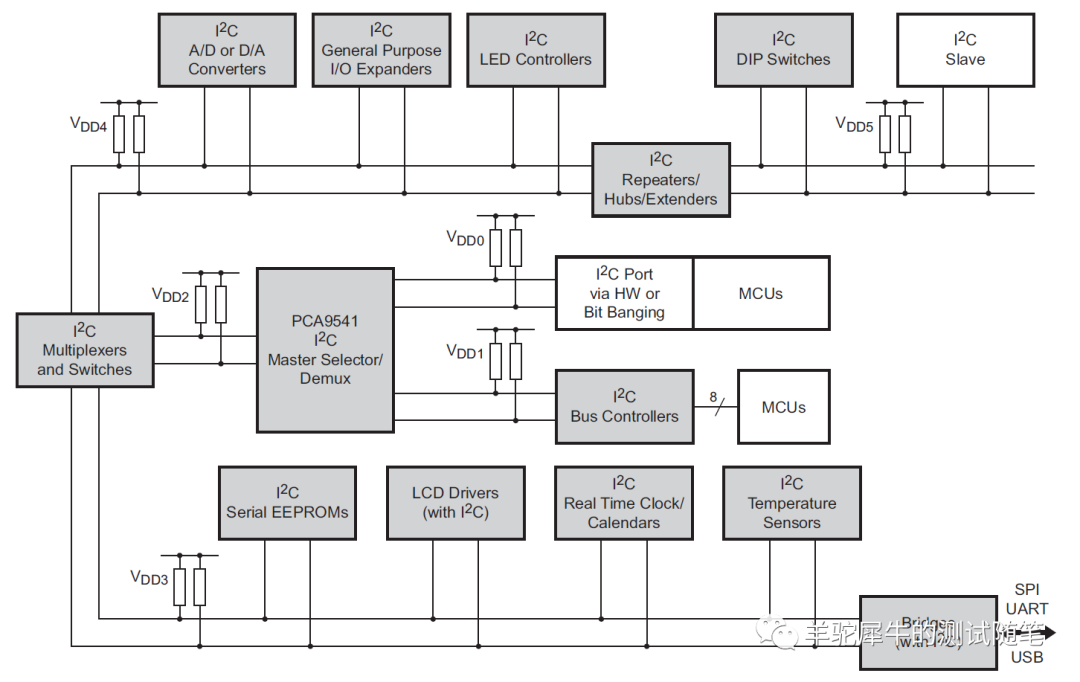

前面一章讲解了I2C总线的基本原理,那么在电路设计完成打板回来,肯定要做信号测试来验证设计;

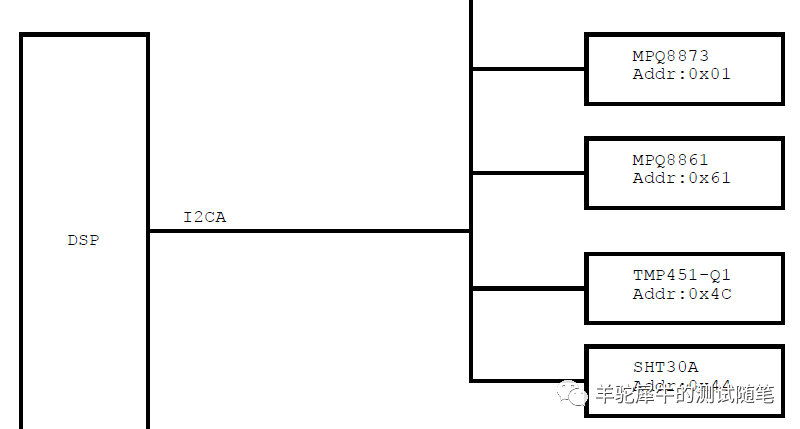

1、梳理测试内容,根据电路图上梳理出I2C总线,包括每一路I2C一共有几个主机,几个从机,以及从机的地址信息;

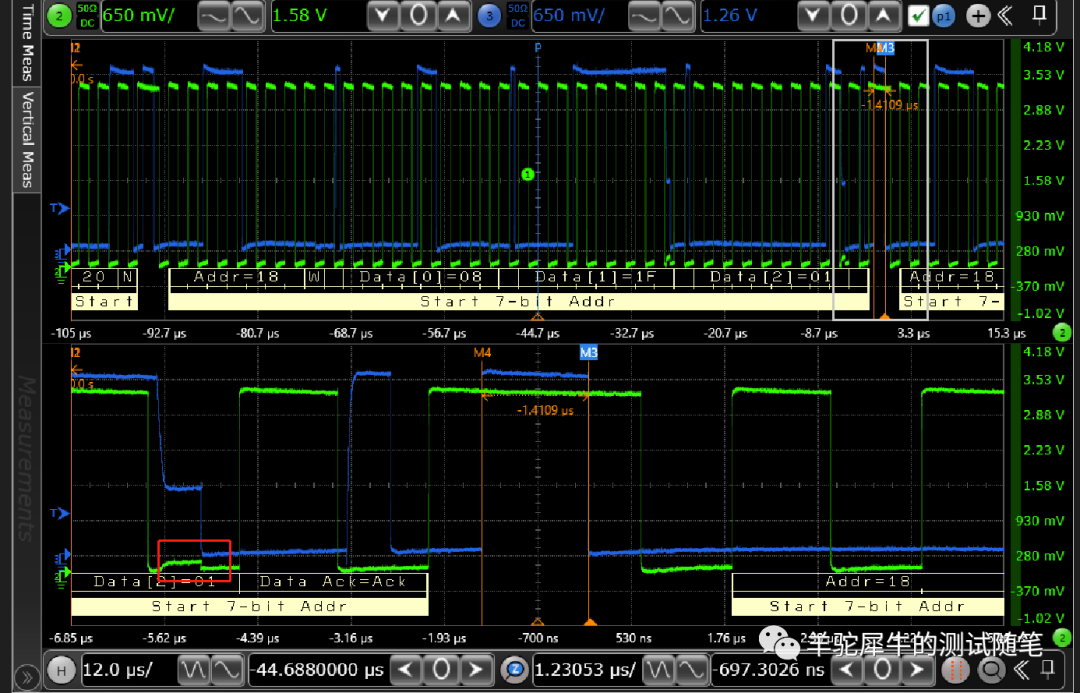

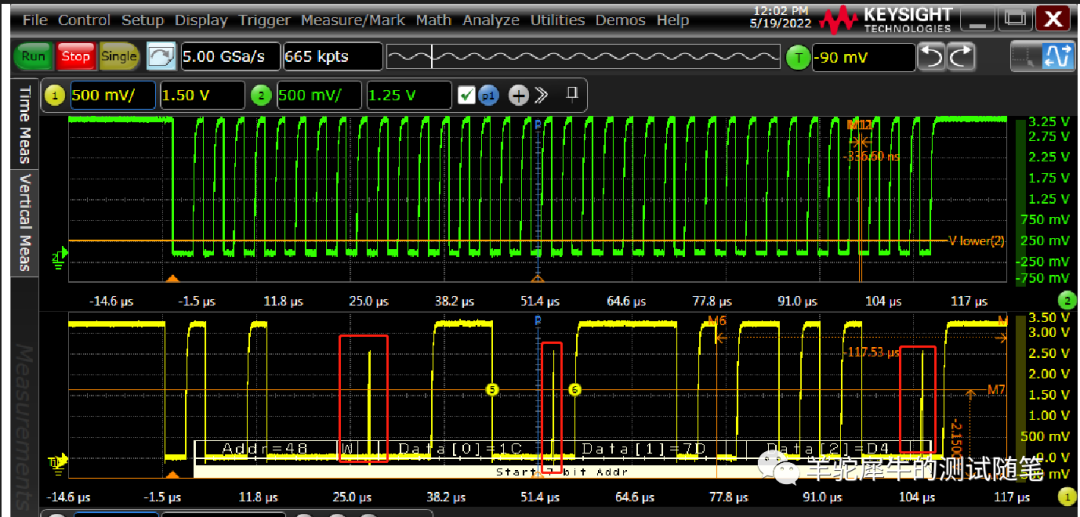

2、使用示波器的I2C协议分析功能或者其他I2C解析工具,将总线上的实时数据抓取解析,看一下是否包括电路设计上的所有器件地址,或者是有多余的地址信息;

因为小编在测试中遇到太多实测地址比设计少的,这个好理解,一个是冗余设计,当前没有使用,一个原因是软件上漏掉了;此外,实测到设计上没有的地址信息,这个大概率发生在后期改版过程中,硬件设计更换了总线上的器件,地址也给到软件做更改,但是软件代码上没有将之前的不再使用的地址信息删掉,导致总线还是存在访问此地址信息的请求数据;

无论是多了还是少了地址,对于测试来讲都是有问题的,必须搞清楚,是问题的话,就分析解决,不是的话,就做个澄清说明;

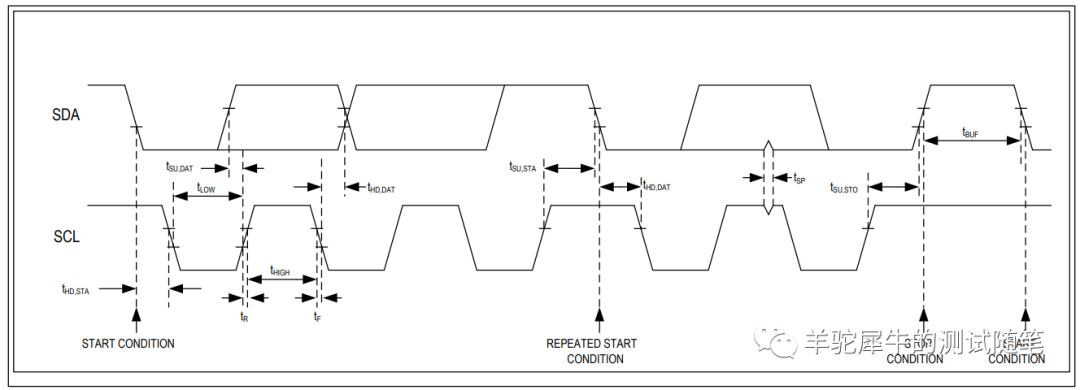

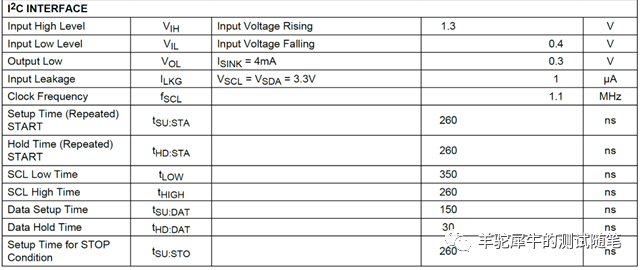

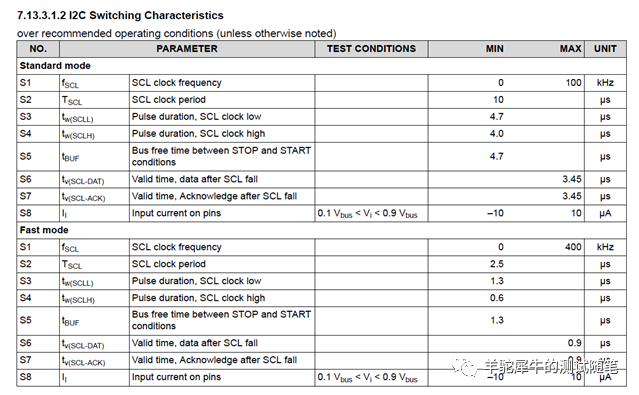

3、整理各个器件对于I2C总线的电平与时序要求;详细如下:

频率:指的是SCL的时钟频率,测量这个参数的意义在于判定总线是单一的速率还是多种速率模式混合,其次确定了时钟频率,有助于后面时序参数的确认,因为不同速率数据时序的要求是不一样的。

正/负脉宽:SCL的高低电平宽度,因为I2C是高电平进行数据采样,低电平时SDA电平变化,所以,无论高电平还是低电压都一定有个最小值来满足采样和电平变化;

逻辑高/低电平:SCL和SDA均要测量,只有测量值满足高低电平的要求,才真正意义上能被识别为逻辑1或0;此处要注意的是,即使总线电平是同一个VCC,不同器件对于逻辑电平门限也是不太一样;

上升/下降时间:指的是SCL和SDA的边沿在高低电平门限之间的持续时间,一般取30%~70%,这也只是一个相对的经验值,因为大多数的I2C器件逻辑高低电平门限是30%Vcc和70%Vcc;追求准确度来说,要根据实际器件的高低电平门限值来卡这个时间;前文讲到总线电容和上拉电阻的值会影响上升时间的值,若测试有问题,可以通过调节上拉电阻的值来改善。

Vmax/Vmin:总线数据的最大电平和最小电平值;主要看是否有上下过冲,若过冲超过芯片要求,很可能会损坏芯片。

Tbuf:帧间隔时间,即SDA线的上一帧传输结束到下一帧开始之间的间隔时间。

开始标志位的保持时间(tHD:STA):在SCL为高电平时SDA由高变低的边沿到SCL第一个下降沿的时间。

结束标志位的建立时间(tSU:STO):在SCL为高电平时SDA由低变高的边沿到SCL前一个上升沿的时间。

重复起始标志位的建立时间(tSU:STA):在第9个时钟之后。在SCL为高的上升沿到SDA的下降沿之间的时间间隔。

数据建立时间(tSU:DAT):一个比特周期内,SDA变化沿到SCL上升沿的时间间隔。

数据保持时间(tHD:DAT):一个比特周期内,SDA变化沿到SCL下降沿的时间间隔。

4、搭建测试环境,实操测试

- 测试所需设备:示波器(最好有协议分析软件)、示波器探头(有源探头优选)、待测DUT(加载I2C总线通讯的软件)

- 选择信号测试点:测量写信号,在从器件端靠近芯片pin脚;测量读信号,在主器件端靠近芯片pin脚;

- 注意事项:探头的接地线尽可能短,避免引额外电感量影响测试准确性。

下面以实际的例子来演示:

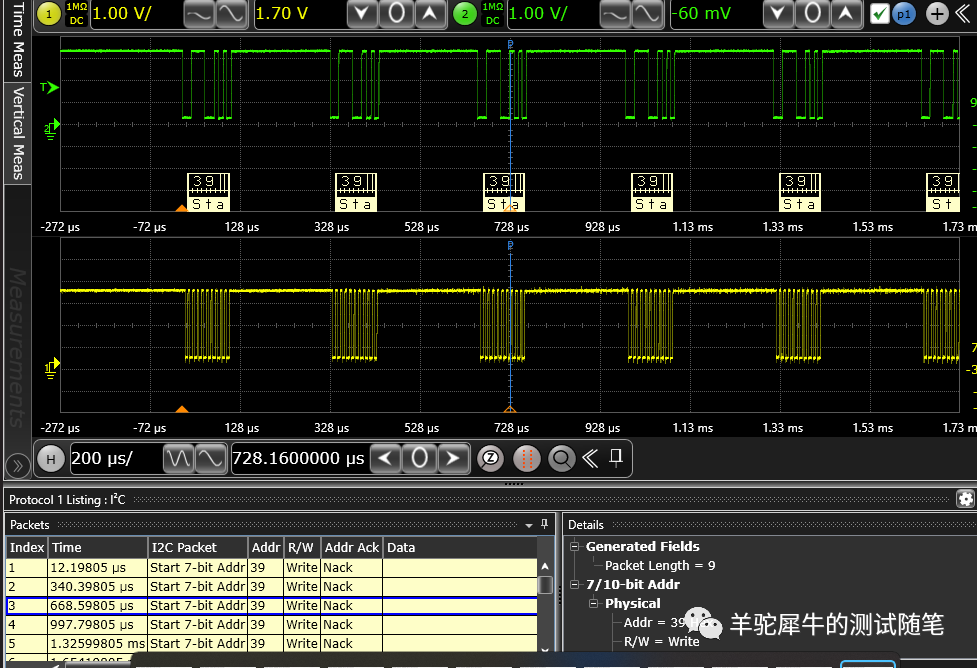

- 待测I2C总线只有一主一从,从机地址为 0x39,用示波器抓取总线数据并解析,确认是只有0x39地址的数据;

- 主从器件的I2C时序要求

常见问题:

1、上升下降时间不满足

更改上拉电阻的阻值

2、建立保持时间不满足

①是否速率太低,调高至fast mode或者更高速率看一下

②数据SDA变化沿调整,前移或者后移

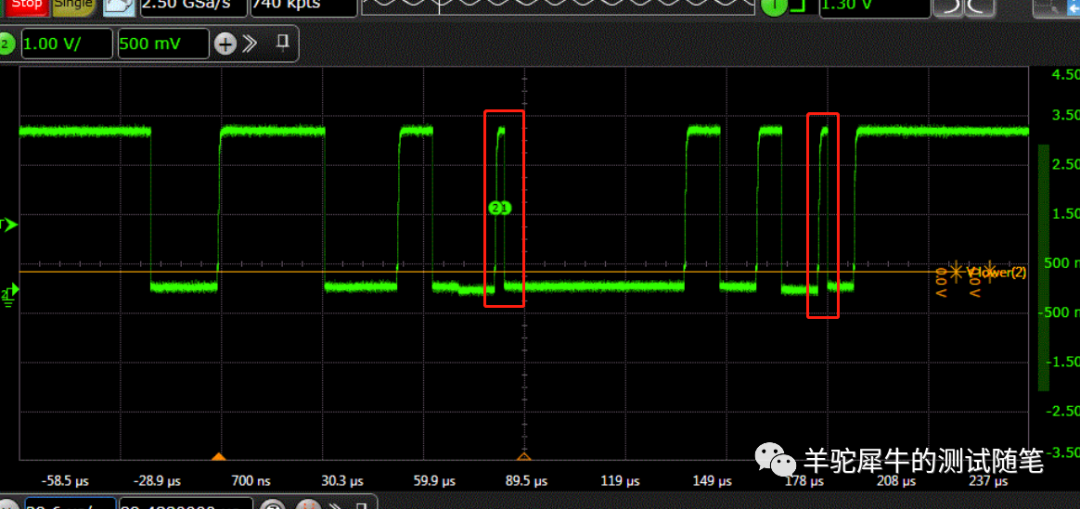

3、SDA边沿有台阶

①一般发生在主从对总线控制的切换时

②若芯片内部有上拉,外部还上拉至Vcc,那么在主机释放总线后会被内部上拉电阻分压至台阶电平,然后再被从机拉低

4、我最开始学习I2C总线,对于总线协议了解的不清楚,造成了一个误解如图所示红的框出来的波形,起初以为像第一张图里脉宽很小,电压也不高的是毛刺信号,第二张的是数据信号;其实都不对,两张图片里的是同一个东西,即应答信号前释放总线造成的;为什么电平与脉宽大小不一,是跟上拉电阻和从器件响应时间决定的。上升时间长的话,主机释放总线,电平从低开始缓慢升高,在还未升至Vcc之前,从机开始应答,拉低总线,那么就很像毛刺;若上升时间很快,从机还没响应之前就会有一段时间的高电平;

-

上拉电阻

+关注

关注

5文章

366浏览量

31719 -

示波器

+关注

关注

113文章

7125浏览量

196831 -

I2C总线

+关注

关注

8文章

422浏览量

63501 -

SDA

+关注

关注

0文章

125浏览量

29745 -

SCL

+关注

关注

1文章

244浏览量

18071

发布评论请先 登录

I2C总线原理详解

I2C总线接口模块设计

基于CPLD的I2C总线接口设计

I2C总线信号与测试案例(二)

I2C总线信号与测试案例(二)

评论