Hello,大家好,这一系列准备了一些硬件工程师经典面试题,如果有兴趣的粉丝比较多就继续更新,不然的话,…

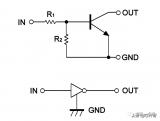

面试题的选择当然是偶个人觉得比较好的,所以肯定有一定的主观性。咱以前为公司招聘时也出过题目,都是最简单的(例如,给一个“场效应管驱动电磁继电器”电路,让你描述一些元件的作用),至于工程师能力与经验方面的,咱们边看简历边聊,因为个人觉得, 除非是针对性面试,通用的硬件工程师面试题应该以考查基本功为主 (仅供参考)。

举个例子,“ 给出一个555芯片的电路图,让你判断其具体功能 ”就不算是个很好的面试题,基本上可以理解为考查记忆能力了(如果你理解成经验,当我没说)。

再举个例子,“ 使用CMOS搭建Y=AB+CD逻辑电路 ”是个比较好的面试题,好就好在:也许你已经记不清(或混淆了)“与”、“或”门的具体结构,但是只要知道CMOS门的基本结构(上PMOS下NMOS),稍微琢磨一下就能做出来。

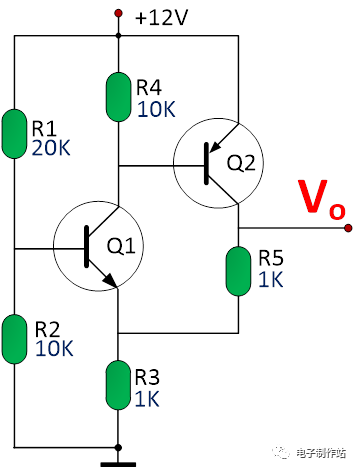

言归正传,今天来求解下图所示三极管电路的输出电位值( Vo ),其中包含两个三极管(bipolar junction transistor, BJT),NPN与PNP管各一个,并且假设发射结压降均为0.6V,电流放大系数非常高,基极电流可忽略。

为了求出输出电位值,你需要分别求出R3与R5两端的压降,两者相加即为输出电位值,所以, 你需要分别获得流过R3与R5的电流 。

首先 求得流过R3的电流 ,你只需要获得R3上端的电位即可。由于Q1的基极电流为0(已知条件),所以Q1的基极电位可由R1与R2对电源+12V的分压获得,即+12V×10K/(10K+20K)=+4V。而Q1的发射结压降为0.6V(已知条件),所以R3上端(Q1发射极)的电位为+4V-0.6V=+3.4V。那么,很明显,流过R3的电流为3.4mA,如下图所示:

接下来 求得流过R5的电流 ,但是3.4mA是由流过R5与Q1发射极的电流叠加而成,如何确定分配比例呢?由于Q1基极电流为0,所以其发射极电流等于集电极电流,该值同样与流过R4的电流相等,因为Q2的基极电流同样为0(已知条件)。

那么,流过R4的电流是多大呢?由于R4与Q2的发射结并联,所以R4两端的压降为0.6V(已知条件),继而可求得流过R4的电流为60μA,这也是Q1发射极的电流值,如下图所示。

至此,流过Q1发射极与R3的电流都已求出,根据节点电流法,流过R5的电流是3.4mA-60μA=3.34mA,那么R5两端的压降也就自然可以求出了,即3.34mA×1K= 3.34V,将该值与R3两端的压降(3.4V)相加,即可求得输出电压为3.34+3.4V=6.74V,如下图所示。

这个电路分析考查了2个基本点。

其一 ,基极分压式共射放大电路的静态工作点求解方法;

其二 ,流过R4电流的计算方法。

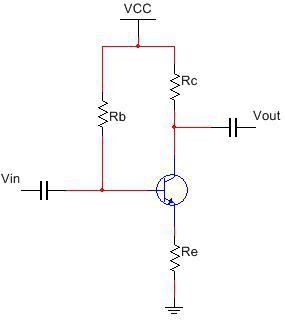

值得一提的是,“将三极管发射结与电阻并联”的方式也有不少巧妙的应用,在《三极管应用分析精粹:从单管放大到模拟集成电路设计》一书中就有使用该电路结构提升有源负载的恒流能力,以达到“提升整个电路的电压放大系数”的目的,如下图所示。

-

三极管

+关注

关注

142文章

3611浏览量

121880 -

继电器

+关注

关注

132文章

5333浏览量

148838 -

NPN

+关注

关注

11文章

2643浏览量

47331 -

基极电流

+关注

关注

1文章

31浏览量

3220

发布评论请先 登录

相关推荐

三极管的应用电路 NPN和PNP型三极管的区别

三极管的三种工作状态 三极管在电路中的作用

PNP三极管和NPN三极管的开关电路

数字三极管与普通三极管电路对比

求解三极管电路的输出电位值

求解三极管电路的输出电位值

评论