电子发烧友网报道(文/周凯扬)对于任何先进晶圆厂来说,逐渐放缓的制造工艺进步已经开始对其业务造成部分影响。即便是头部客户,也会追求相对成熟的工艺来减少设计和制造成本。为了不让芯片性能停滞不前,绝大多数厂商会选择异构集成的方式,借助先进封装技术实现“超越摩尔”。诸如台积电、英特尔等厂商,也都纷纷推出了3DFabric、Foveros之类的技术,而三星也不甘落后,一并追求突破半导体技术的极限。

为了进一步发挥其先进封装技术优势,三星于去年年底在其半导体业务部门内成立了先进封装(AVP)业务团队。作为一家同时具备内存、逻辑代工和封装业务的厂商,三星在异构集成上已经有了多年的经验,尤其是逻辑与内存的异构集成。

I-Cube

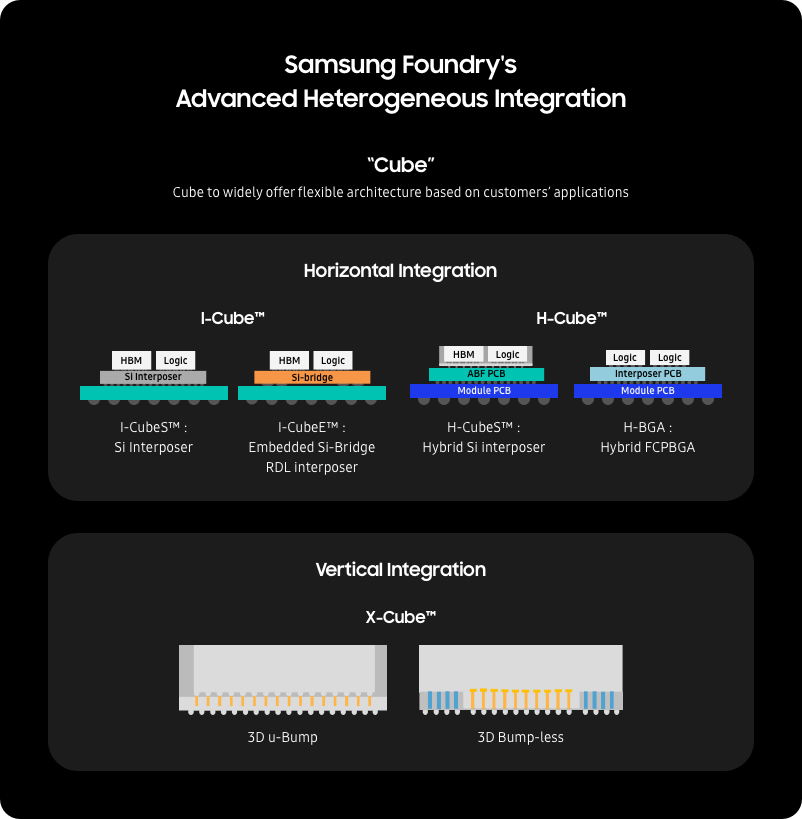

以绝大多数服务器芯片面临的带宽问题为例,三星针对不同的带宽需求,提供了完备的解决方案。比如针对需要1TB/s的超大带宽场景,三星提供了逻辑电路垂直堆叠的架构。而针对需要超大内存带宽的场景,比如196GB/s到1TB/s的带宽范围内,三星则提供了逻辑电路与HBM堆叠至硅中介层上的方案,I-CubeS。

且根据HBM die的配置分布,三星已经推出了I-Cube2、I-Cube4、I-Cube8三大方案,更为复杂的I-Cube12也已经在研发过程中,预计明年第四季度成功验证,2025年实现量产。这也是越来越多服务器、AI芯片所选的方案,I-Cube与HBM3的搭配提供了相对GDDR6更高的容量和带宽。

三星Cube异构集成技术 / 三星

除此之外,三星也在研究HBM与逻辑电路直接垂直堆叠的方案,这类HBM无需缓存die,而是将缓存die集成到逻辑die中,进一步提高能效降低延迟。有趣的是,最近韩媒也爆出消息,SK海力士将与英伟达联合研究GPU直接堆叠HBM4的设计,不过其最终封装可能会由台积电来接手。

针对60-196GB/s内存带宽区间的应用,比如头戴AR/VR等设备,三星的计划是进一步提高其能效和降低延迟。为此,三星正在进行LLW DRAM这一低延迟宽IO产品的研发,用于替代传统的LPDDR内存。其异构集成结构是将逻辑电路和LLW内存垂直堆叠在重布线层(RDL)上,根据三星给出的数据,相比传统的FBGA封装LPDDR内存,其I/O数、带宽都将成倍增长,而相比硅中介层的方案又可以节省20%的封装成本。

X-Cube

至于全3D的逻辑异构集成方案X-Cube,则是通过微凸块或更先进的铜键合技术,将两块垂直堆叠的逻辑裸片连接起来。其实早在HBM的垂直堆叠上,三星就已经用上了微凸块连接技术,且自2016年就实现了大规模量产。

然而面对更为复杂的逻辑die垂直堆叠,则需要对其设计进一步改进,从而避免电源完整性、信号完整性以及热设计上带来的新问题。所以三星也在研究相关的集成硅电容、散热增强设计等,来解决这些异构集成实现过程中的顽疾。

三星代工业务的发展负责人Moonsoo Kang表示,他们预计将在明年开始量产微凸块类型的X-Cube产品,而2026年才会开始量产铜键合的X-Cube产品。可以看出,在台积电和英特尔厂商都已经规划好下一代先进封装路线图的前提下,三星也在加快步伐推进新技术的落地,这样才能给其半导体业务带来更多的竞争优势。

写在最后

与依然在缓步推进的逻辑工艺不同,异构集成这类先进封装技术最终是起到降低设计成本,提高芯片设计效率并优化PPA的目的,更像是对摩尔定律的一个横向扩展。而作为晶圆厂,在钻研这类技术的同时,也必须与EDA、Chiplet、PCB等领域的厂商达成深入合作,才有可能把这类业务推向更多的芯片设计公司。

-

晶圆厂

+关注

关注

7文章

621浏览量

37869

发布评论请先 登录

相关推荐

人工智能应用中的异构集成技术

薄板拼焊激光焊接工艺

晶合集成28纳米逻辑工艺通过验证

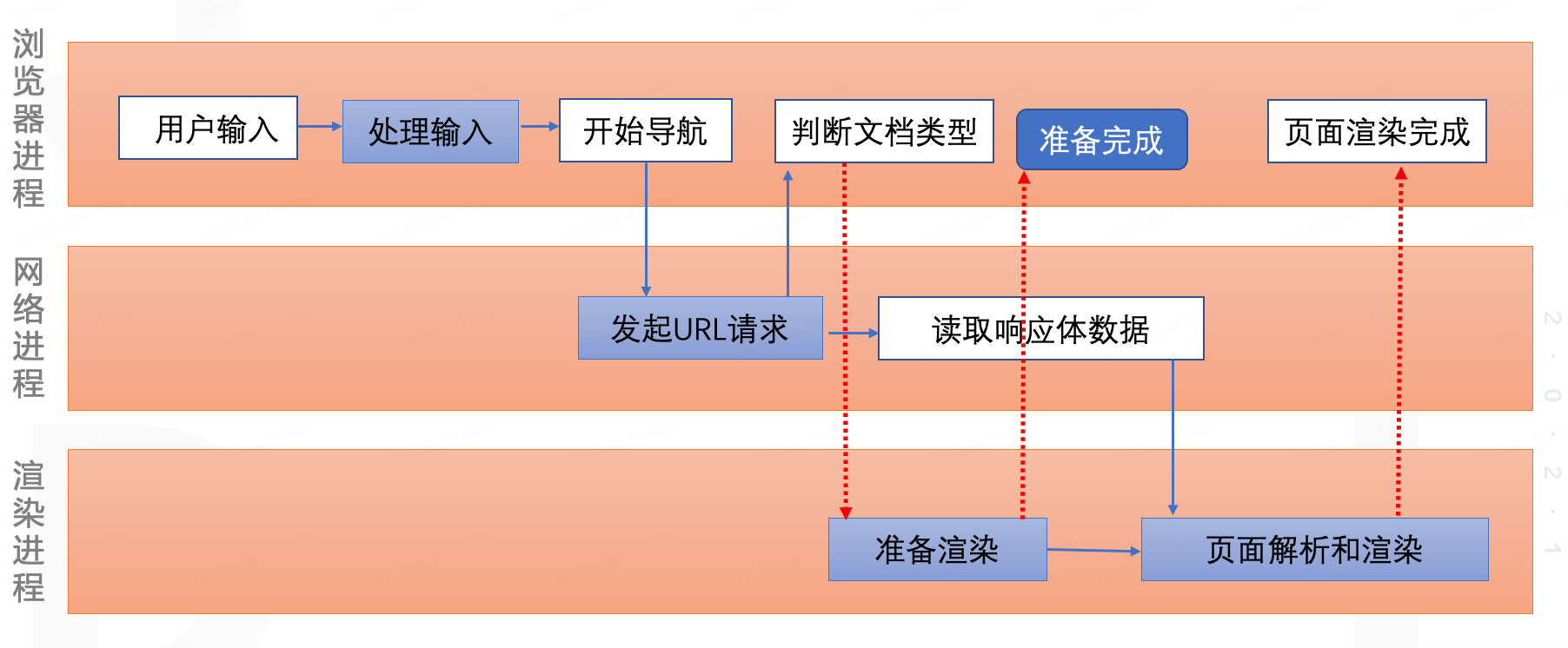

不只是前端,后端、产品和测试也需要了解的浏览器知识(二)

晶圆厂拼的不只是先进逻辑工艺节点,异构集成技术不可小觑

晶圆厂拼的不只是先进逻辑工艺节点,异构集成技术不可小觑

评论