单光子雪崩二极管(SPAD)的关键特征是能够探测单个光子并提供数字信号输出。雪崩倍增过程产生了可探测的电信号,该电信号可以在无需额外电路的情况下被放大到高电压,从而使SPAD能够探测单个光子。具体而言,采用CMOS技术制备的SPAD可以探测近红外(NIR)信号,这是如激光雷达(LiDAR)、飞行时间(ToF)成像和NIR光学断层扫描等诸多应用的关键要求。这些应用需要特定的性能特征,例如高光子探测概率(PDP)。

据麦姆斯咨询报道,近日,韩国科学技术研究院(KIST)的科研团队在IEEE Journal of Selected Topics in Quantum Electronics期刊上发表了以“Back-Illuminated Double-Avalanche-Region Single-Photon Avalanche Diode”为主题的论文。该论文的第一作者为Eunsung Park,通讯作者为Myung-Jae Lee和Woo-Young Choi。

为了提高探测器的PDP性能,这项工作提出了一种双雪崩区(DAR)SPAD,该SPAD通过掺杂优化扩展了雪崩倍增区。双雪崩区SPAD采用40 nm CMOS图像传感器(CIS)技术制备,这是迄今为止所报道的最先进的CMOS SPAD技术。随后,研究人员对双雪崩区SPAD的全部性能进行了清晰的表征和分析,并对传统的SPAD与双雪崩区SPAD的电学和光学特性进行了比较,证明了优化的有效性。

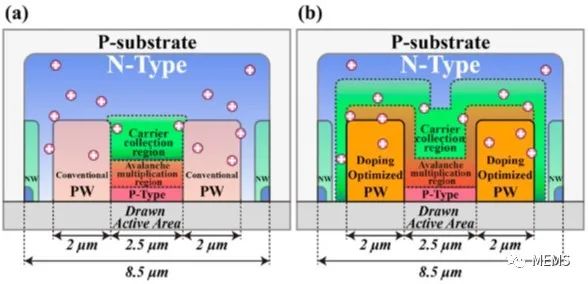

为了在背照式(BSI)工艺中提高SPAD的PDP,可以引入微透镜(microlens)和背面沟槽引导(backside trench guide)等技术。然而,实现额外结构需要专门的设备和工艺,这样不仅更难控制,而且制造成本也更高。如图1所示,最具成本效益且最简单的方法是在不增添任何额外结构下优化掺杂浓度,以扩展直接影响PDP的雪崩倍增区和载流子收集区。

图1 (a)未经保护环(GR)掺杂优化的传统SPAD(b)经过GR掺杂优化的双雪崩区SPAD

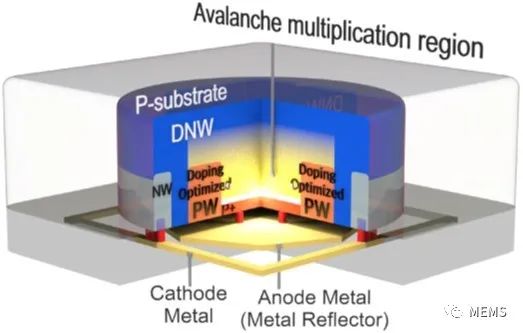

如图2所示,为了验证并演示上述技术,研究人员采用基于圆形40 nm背照式CMOS图像传感器技术制备了双雪崩区SPAD。SPAD由重掺杂的P型区“P+”与倒掺杂的n型区“深n阱(DNW)”组成,它们连接在一起形成p-n结。为了防止边缘击穿并提高PDP,将掺杂优化的p阱(PW)GR置于SPAD的p-n结周围。传统SPAD与双雪崩区SPAD之间的唯一区别就是其PW GR的掺杂分布。

图2 双雪崩区SPAD的横截面图

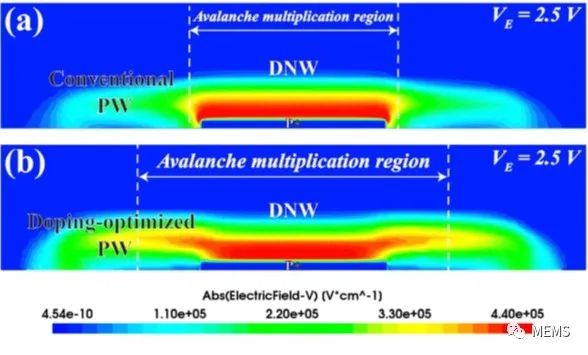

接着,研究人员利用TCAD仿真软件核查了SPAD在2.5 V偏置电压(VE)下的电场分布,结果如图3所示,显示了两种SPAD的雪崩倍增区的电场分布。

图3 VE = 2.5 V时两种SPAD的电场分布图:(a)采用传统PW GR的SPAD;(b)采用掺杂优化PW GR的SPAD

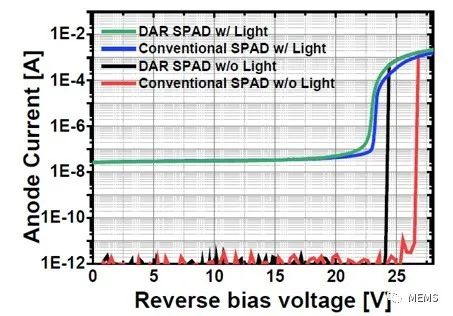

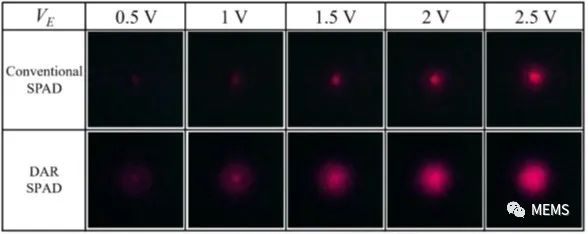

随后,研究人员通过电学和光学实验对两种SPAD的特性进行了清晰的评估,从而证明了GR优化的有效性,两种SPAD的I-V特性和有效活性面积相关测试结果如图4和图5所示。研究人员还对两种SPAD的有效活性区域、PDP、暗计数率(DCR)、时间抖动(Timing jitter)等指标做了详细的对比和分析。

图4 两种SPAD的I-V特性结果

图5 两种SPAD在不同偏置电压下的光发射测试(LET)结果

综上所述,这项研究提出了一种基于40 nm背照式CMOS图像传感器技术制备SPAD的优化方案。SPAD采用重掺杂P型(P+)和倒掺杂DNW结设计和制备。用于扩展雪崩倍增区的掺杂优化GR在最大限度地提高PDP的同时,保留了其原有功能,即在结的边缘防止过早边缘击穿(PEB)。通过将电学和光学实验结果与传统SPAD进行比较,研究人员证明了GR优化的有效性。所提出的双雪崩区SPAD在700 nm处达到了约89%的峰值PDP,在940 nm处达到了约45%的峰值PDP,这是迄今为止报道的SPAD中在2.5 V偏置电压下的最高值。在相同的工作条件下,其DCR为27 cps/μm²,时间抖动的半峰全宽(FWHM)为89 ps。

审核编辑:刘清

-

探测器

+关注

关注

14文章

2669浏览量

73484 -

图像传感器

+关注

关注

68文章

1936浏览量

129868 -

雪崩二极管

+关注

关注

2文章

54浏览量

12906 -

激光雷达

+关注

关注

969文章

4057浏览量

190842 -

CMOS技术

+关注

关注

0文章

68浏览量

10337

原文标题:背照式双雪崩区单光子雪崩二极管(SPAD)

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

背照式双雪崩区单光子雪崩二极管(SPAD)介绍

背照式双雪崩区单光子雪崩二极管(SPAD)介绍

评论