上海华宏利半导体制造有限公司就“半导体结构及其形成方法”申请专利,申请公告日为11月17日,申请公告号为cn113921595b。

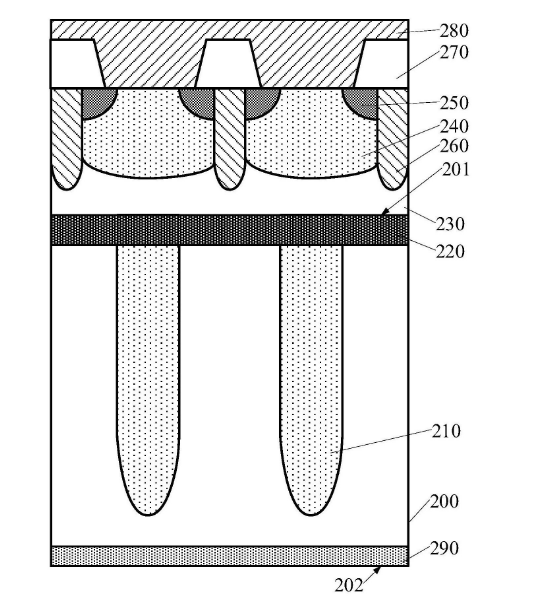

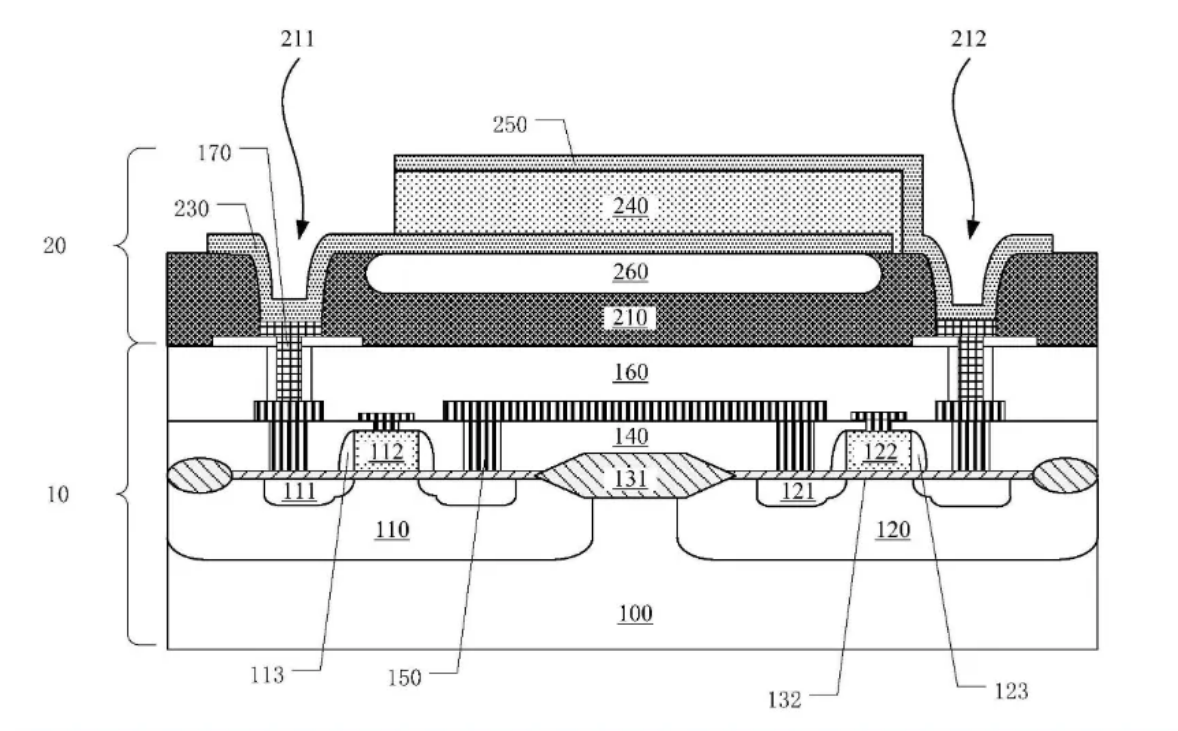

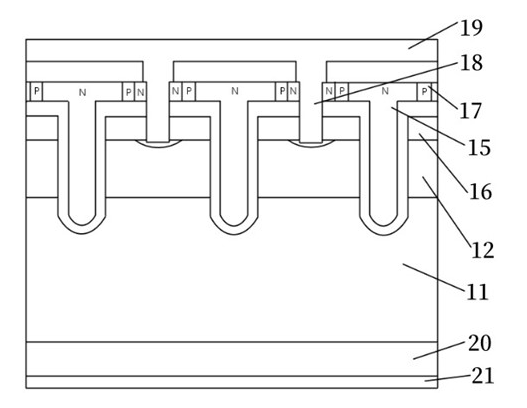

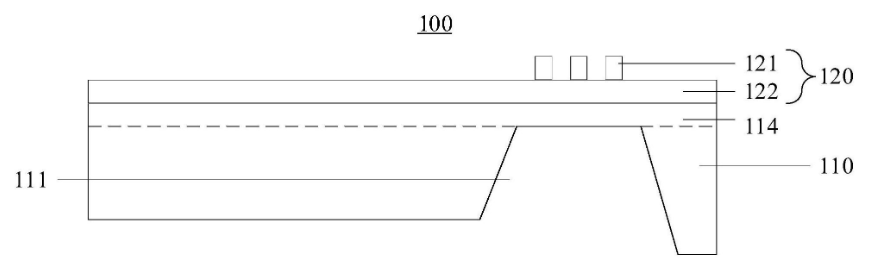

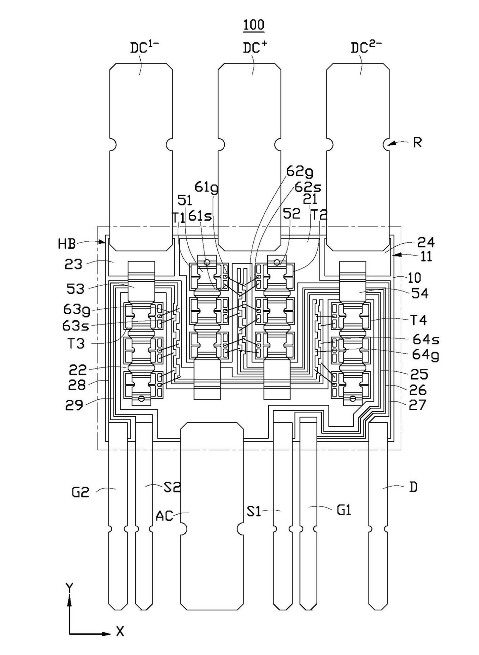

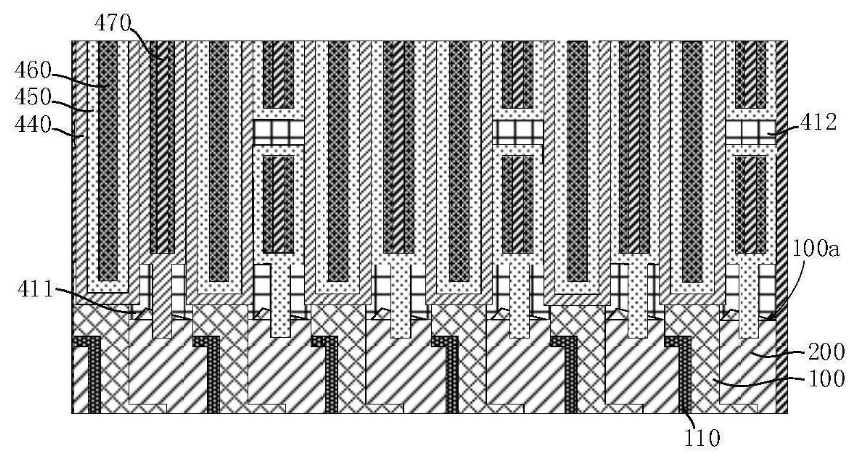

专利摘要据半导体结构及其形成的方法中,半导体结构包括如下:第一夹杂着离子的电路板;位于基板内的深谷结构、机关和深深的凹槽结构位于上方的杂质区域切断,位于阻挡掺杂区上的第一外延层,第一外延层内的体区,至少一部分是所述深谷位于结构的上部。位于本体内的发源区,本体区露出发源区的部分表面。栅极位于第一外延层,与深谷结构相邻的基板上,栅极接触本体区和发源区暴露的表面。位于衬底底部的集电区,第2面露在集电区表面,集电区与深槽结构底部之间有集电区的间隔。通过这种半导体结构,绝缘栅晶体管的性能得到了提高。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

半导体

+关注

关注

334文章

27290浏览量

218086 -

电路板

+关注

关注

140文章

4951浏览量

97689 -

基板

+关注

关注

2文章

274浏览量

23003

发布评论请先 登录

相关推荐

意法半导体与华虹半导体合作生产40nm MCU

近日,有消息传出,全球知名半导体公司意法半导体(ST)已与中国晶圆代工厂华虹半导体达成一项新合作,计划在中国共同生产40nm节点的微控制器单元(MCU)。这一消息引起了业界的广泛关注。

半导体PN结的形成原理和主要特性

半导体PN结的形成原理及其主要特性是半导体物理学中的重要内容,对于理解半导体器件的工作原理和应用具有重要意义。以下是对

p型半导体是怎么形成的

p型半导体(也称为空穴半导体)的形成是一个涉及半导体材料掺杂和物理性质变化的过程。以下是对p型半导体形成过程的详细解析,包括其定义、掺杂原理

AMEYA360:士兰微“MEMS器件及其制造方法”专利获授权

天眼查显示,杭州士兰微电子股份有限公司近日取得一项名为“MEMS器件及其制造方法”的专利,授权公告号为CN109665488B,授权公告日为

上海华虹宏力半导体制造有限公司取得专利

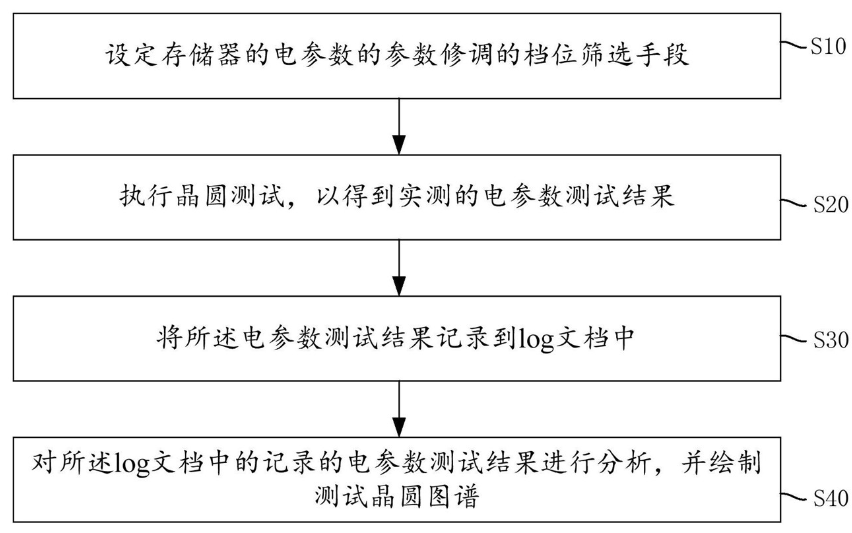

这项专利技术主要包括四个步骤:首先,确定存储器电参数的调整范围;其次,进行晶圆测试获取实际测量的电参数;接着,将这些数据记录在日志文件中;最后,对日志文件中的数据进行分析,生成测试晶圆图谱。

中芯国际获“半导体结构及其形成方法”专利

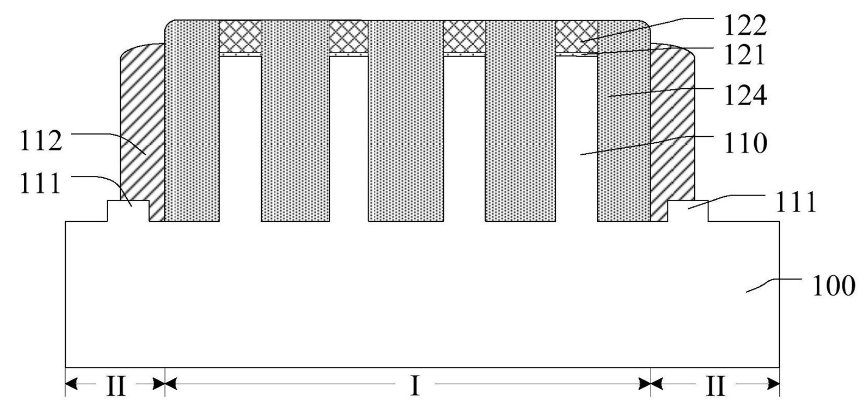

该半导体结构及其形成方法主要包含以下步骤:首先,需制备基底,其中含有器件区及位于两侧的隔离区;之后进行基底图案化,制作出衬底及突出于衬底的鳍部;接着,在器件区两侧

华虹宏力半导体获半导体器件专利

该发明涉及一种半导体器件,包含底座,又划分为第一和第二园区,一个位于另两个邻侧之间;两个子漏区,坐落于底座的第一园区;虚拟结构,位于两子漏区间的底座上;源区,位于底座的第二园区;栅极结构,位于第一和第二园区之间的底座上。

深圳芯能半导体获IGBT芯片专利,创新接触孔连接ESD结构提升安全性

此次专利的申请日期为2023年8月22日,授权公示日为2024年3月26日,授权公告号为CN116779666B。此项专利主要涉及的新型IGBT芯片

科大讯飞高空抛物检测专利获授权

近日,科大讯飞成功获得了一项名为“高空抛物检测方法、装置、计算机设备和存储介质”的专利授权。该专利主要针对高空抛物行为的自动检测,通过创新的算法和技术手段,显著提高了检测效率和实时性,

武汉新芯集成电路专利“半导体器件及其制备方法”公布

在此项专利中,申请人展示了一种新型半导体器件及其制作流程。其主要步骤包括先制备出含有第一钝化层,第一金属层和第二钝化层的半导体基体;接着在第二钝化层背对第一钝化层的一侧表面设计并

明阳电路取得Micro LED相关专利

明阳电路在12月份取得了多个Micro LED发明专利的新进展。其中,“一种micro-led芯片及其集成方法”的发明专利已经获得授权,

华虹宏力“半导体结构及其形成方法”专利获授权

华虹宏力“半导体结构及其形成方法”专利获授权

评论