在这篇文章中,我们将介绍鉴频鉴相器(PFD)的工作原理。

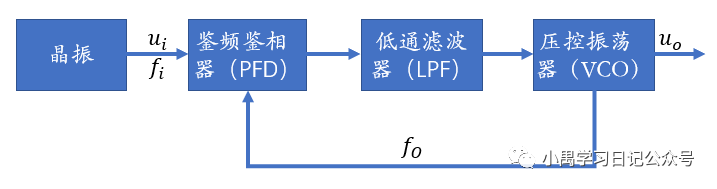

鉴频鉴相器是锁相环中的一个器件,我们要求这个器件能对如下条件做出响应,由此我们就能通过适当的调节实现负反馈,从而使得输出信号的频率不断地接近输入信号的频率。

鉴频鉴相器是锁相环中的一个器件,我们要求这个器件能对如下条件做出响应,由此我们就能通过适当的调节实现负反馈,从而使得输出信号的频率不断地接近输入信号的频率。

- 输出信号与输入信号频率不同时,鉴频鉴相器输出一个电压反映两个信号频率还不相等。

- 输出信号与输入信号相位不同时,鉴频鉴相器输出一个电压反映两个信号相位还不相等。

- 当输入信号与输出信号同频同相时,鉴频鉴相器没有信号输出。

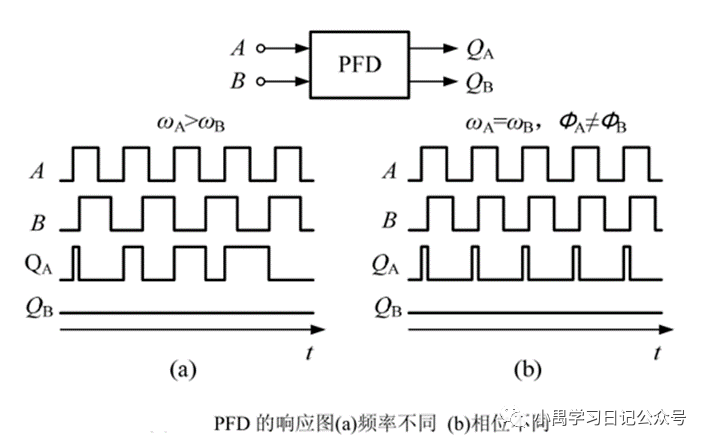

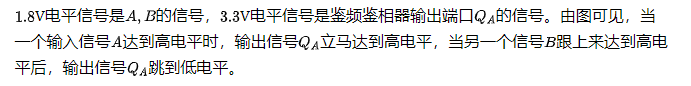

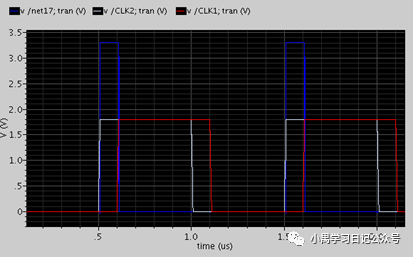

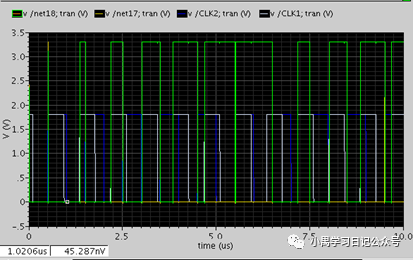

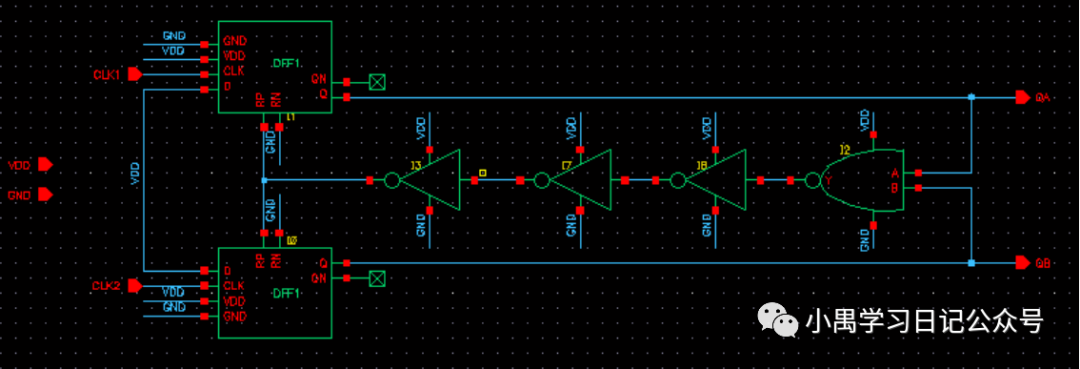

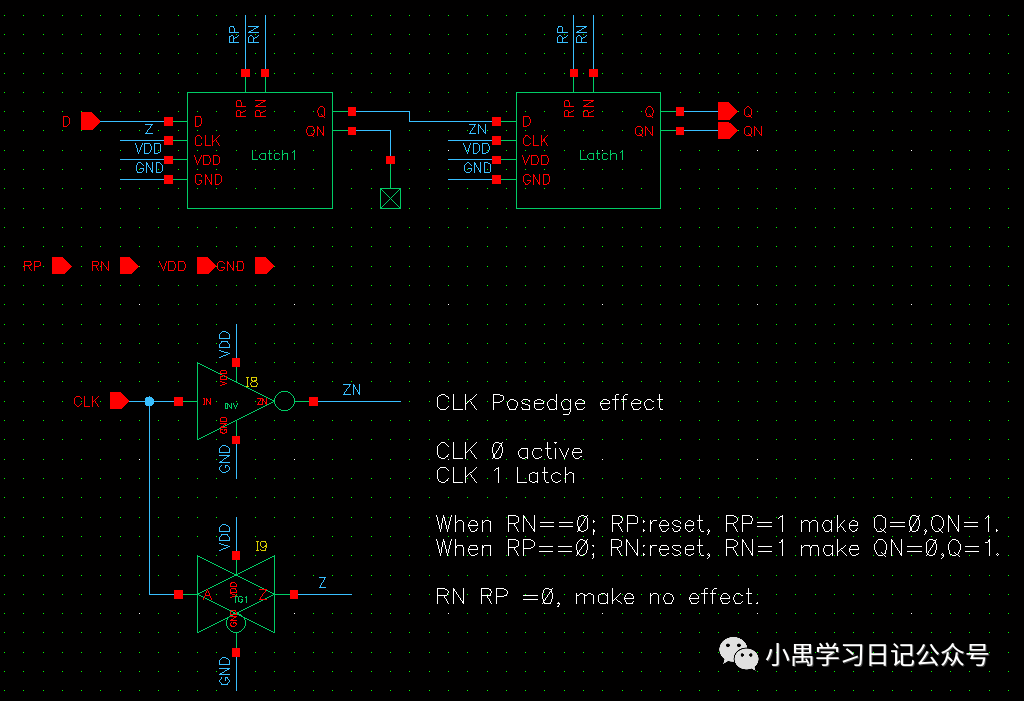

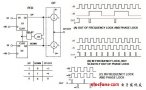

于是,人们设计出了边沿触发型PFD,其工作原理如上图,A,B两个输入端口接的是时钟信号;当A时钟信号的上升沿先到,QA升到高电平,直至B时钟信号上升到高电平,QA电平降至低电平,其间保持低电平;B上升沿先到也是同样的逻辑。在上图(理想情形)中展示出了频率不同(a)和相位不同(b)的QA、QB输出波形。QA、QB即为鉴频鉴相器通过比较A、B信号的相位信息给出的电压信息。我们把 fi,fa分别接在A,B端口,我们就能得到fi,fa之间的频率差和相位差的信息了。如下是我们自己搭建的鉴频鉴相器的仿真结果。

同频不同相

不同频率

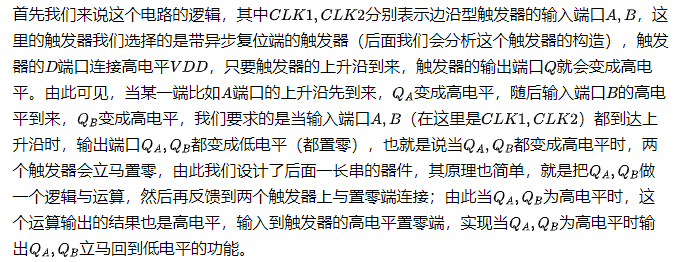

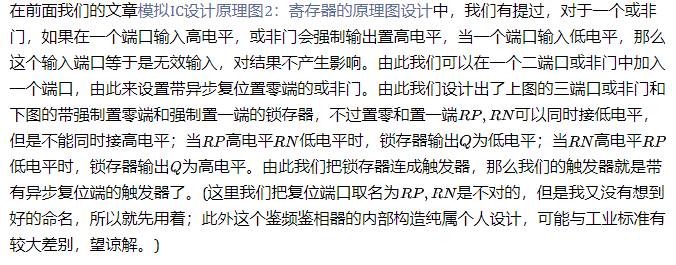

从功能描述上看,每当输入信号上升沿到来时输出就会发送反应,所以我们需要的是设置合适的触发器以及触发器的逻辑。当A端(B端)输入信号上升沿先到来时,QA(QB)输出信号就会上升,然后A当B与同时达到高电平时,输出信号就会同时变为低电平,由此设计出了如下电路结构:

鉴频鉴相器原理图

接下来我们分两步地来分析这个电路结构。

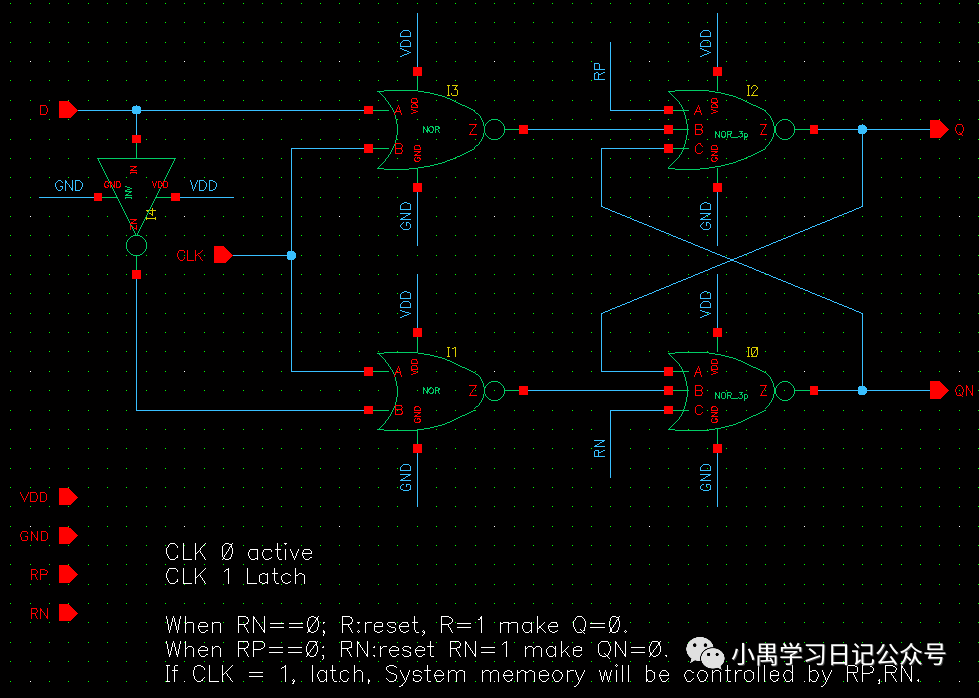

1.带异步复位端的触发器

讨论异步复位触发器之前,我们可以稍微聊一下,同步复位、异步复位的区别:

同步复位的意思是,当复位端满足复位信号时,输出信号并不会立刻变成置零信号,而是要等系统的时钟的触发沿(比如上升沿)到来时,这个触发器才会输出置零信号;在我们理解里,同步的意思是触发器的变化与整个系统同步或者说是与系统的时钟信号同步变化,也就是每过一个时钟周期触发器才能发送一次改变;而异步复位则不是这个意思,它是说只要复位信号满足了复位要求,输出信号就会立刻置零,这样的触发器的复位与系统时钟无关。在浏览器前端里也有同步和异步的概念,哈哈哈,忘了互联网浏览器概念里的同步异步的概念了,不知道是不是一个意思。

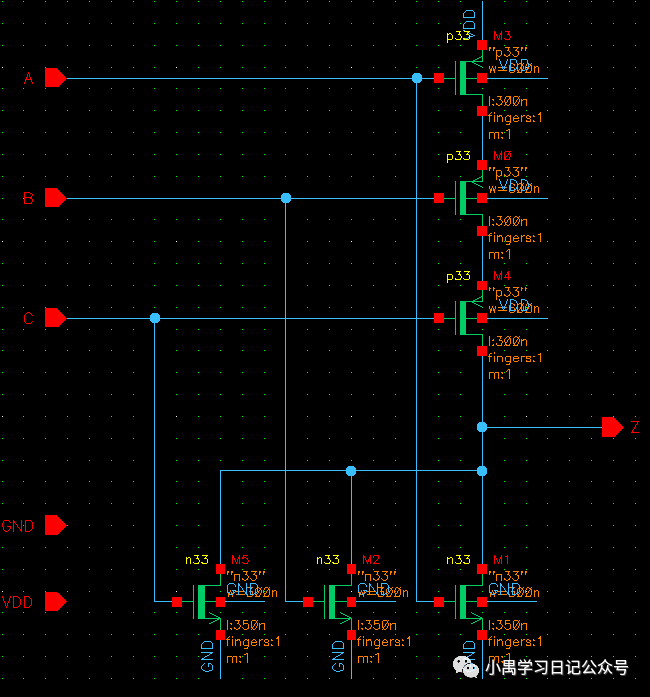

实现异步复位的关键三端口或非门

带异步复位端锁存器的结构

带异步复位端触发器的结构

2.输出端信号处理

有了对异步触发器的原理图和理解,后面我们只需要理解鉴频鉴相器后面一长串器件的功能就可以了。

由此,在这里引入一个与延时紧密关联的概念:

复位脉冲 :当输入相位差为0的情况下,鉴频鉴相器的输出QA,QB也会同时出现一段高电平脉冲信号,这样的脉冲被称为复位脉冲。

- 这个脉冲是我们所希望出现的,所以我们在这里经过与非门加一个非门的运算后,刻意又加了两个非门来做延时,由此加长复位脉冲时间。

总结与讨论

至此,我们讲述完了鉴频鉴相器的原理和功能,在下一章节中,我们将讲述电荷泵,然后结合压控振荡器的原理,综合理解一下,为什么我们需要鉴频鉴相器这样的器件;当然也可以回到我们的上一篇文章,深化理解我们为什么需要鉴频鉴相器。

鉴频鉴相器在文章中一般都没有直接展示其内部构造,为了实现这个功能,我想了一天,反复调试逻辑才最终完成了这份工作,挺有成就感的.

-

电荷泵

+关注

关注

3文章

435浏览量

30896 -

鉴相器

+关注

关注

1文章

63浏览量

23928 -

触发器

+关注

关注

14文章

2065浏览量

63582 -

输入信号

+关注

关注

0文章

559浏览量

13225 -

鉴频鉴相器

+关注

关注

1文章

11浏览量

11528

发布评论请先 登录

HMC3716LP4E数字鉴频鉴相器

EV1HMC3716LP4数字鉴频鉴相器评估板

锁相环里的鉴相器为什么能使输入输出的频率相等呢?

随机抖动时鉴频鉴相器AD9548的特性

鉴频鉴相器的工作原理解析

鉴频鉴相器的工作原理解析

评论