几年后,服务器可能看起来与现在有所不同,那时,存储和处理器会被放在彼此独立的机箱内。一种名为 CXL(Compute Express Link)的互连技术正在使这成为可能。

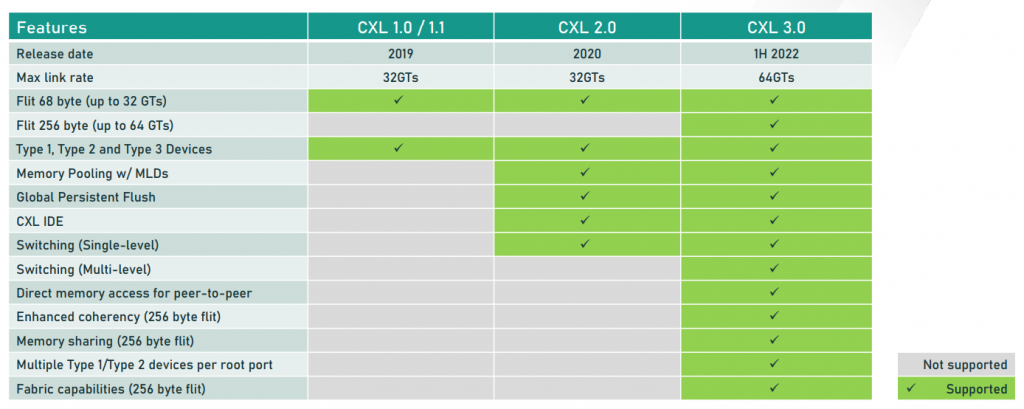

CXL是由电脑科技的行业巨头组成的联盟— Compute Express Link Consortium(CXL Consortium)所开发和定义的,主要成员包括英特尔(Intel)、AMD、三星(Samsung) 、SK海力士(SKHynix)、美光(Micron)、戴尔(Dell)、惠普企业(Hewlett Packard Enterprise)、Microchip Technolog等。CXL 协定发展经历过1.0、1.1、2.0、以及最新的3.0版本,如今市场上已经陆续出现支援CXL 1.1 和2.0 的产品,3.0 协定还在开发中;协定本身更是吸引了一群大型科技公司积极参与其中。

该技术的升级规范,3.1版,于本周发布。更新提供了更快、更安全的计算环境和更强大的技术基础,可将数据中心转变为巨型服务器。

新规范将支持 DDR6 内存,该内存仍在开发中。DDR 标准制定组织 JEDEC 尚未广泛讨论 DDR6。

目前,英特尔和AMD的服务器芯片支持DDR5,但尚未指导芯片组对DDR6的支持。大多数硬件和云提供商都支持 CXL。

CXL 3.1 是一年多前推出的 CXL 3.0 的增量改进。CXL 协议是系统中芯片、内存和存储之间的通信链路。

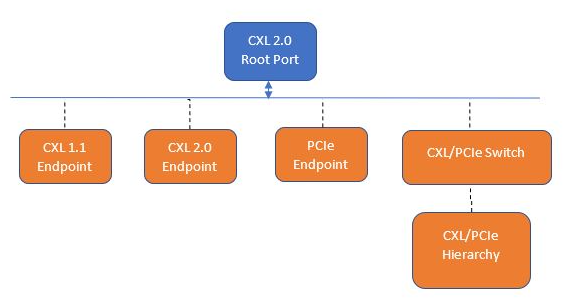

CXL 3.0 规范基于 PCIe 6.0,数据传输速度高达每秒 64 千兆。它比其前身 CXL 2.0 快两倍,CXL 2.0 基于 PCIe 5.0,并且正在进入服务器系统。

随着 AI 等技术的普及,CXL 已成为芯片组的重要组成部分,机器学习应用程序需要大量内存和带宽,CXL 允许跨服务器池化存储和内存。

CXL 3.1 协议可以打开更多的点对点通信,将内存和存储分解到单独的机箱中,通过传统网络和互连技术进行分解的讨论已经讨论了10年,CXL 提供了提供各种计算资源所需的可扩展性。

首先,CXL 3.1 规范提供了一个支持新型内存的开放标准,可以更有效地将数据重新路由到内存和加速器。

一项重要的改进是将结构上的内存资源汇集到一个全局地址下,该功能称为全局集成内存,对于在内存和其它资源之间建立更快的连接非常重要。

加速器还将能够直接与内存资源通信,基于端口的路由的新功能有助于更快地访问内存资源。

CXL 3.1 还提供了在受保护环境中执行数据的指令,引入这项技术是为了支持机密计算,英特尔的 Sapphire Rapids 中已经引入了 TDX 指令,AMD的芯片中引入了 SNP-SEV 功能。

新规范定义了一种安全协议,该协议可保证数据在内存、处理器和存储之间移动时扩展安全环境。

该协议将检测需要对连接进行身份验证以打开硬件保险库,以访问代码或信息的环境。这些信息可能位于处理器、内存或存储上。英特尔、Microsoft 和其它公司有不同类型的证明方法来验证在安全环境中访问数据的连接。

CXL的功能与特性详解

CXL是一种用于加速CPU 和设备之间资料传输的协定,主要应用于人工智能和机器学习等领域,以解决在这些应用中需要高效率的资料交互的需求。随着PCIe协定的发展,到了5.0版本后,像需要大量IO 资料交互的人工智能应用,开始遇到性能瓶颈的问题。为了突破这个瓶颈,引入了CXL协定的概念。

首先,CXL 协定解决了共享RAM的问题,在支援PCIe 协定的设备中,每个设备都拥有自己的RAM,但这些RAM无法被CPU 统一编址,因此无法直接进行调用,这导致了延迟的问题;CXL协定引入了共享RAM 的概念,允许CPU 对所有设备上的RAM 进行统一编址,从而实现了彼此之间的互相调用。

其次,CXL 协定解决了高延迟的问题,例如:CPU 和GPU之间的资料交互,需要经过多个节点,包括CPU 缓冲(Cache)、CPU RAM、PCIe 链路、GPU RAM和GPU Cache 等,这些节点和IO 频宽限制导致了延迟的增加;为了降低延迟,我们希望CPU 能够直接存取GPU 的RAM,从而避免了繁复的资料传输过程。CXL的功能特性中,CXL 2.0 版本引入了FLIT(可变长度介面传输,Flexible-Length Interface Transport) based transfers 功能,使用544 位元的FLIT 模式进行资料传输,这种模式可以降低资料传输的延迟,类似于NVMe 协定中的队列概念。

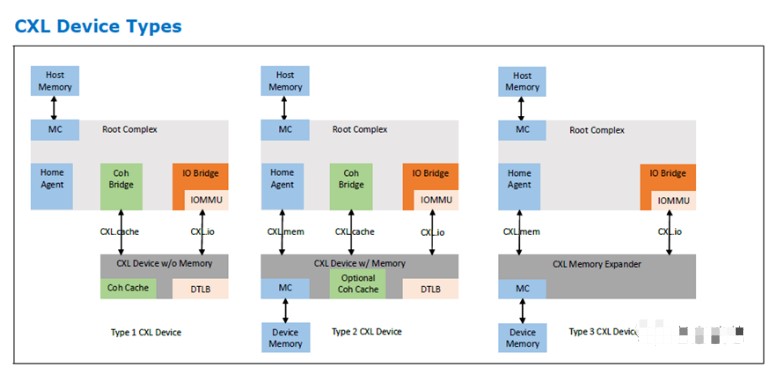

CXL的三个子协定及其对应的三种设备

CXL有三个子协定:CXL.io、CXL.cache、CXL.memory。

CXL.io 和CXL.cache 是CXL 协定中的两个子协定,它们的功能和用途有所不同,主要是为了引入非对称的概念;CXL.io 类似于PCIe 的事件(event),主要用于初始化、链接、设备发现、列举以及寄存器(register) 的存取,从某种程度上说,它可以看作是PCIe事件的一个变种。

CXL.cache 则是用于设备去使用主机的主要RAM,这表示设备可以直接存取主机的RAM,并且需要与CPU 的Cache 保持资料一致性;如果没有有效的通讯和同步,可能会出现RAM 使用冲突或不存在的问题。

另一方面,CXL.memory则是CPU 使用设备上的RAM;在这种情况下,CPU可以直接存取设备上的RAM,而不需要与设备的Cache 进行交互;这是因为CPU 的Cache 直接使用设备上的RAM,因此可以直接进行通讯,而无需额外的同步操作。

总结来说,CXL.io 和CXL.cache 的使用方向和目的不同,因此被拆分为两个子协定;CXL.io 类似于PCIe 事件,用于设备和主机之间的通讯和初始化过程;而CXL.cache 则用于设备存取主机的RAM 并保持资料一致性;另一方面,CXL.memory 则是CPU 直接使用设备上的RAM,无需与设备的Cache 进行交互,这样的设计使得CXL 协定在不同的使用情境中更具灵活性和效能。

基于这三个子协定,衍生出三种不同的设备类型;其中,CXL.io 是所有设备都需要的协定,因为它包含了设备的列举过程,使其能够被识别和通信;另外两个协定则是进行组合以产生更具特定功能的设备。

第一种设备类型是智慧网卡,它有Cache,但没有独立的RAM;相反,它直接使用CPU 的内存,这使得在CPU 处理资料时非常迅速;由于记忆体就在设备内部,它可以直接读取和处理资料,这是它的优势。

第三种设备类型则只拥有RAM,而没有Cache;换句话说,它实际上是CPU 的一种无限扩展的内存;传统CPU 主机板上的内存插槽有限,且主机板的空间有限,即使提高单条内存的容量也有限制。

审核编辑:黄飞

-

cpu

+关注

关注

68文章

10860浏览量

211723 -

内存

+关注

关注

8文章

3024浏览量

74036 -

服务器芯片

+关注

关注

2文章

122浏览量

19255 -

机器学习

+关注

关注

66文章

8416浏览量

132619 -

ddr6

+关注

关注

0文章

6浏览量

7483

原文标题:最新CXL规范支持DDR6

文章出处:【微信号:ICViews,微信公众号:半导体产业纵横】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一窥CXL协议

一文解析CXL系统架构

CXL事务层的结构是由哪些部分组成的

CXL内存协议介绍

一文详解CXL链路层格式的定义

CXL事务层详解

CXL协议和标准介绍, CXL2.0和3.0有什么新功能?

CXL 2.0设备发现的迷人路径

MIFARE DESFire EV3特性和功能与其他MIFARE的比较

关于CXL的功能与特性详解

关于CXL的功能与特性详解

评论