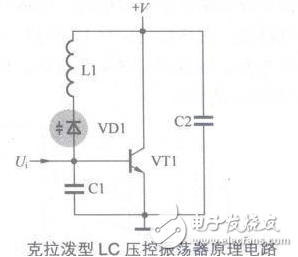

1. 奇数级振荡器

1.1 基于反相器的振荡器

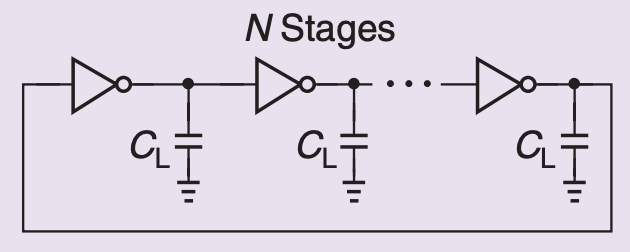

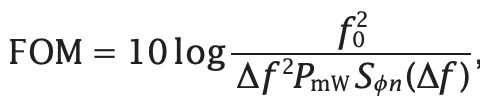

图一

如图一,假设振荡器由N级反相器组成,N必须为奇数,以保证电路DC时为负反馈。每级反相器延时TD,振荡周期为2NTD。这样的振荡器有三个特点:一,供电电压VDD越高,每级延时越短,因此振荡频率f0和供电电压VDD成正相关。二,假设每级反相器负载电容为CL,总功率约等于Nf0CLVDD^2。三,提供每级相位差为180°/N的N个输出信号(DC负反馈本身提供180°相移,那么NTD再产生180°相移,即可满足360°相移的振荡条件)。

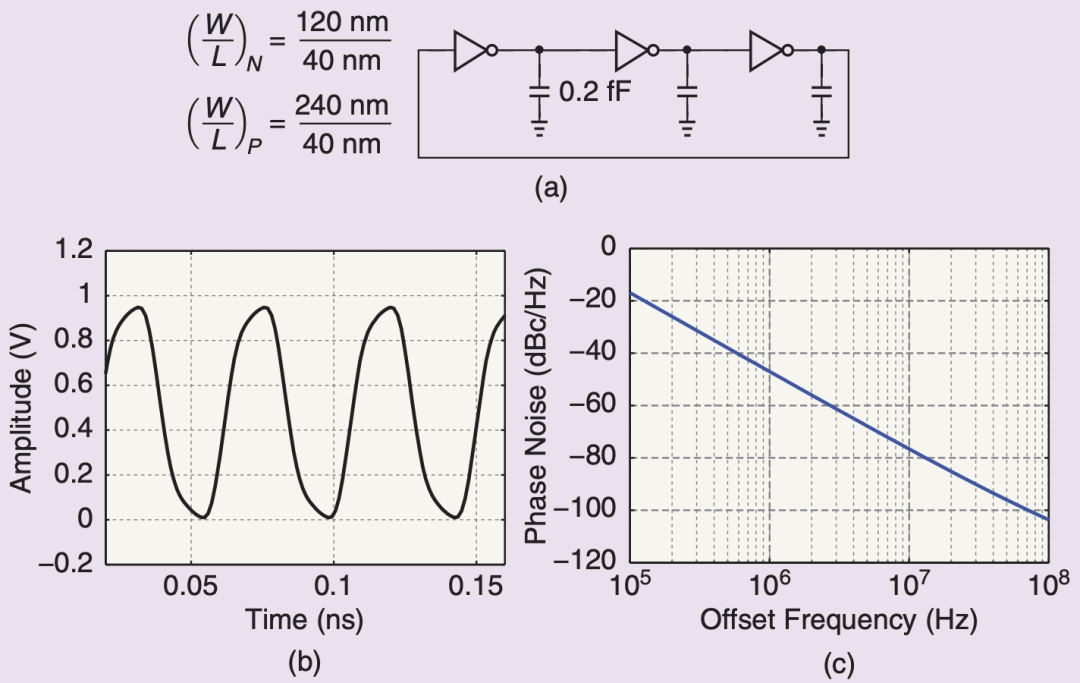

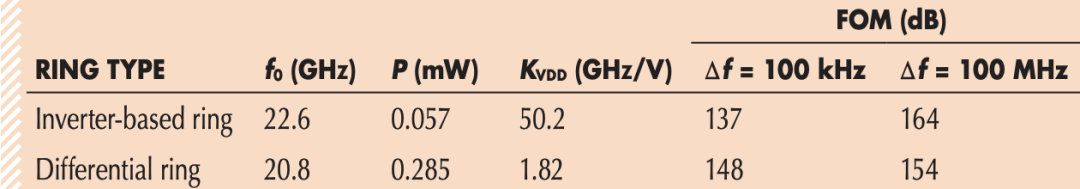

图二

原作者设计了一个实际的振荡器,如图二。具体参数如下:f0=22.6GHz,功耗57uW,电源电压到输出频率的增益KVDD=50.2GHz/V,是一个非常高的数值。如图二(c),相位噪声随着offset频率的下降速率为30dB/dec,说明闪烁噪声是主导因素。

据原文,改善相位噪声有一个方法,叫做线性缩放(linear scaling):将所有晶体管尺寸(W/L)增大到M倍,假设版图寄生可以一定比例缩放,保证f0和KVDD保持不变,那么相位噪声就可以降低10*log(M)。例如,将图二(a)晶体管尺寸增加100倍,相位噪声可以减少20dBc/Hz。这样做的代价是晶体管等效阻抗减小,为保持频率不变,各节点电容增加,那么功耗也增加了。在这个例子中功耗会增大到5.7mW。当然,面积也会同比例增加。

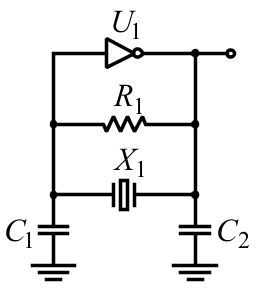

1.2 基于全差分运放的振荡器

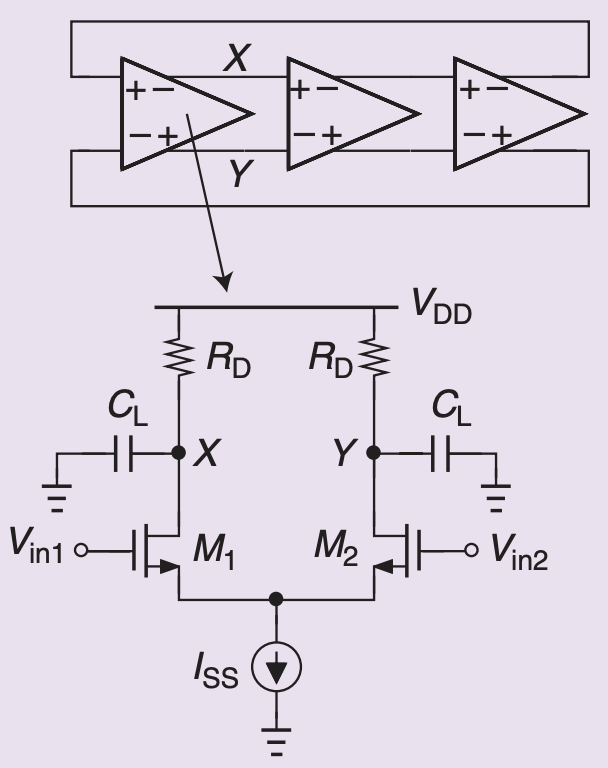

图三

如图三,这种差分振荡器和前面的反相器式振荡器有四点不同:一,对电源VDD不敏感,因为每一级延时是由RDCL来决定的。二,各内部节点,如X/Y点的单端最大摆幅为ISSRD,不能实现轨到轨输出。三,可以用偶数级实现振荡器,只需要将其中一级的输入反接。四,有静态电流。

针对第二点,有两个地方需要补充说明。一个是晶体管的尺寸选取,W/L需要足够大,这样可以保证每一级输出达到满摆幅时所需的输入差分电压小于ISSRD,那么在输入满摆幅(ISSRD)时,输入对管其中之一(M1或M2)可以完全关断。二是对于三级振荡器,即便可以实现振荡,但会因为整个环路延时太短而无法实现完全的切换,那么每个节点都无法实现满摆幅(ISSRD)振荡。根据现有文献,振荡摆幅约为0.5ISS*RD。

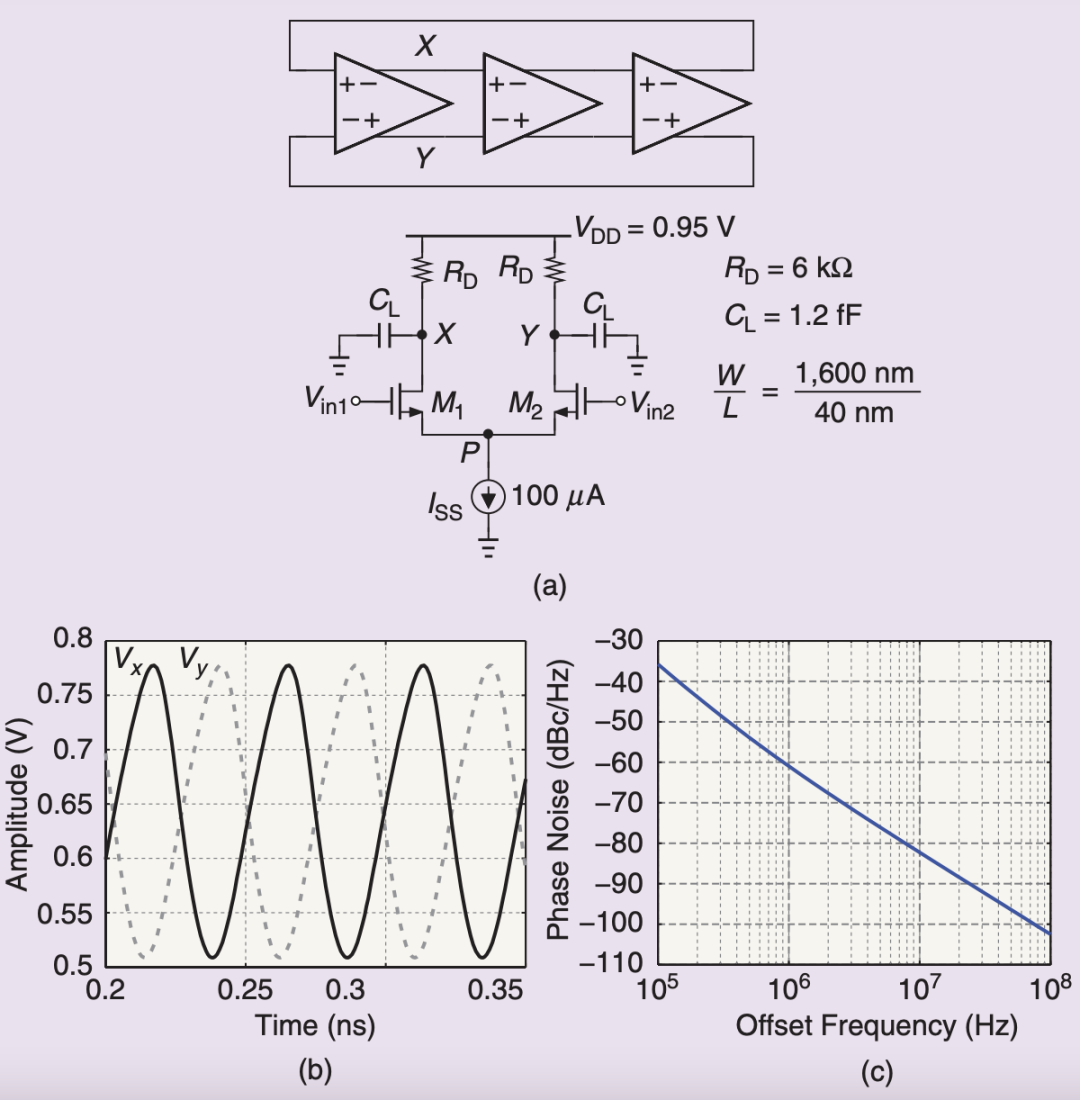

图四

作为对比,原作者设计了一个振荡频率和图二差不多的差分振荡器,如图四。f0=20.8GHz,功耗285uW,电源电压到输出频率的增益KVDD=1.82GHz/V,比图二小得多。从图四(b)看到的摆幅为270mV,和前面预估的0.5*ISS*RD=300mV差不多。根据图四(c),相位噪声的下降斜率从1MHz以下的-30dB/dec过渡为之后的-20dB/dec,意味着和图二相比,闪烁噪声的比重降低。

为了减小相位噪声,线性缩放的方法依然是可行的。在这里,需要将M1/M2的W/L和ISS增大M倍,同时将RD减小M倍。

1.3 总结与对比

为了实现两种结构的公平对比,作者定义了一个figure of merit (FOM):

其中,Δf为offset频率,PmW为功耗,Sφn(Δf)为在该offset频率下的相位噪声。FOM越大,性能越好。

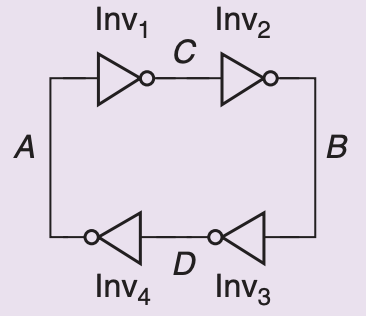

表一

表一对比了两种振荡器的差别。在Δf=100kHz时,反相器式振荡器性能更差,这是因为此时频率低,闪烁噪声显著,而反相器式振荡器的相位噪声由闪烁噪声主导。在Δf=100MHz时,差分振荡器性能更差,因为此时闪烁噪声降低,热噪声主导了相位噪声,而差分振荡器输出摆幅更小,热噪声影响更大。事实上,反相器式输出摆幅约为差分式的3.5倍(11dB),而这也和两者在100MHz的FOM之差相当。

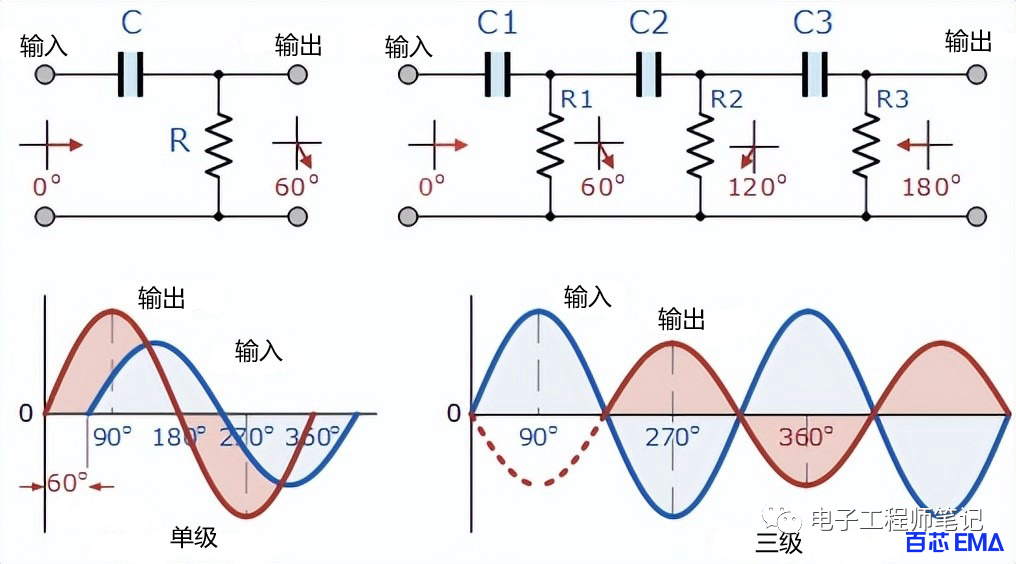

2. 偶数级振荡器

2.1 四级全差分振荡器

前面提到,全差分振荡器容易做成偶数级,只需要其中一级输入反接即可。那么在图三的基础上增加一级即可构成四级振荡器,每级相位差为45°。相比三级振荡器,由于级数增加,可以预期每级摆幅增加。然而,为了保证功耗不变,ISS需要减小。从相位噪声的角度来看,这两个因素可以互相抵消一部分。根据仿真,FOM约降低1dB。

2.2 四级反相器式振荡器

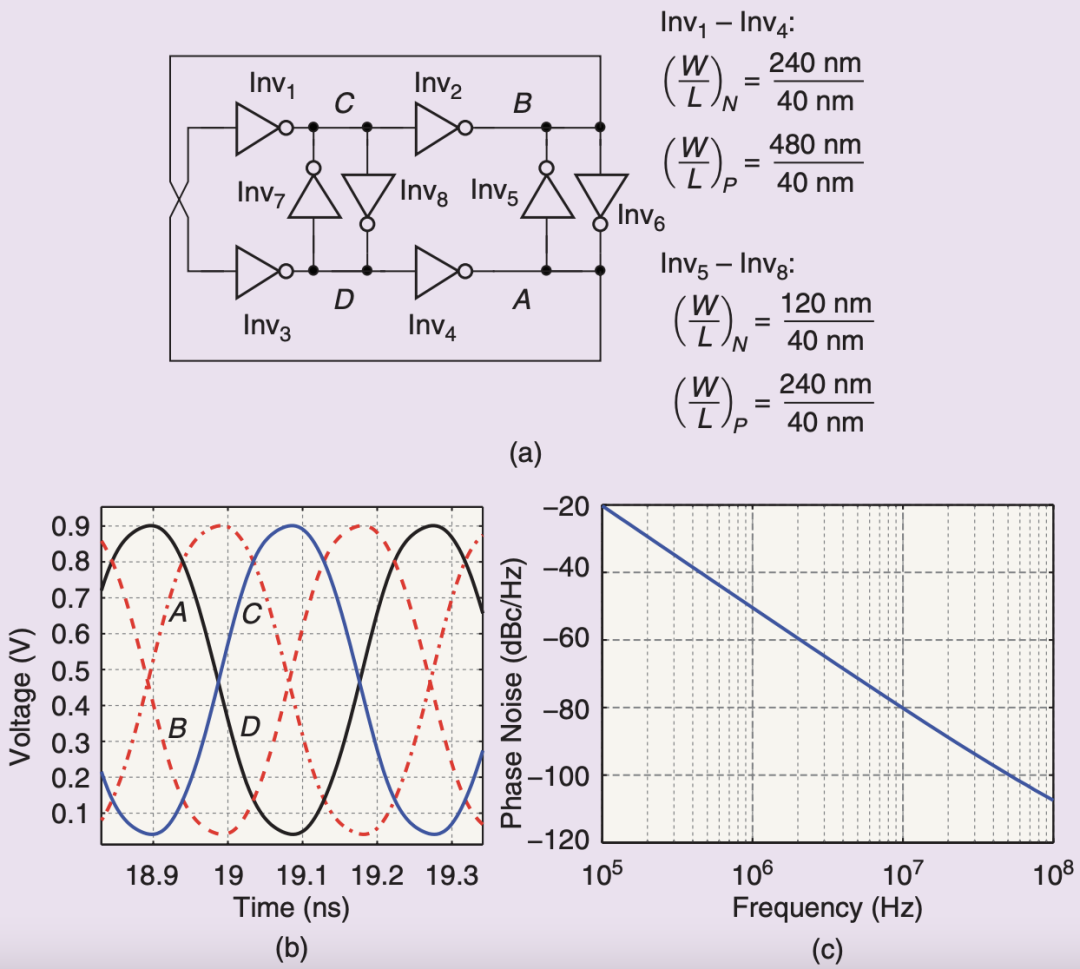

图五

反相器式振荡器一般不可直接用偶数级实现,这是因为偶数级在DC情况下是正反馈,会导致电路在DC情况被锁住。如图五,假设A=1,C=0,B=1,D=0,电路会一直latch在这种状态。但是,如果忽略这种latch的情况,电路是否有可能在某个频率振荡?答案是肯定的。假设每级延时为TD,考虑到DC正反馈未提供额外的相移,环路总延时4*TD需要达到360°则有可能振荡。那么每级相位差为360°/4=90°,振荡周期为4*TD。此时A和B相位差180°,C和D相位差180°,和DC情况下的A=B,C=D不同。那么,是否只要我们规避了DC的latch状态,就可以实现振荡?

图六

出于前面的想法,设计电路如图六。这个画法不容易看懂,但实际上就是在图五的基础上,在A/B之间和C/D之间插入inverter-based latch(Inv5 ~ 8),保证不会因为两对节点相同而在DC情况下锁住。对于Inv5 ~ 8的尺寸选取需要注意,一方面需要足够大尺寸,保证可以实现避免自锁的功能;另一方面,由于Inv5 ~ 8会和Inv14竞争,如果Inv58尺寸过大,会导致功耗和噪声增加。

图六中的设计指标如下:f0=26.5GHz,电流为235μA(三级振荡器为60μA)。根据计算,相比三级振荡器,总的FOM降低了1.5dB。这就是采用偶数级结构的成本。

-

振荡器

+关注

关注

28文章

3832浏览量

139057 -

反相器

+关注

关注

6文章

311浏览量

43304 -

负载电容

+关注

关注

0文章

139浏览量

10439

发布评论请先 登录

相关推荐

一文详解振荡器

振荡器,振荡器的分类,振荡器的特性

振荡器,振荡器的分类和原理是什么?

压控振荡器,压控振荡器是什么意思

压控振荡器电路图大全(八款压控振荡器电路设计原理图详解)

什么是皮尔斯振荡器?皮尔斯振荡器电路如何工作?

振荡器原理详解(2)

振荡器原理详解(2)

评论