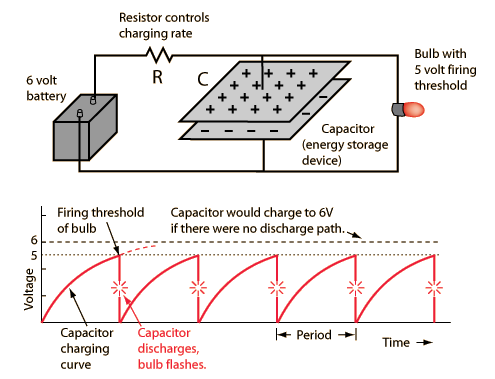

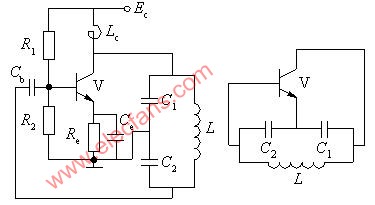

1. 传统张弛振荡器

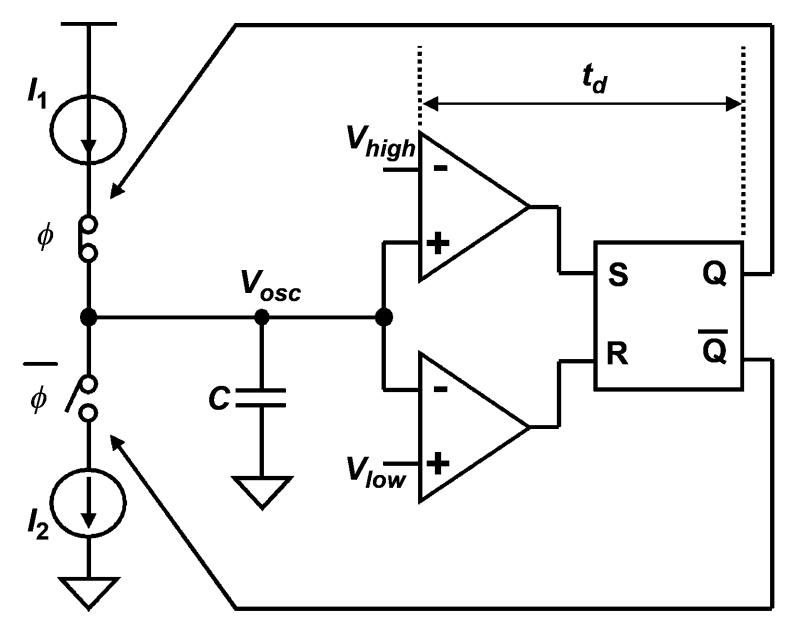

图一

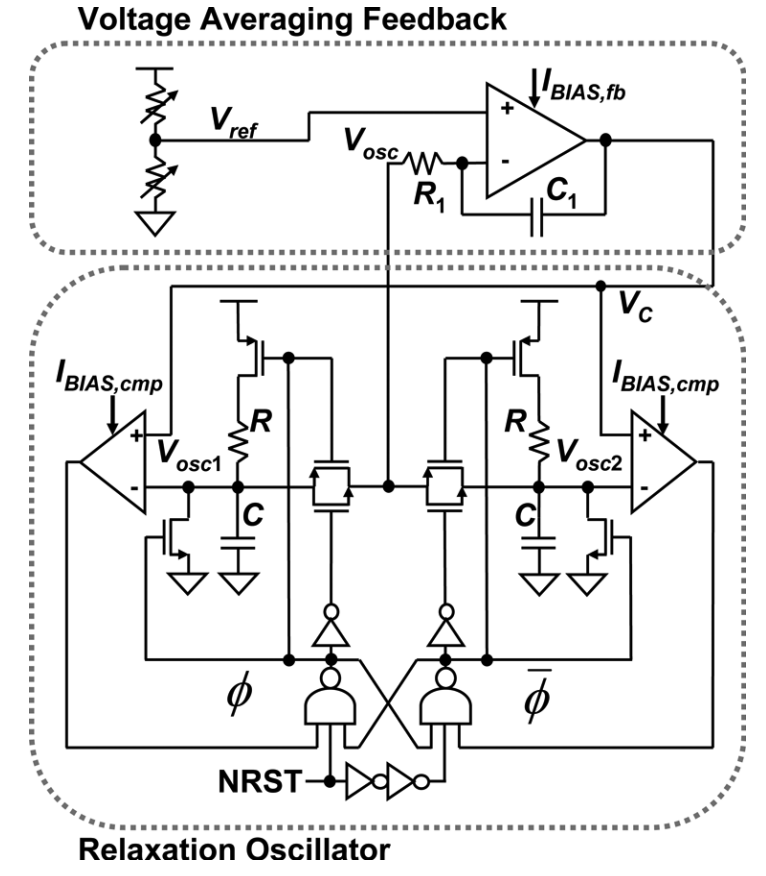

图二

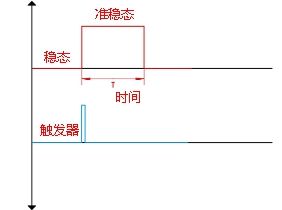

传统两比较器的张弛振荡器如图一,波形如图二,每个周期经历如下过程:

1)相位Φ:I1给C充电,Vosc上升,超过Vhigh后,上面比较器输出从0变1,触发S-R latch翻转

2)相位Φ':I2给C放电,Vosc下降,低于Vlow后,下面比较器输出从0变1,触发S-R latch翻转,重新进入相位Φ

实际上,也可以用单比较器实现张弛振荡器,不过需要在两个相位切换比较器的reference电压。无论怎样,传统张弛振荡器都有如下缺点:

1)从图二可以很明显看出,由于比较器延时td,Vosc实际翻转点偏离了Vhigh和Vlow,从而影响了振荡频率。可以算出,振荡周期=C*(Vhigh-Vlow)(1/I1+1/I2)+2td+td*(I1/I2+I2/I1)

2)由于沟道长度调制效应,I1和I2随着Vosc的变化而变化,并非恒定值,则Vosc变化斜率也不是恒定的,间接影响了振荡频率

3)I1和I2的flicker noise影响了phase noise或者jitter

2. 带平均电压反馈的张弛振荡器

2.1 电路结构

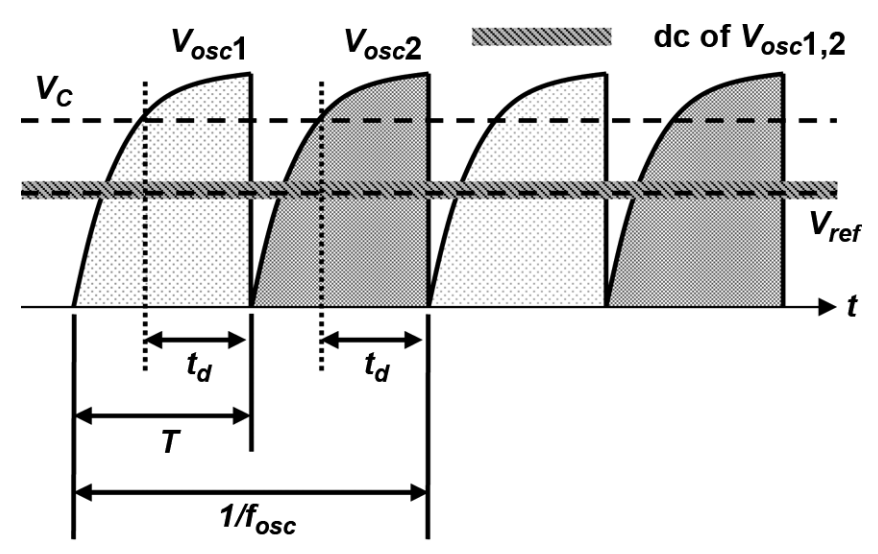

基于以上种种缺点,作者决定做两件事情:一是用 电阻替代电流源 ,二是 增加一个反馈环路来抵消比较器延时的影响。 电路结构和波形如图三和图四:

图三

图四

同样分析下每个周期的过程:

1)相位Φ:Vosc1被reset到0,左侧R-C上端PMOS关断,到Vosc的传输门关断;右侧R-C上端PMOS开启,通过R给C充电,Vosc2上升,到Vosc的传输门也开启,Vosc=Vosc2。直到Vosc2>Vc,右侧比较器输出从1变0,触发S-R latch翻转

2)相位Φ':Vosc2被reset到0,右侧R-C上端PMOS关断,到Vosc的传输门关断;左侧R-C上端PMOS开启,通过R给C充电,Vosc1从0上升,到Vosc的传输门也开启,Vosc=Vosc1。直到Vosc1>Vc,左侧比较器输出从1变0,触发S-R latch翻转,重新进入相位Φ

分析完张弛振荡器的部分,再来看反馈环路的部分:通过电阻分压产生Vref,再用积分器(R1,C1和运放)保证 Vosc的平均值等于Vref ,积分器输出端作为振荡器控制端Vc,调节振荡频率。假设比较器延时td使得振荡周期过长,Vosc平均值超过Vref,则运放输出Vc变低,降低两个比较器阈值,抵消td的影响。当然了,td也不是没有任何要求的,至少应该满足: td ,否则即便把Vc减小到0也无法抵消td的影响。另外,这里的fosc指的是Φ或者Φ'节点的振荡频率,而Vosc节点的振荡频率应该是2*fosc。

2.2 推导分析

鉴于我们是通过电阻而不是电流来给电容充电的,那么避免不了等式里会出现指数项。关于Vosc节点的振荡周期T的表达式如下:

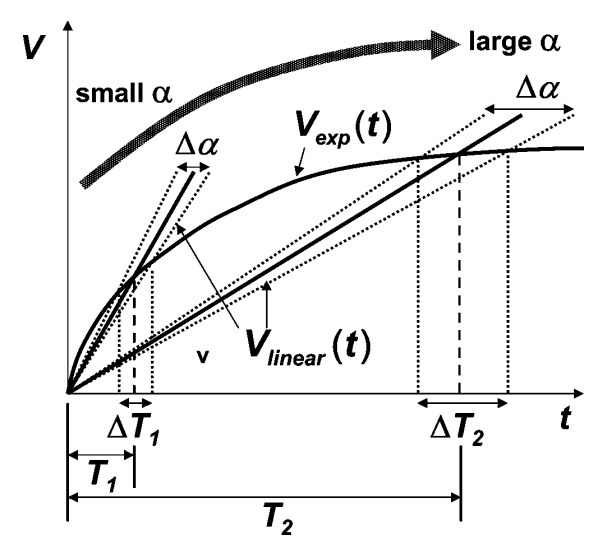

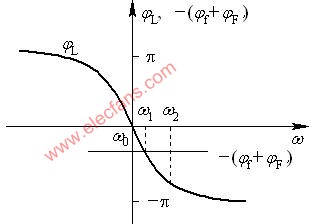

左边是关于T的线性项,右边则是指数项。为了便于大家理解,作者贴了一张图:

图五

当α小时,线性项和指数项的交点靠左,此时T较小,频率较高;当α大时,线性项和指数项的交点靠右,T较大,频率较低。笔者认为,这张图一方面展示了α或者Vref和频率的关系;另一方面,从直观上说明了,当R、C、α这些参数都固定时,上面关于T的等式有唯一解。那么,我们就可以通过调节R、C、α来调节频率了。

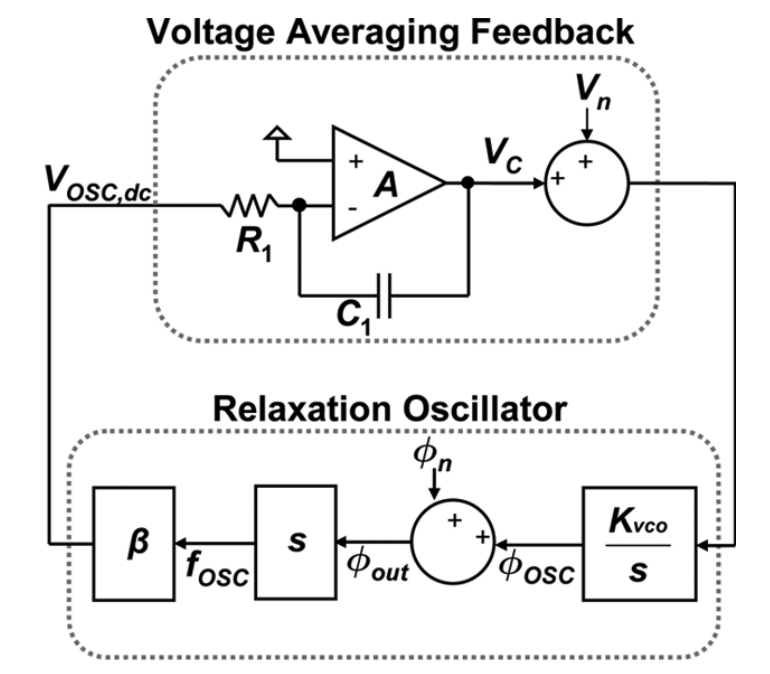

最后,可以从频域的角度建立这个系统的等效控制模型如图六:

图六

从电压Vc出发,通过VCO的系数KVCO和积分转化为相位Φosc,再通过微分转化为频率fosc,最终通过系数β转回电压Vosc,dc。很多其他带VCO的闭环系统也可以用同样的方式建模。

3. 后记

这篇文章的主要思路是:为了提高振荡器精度,对振荡节点进行积分,求平均值来控制频率。出于这种思路,可以有很多电路实现的方式,大家可以根据需求进行设计。当然,也可以通过其他方法将频率转化为电压,我会在以后慢慢补充。

-

振荡器

+关注

关注

28文章

3873浏览量

139617 -

比较器

+关注

关注

14文章

1665浏览量

107654 -

电压反馈

+关注

关注

0文章

36浏览量

14330 -

张弛振荡器

+关注

关注

2文章

2浏览量

2251

发布评论请先 登录

相关推荐

非线性或弛豫振荡器和运算放大器弛豫振荡器

非稳态多谐振荡器电路图分享

一种单电源低功耗OTA-C张弛振荡器

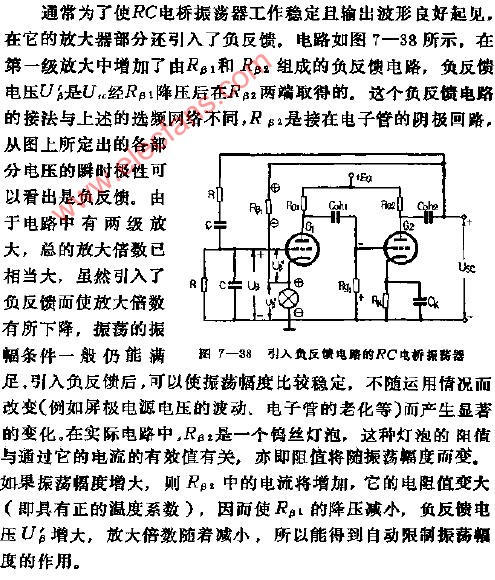

带负反馈电路的RC电桥振荡器

555振荡器计算方程及案例

一文详解单稳态多谐振荡器

带平均电压反馈的张弛振荡器详解

带平均电压反馈的张弛振荡器详解

评论