一、M-LVDS概述

1) M-LVDS:英文全称Multipoint-Low-Voltage DifferentialSignaling,中文全称:多点低电压差分信号,其主要目的是将点对点的LVDS延申用于解决多点应用问题,因此其除了LVDS的相关低功耗、差分、抗干扰等特点外,其驱动器输出的强度更高,共模范围更广。

2) M-LVDS可认为仅定义“物理层”标准,其仅定义了相关的电气特性,因此也可被其他协议标准借用为其物理层接口。

3) M-LVDS相关规范标准:TIA/EIA-899 规范。

4) 使用场景:基于LVDS的多点应用,比LVDS更强的噪声容忍,比TIA/EIA-485(RS485)或控制器局域网CAN更低的功耗、更高速的传输。

二、拓扑结构

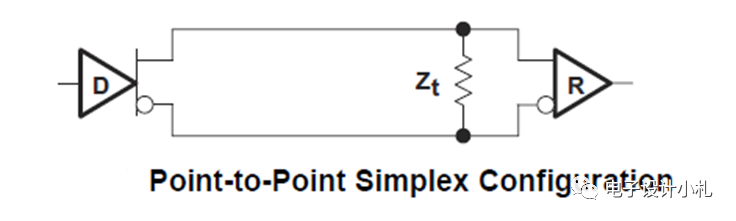

1) 点对点(point-to-point) 拓扑特征如下图所示:

1 *LVDS驱动器、

1 *LVDS接收器、

1*LVDS差分传输介质、

1 *端接匹配电阻( 放置接收器端 )、

单向通信@1组传输介质 ;

适用于TIA/EIA-644 (LVDS)。

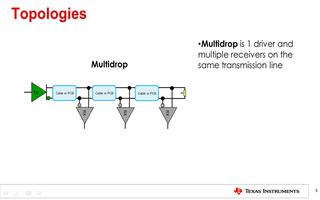

2) 多分支(multidrop) 拓扑特征如下图所示:

1 *LVDS驱动器、

N *LVDS接收器、

1*LVDS差分传输介质、

1 *端接匹配电阻( 放置在接收器最远端 )、

单向通信@1组传输介质 ;

适用于TIA/EIA-644-A (LVDS, REV A),基本上与LVDS类似(因为接收器有多个,特别规定了接收器的输入端口漏电流大小,免得多个互连时漏电流太大),不特别说明了,有时候这个也简称为MLVDS。

3) 多点(multipoint)半双工拓扑特征如下图所示:

N *LVDS驱动器、

N *LVDS接收器、

1*LVDS差分传输介质(半双工总线中使用1对2根传输介质)、

2 *端接匹配电阻( 放置在一对传输线两端 )、

半双工双向通信@1对传输介质 ;

适用于M-LVDS (TIA/EIA-899)半双工。

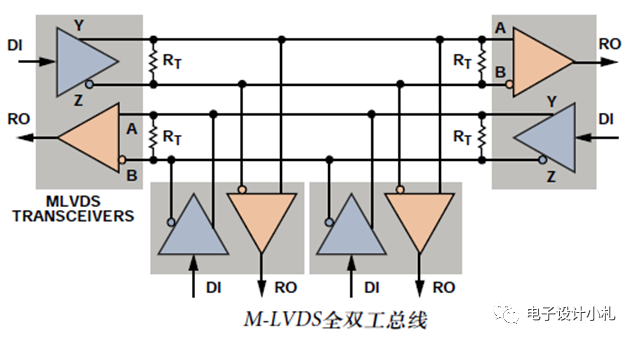

4) 多点(multipoint)全双工拓扑特征如下图所示:

N *LVDS驱动器、

N *LVDS接收器、

2 *LVDS差分传输介质(全双工总线中使用2对四根传输线)、

2*2端接匹配电阻( 2@1对传输介质两端,2对传输介质 )、

全双工双向通信@2对传输介质 ;

适用于M-LVDS (TIA/EIA-899)全双工。

三、工作原理

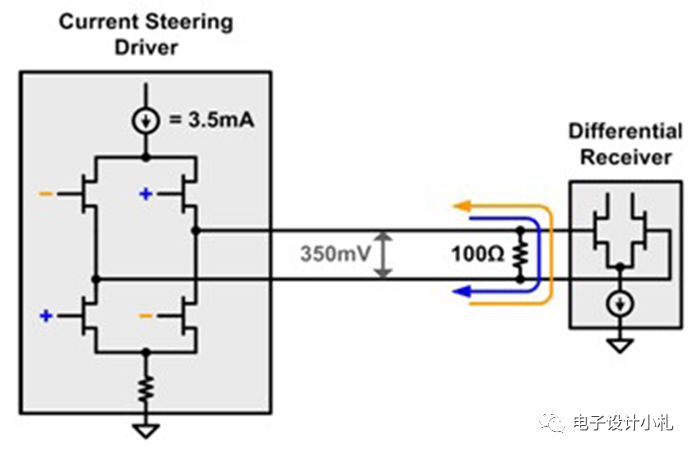

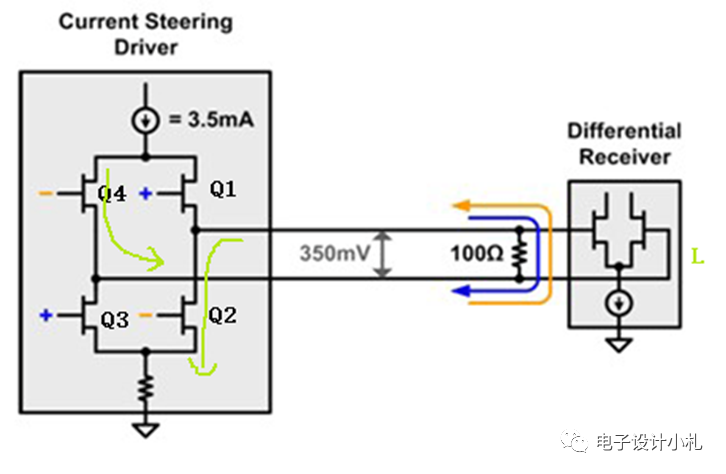

M-LVDS的工作原理是基于LVDS的工作原理,原理类似,只是参数上有区别(其中恒流源可以认为大约11.3mA,2个100Ω端接电阻等效值为50Ω,则差分输出电压差为11.3 mA 50Ω=565mV,对应的LVDS则为3.5mA100Ω=350mV),下面是LVDS的工作原理。

如上图可知,LVDS驱动端有个3.5mA的恒流源驱动,同时由4个MOS管形成了全桥开关电路,通过4个MOS管的开关,控制3.5mA恒流源输出的电流方向;而接收器端在同相和反相之间并联了一个100Ω端接电阻,通过端接电阻可产生3.5mA*100Ω=0.35V的电压压降,该压降经过接收端电平判断可形成高低电平。

依据上图的电路结构,可知LVDS是一个电流驱动型接口,需要依赖外部电阻产生电压, 如果单独测量驱动端(端口悬空)是无法测量到电压信号的 ,这与我们常规的CMOS电压驱动型信号还是有所区别的。

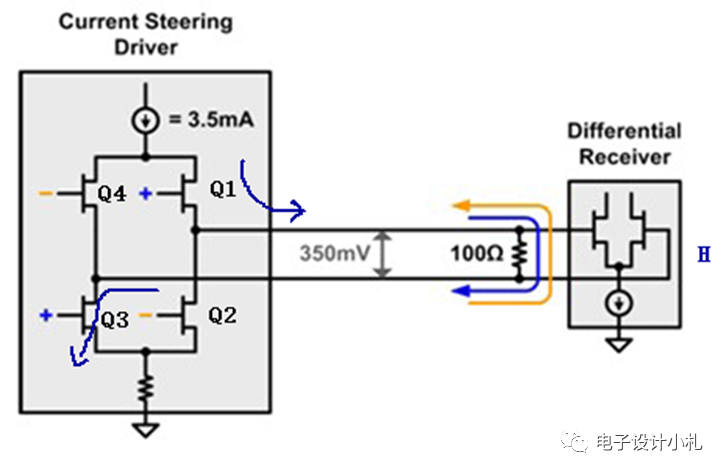

具体高电平产生示意如下图蓝色箭头所示,当Q1和Q3导通,Q2和Q4截止,恒流源3.5mA电流分别经过Q1、100欧端接电阻、Q3,最后经过偏置电阻到GND,接收端输入阻抗较大,则3.5mA基本全部经过100欧电阻,形成了350mV的正向电压差,即认为输出为“H”。

具体低电平产生示意如下图橙色箭头所示,当Q2和Q4导通,Q1和Q3截止,恒流源3.5mA电流分别经过Q4、100欧端接电阻、Q2,最后经过偏置电阻到GND,一般接收端输入阻抗较大,则3.5mA基本全部经过100欧电阻,形成了350mV的负向电压差,即认为输出为“L”。

四、电气特性

1)输出特性(对发送端来说)

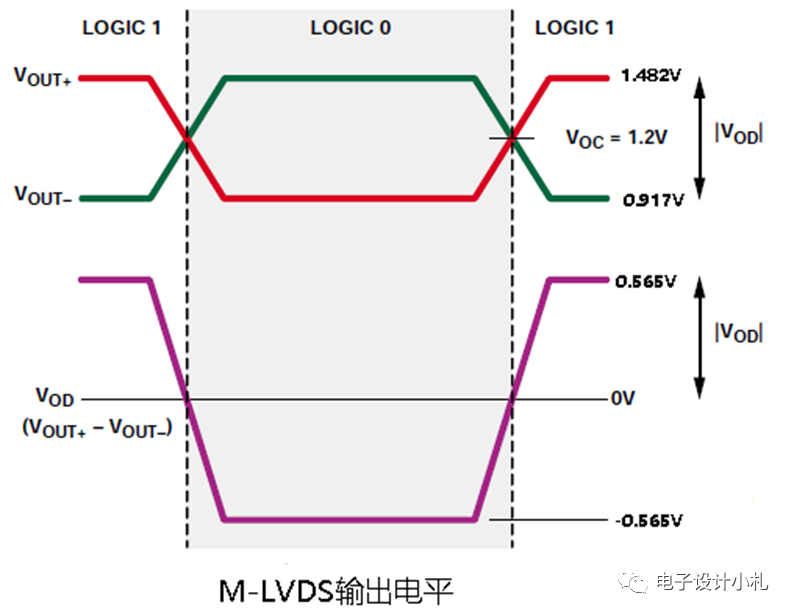

如上图所示,对M-LVDS而言,正端输出信号VOUT+:逻辑1为高电平,逻辑0为低电平,负端输出信号VOUT-:逻辑1为低电平,逻辑0为高电平。

这里面有两个概念,一个是差模电压,一个是共模电压,其中:

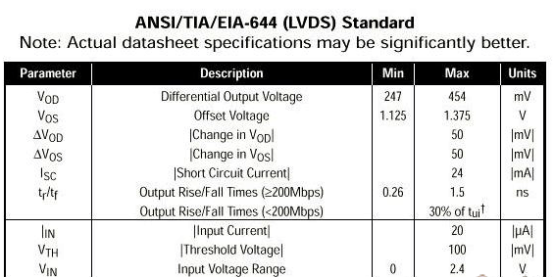

M-LVDS差模电压=“VOUT+”与“VOUT-”之间的电压差,可为正,也可为负,通常以|VOD|表示;VOD按照上文的原理分析,M-LVDS一般电压差为565mV,但是在实际过程中有个范围(如下图),一般在480mV~650mV之间。

M-LVDS共模电压=“VOUT+”与“VOUT-”的中心电压,通常以VOC表示,共模电压在实际不同的芯片中也有不同,通常情况下对于2.5V/3.3V/5V供电的设备,其VOC一般为1.2V,但是对于1.8V供电的设备,其VOC一般可能为0.9V。

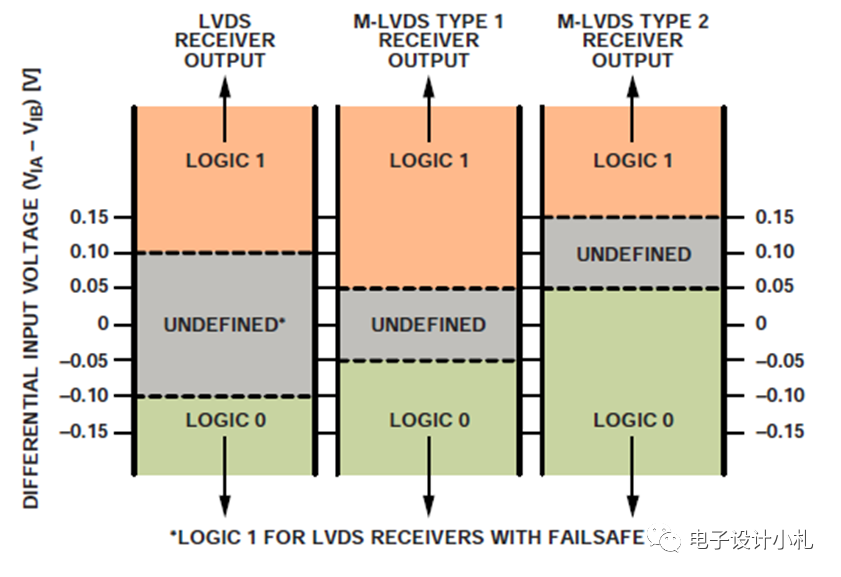

2)输入特性(对接收端来说)

对于接收端来说,也有同样的共模电压VIC和差分电压VID概念,接受端针对这两个特性分别有要求,其中:

M-LVDS差分电压会有个判决门限(如下图所示),正VID >= +50 mV对应于逻辑1,负VID <= −50 mV则对应于逻辑0,这种±50mV判决门限的M-LVDS为TYPE1类型M-LVDS。

需要特别说明的是,如果差分电压在两个阈值之间,则M-LVDS接收器输出为未定义态,可能为高电平或低电平,比如说M-LVDS接收器件输入端短路或者开路时。为了编码这种情况,定义了TYPE2 型M-LVDS接收器,被称为fail-safe,具体原理参照前面的这篇文章。

需要重点说的是,由前面的介绍可以知道,M-LVDS信号为电流驱动型,通常采用直流耦合的方式进行, 因此M-LVDS的发送端和接收端是需要进行共地处理的,这块尤其注意,只不过对于共地的要求不是特别高,允许两端有一定的地电势差 ,通常允许两端的地电势差在±1V之间。

3)传输线

M-LVDS传输线可以为导线,也可以为PCB走线,因为其驱动电流较LVDS更大,因此其走线长度较LVDS更长,可达20m以上,其传输速率能够达到400Mbps这样的速率,当然传输速率与传输距离是成反比的,当传输线长度20m时,速率最大200Mbps左右,准确的距离还受传输介质、阻抗匹配等影响,需要通过仿真去评估。

五、应用说明

1) 应用场景:多点半双工/全双工传输、低功耗,M-LVDS速率最高可>400Mbps,传输距离最长可达到20m左右,但需要关注速率、传输介质与传输距离的关系等;

2) 原理图设计时,需要关注每对传输介质两端均并联端接100欧电阻,同时关注M-LVDS相关设备的共地情况,必须确保各设备的共地电势差小于1V;

3) PCB设计时,主要关注差分信号的等长、阻抗匹配,以及端接电阻两端放置,其他收发器尽量距离主传输线较近。

六、LVDS与M-LVDS对比说明

| 类别 | 参数 | LVDS | M-LVDS |

|---|---|---|---|

| 拓扑 | 拓扑 | 点对点 | 多点(最多32个) |

| 驱动器数量 | 1个 | 多个 | |

| 接收器数量 | 1个 | 多个 | |

| 端接电阻 | 1个@接收端 | 2个@两端 | |

| 通信方向 | 单向@1对传输线 | 半双工@1对传输线全双工@2对传输线 | |

| 发送 | 驱动电流 | 3.5mA | 11.3mA |

| 差分电压VOD | 350 mV250mV~450mV | 565mV480mV~650mV | |

| 共模电压VOC | 1.2V | 1.2V | |

| 接收 | 判决门限 | ≥100mV—H≤-100mV—L | ≥50mV—H≤-50mV—L@type1≥150mV—H≤50mV—L@type2 |

| 共地漂移 | ±1V | ±1V | |

| 传输 | 速率 | 最大3.125Gbps | 最大400Mbps |

| 距离 | 最大10m | 最大20m |

-

驱动器

+关注

关注

54文章

9111浏览量

156436 -

接口

+关注

关注

33文章

9588浏览量

157591 -

电平

+关注

关注

5文章

373浏览量

41772 -

差分信号

+关注

关注

4文章

409浏览量

29071 -

M-LVDS

+关注

关注

0文章

347浏览量

9801

发布评论请先 登录

M-LVDS是什么 有哪些优势

M-LVDS优化高密度系统实现紧凑模块化设计

单通道M-LVDS接收机的特性与应用

增强隔离型 M-LVDS 收发器参考设计

LVDS和M-LVDS电路实施指南

电平标准M-LVDS接口学习笔记

电平标准M-LVDS接口学习笔记

评论