一、LVDS概述

1) LVDS: 英文全称Low-Voltage Differential Signaling,中文全称:低电压差分信号,其基本特点即:“低电压”、“差分”,引申特点“高速”、“低功耗”、“抗干扰”、“低辐射”。

2) LVDS可认为仅定义“物理层”标准,其仅定义了相关的电气特性,因此也可被其他协议标准借用为其物理层接口。

3) LVDS相关规范标准:TIA/EIA-644 规范、IEEE1596.3规范。

4) 使用场景:点对点,高速数据传输,比如ADC接口、视频接口等,也可用于板内、背板、电缆等数据传输。

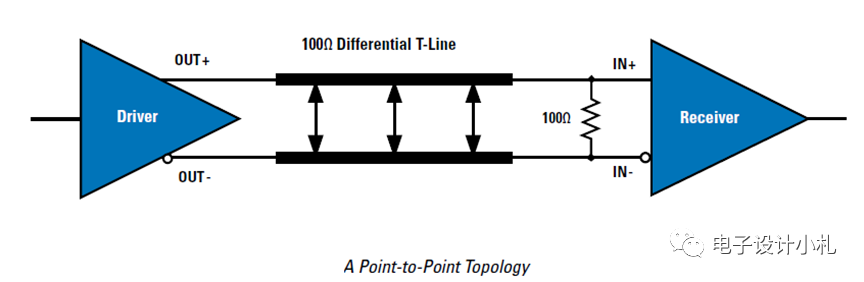

二、拓扑结构

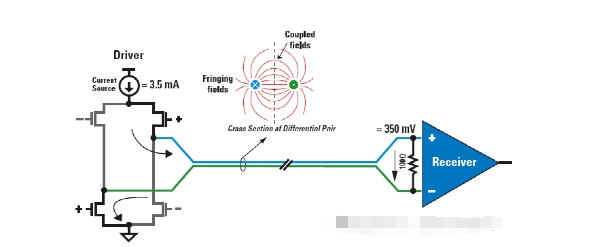

如上图,一个LVDS传输链路, 包含四种组件,LVDS驱动器、LVDS接收器、LVDS差分传输介质、终端匹配电阻 ,其中:

LVDS驱动器实现单端转差分LVDS信号;

LVDS接收器实现差分LVDS转单端信号;

LVDS差分传输线由两根(一对)差分信号线组成,可以是PCB走线、也可以是线缆;

终端匹配电阻:一般为100欧,一方面以便在接收器正负两端形成0.35V的压差,一方面作为端接电阻防止信号反射。

为了提升传输的带宽,可以选择多组LVDS传输链路进行传输,类似于PCIe的X2,X4这种。

其拓扑结构为点对点传输,对于多点传输的MLVDS这里先不考虑。

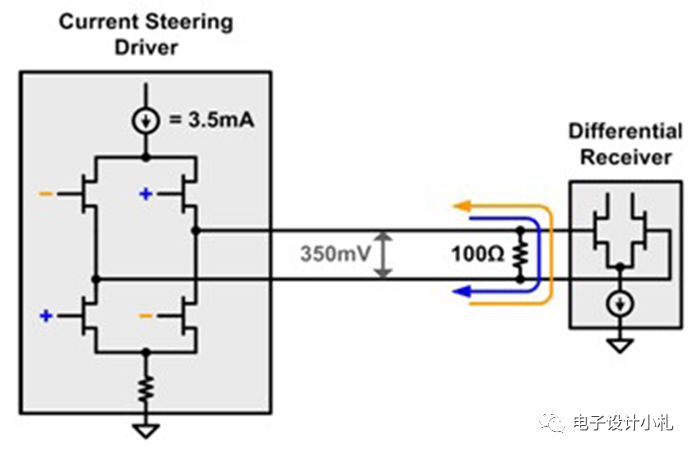

三、工作原理

如上图可知,LVDS驱动端有个3.5mA的恒流源驱动,同时由4个MOS管形成了全桥开关电路,通过4个MOS管的开关,控制3.5mA恒流源输出的电流方向;而接收器端在同相和反相之间并联了一个100Ω端接电阻,通过端接电阻可产生3.5mA*100Ω=0.35V的电压压降,该压降经过接收端电平判断可形成高低电平。

依据上图的电路结构,可知LVDS是一个电流驱动型接口,需要依赖外部电阻产生电压, 如果单独测量驱动端(端口悬空)是无法测量到电压信号的 ,这与我们常规的CMOS电压驱动型信号还是有所区别的。

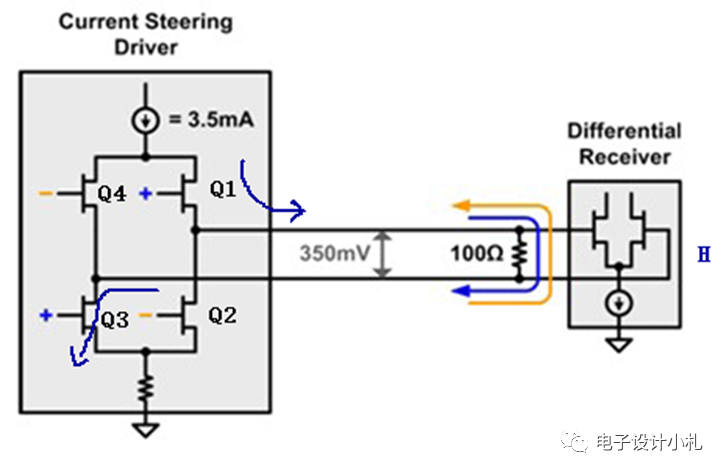

具体高电平产生示意如下图蓝色箭头所示,当Q1和Q3导通,Q2和Q4截止,恒流源3.5mA电流分别经过Q1、100欧端接电阻、Q3,最后经过偏置电阻到GND,接收端输入阻抗较大,则3.5mA基本全部经过100欧电阻,形成了350mV的正向电压差,即认为输出为“H”。

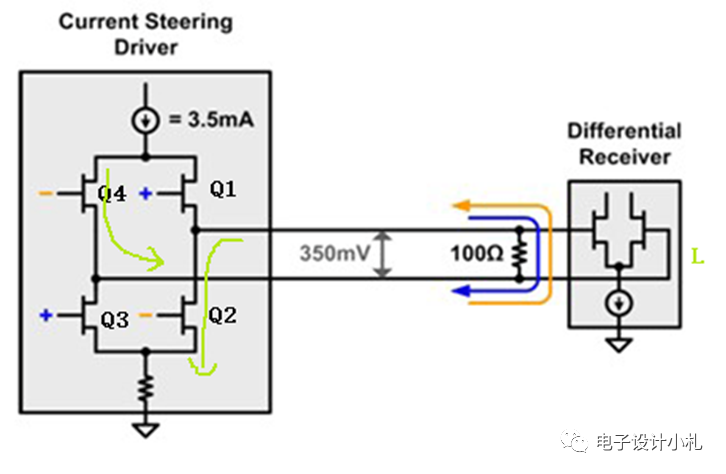

具体低电平产生示意如下图橙色箭头所示,当Q2和Q4导通,Q1和Q3截止,恒流源3.5mA电流分别经过Q4、100欧端接电阻、Q2,最后经过偏置电阻到GND,一般接收端输入阻抗较大,则3.5mA基本全部经过100欧电阻,形成了350mV的负向电压差,即认为输出为“L”。

四、电气特性

1)输出特性(对发送端来说)

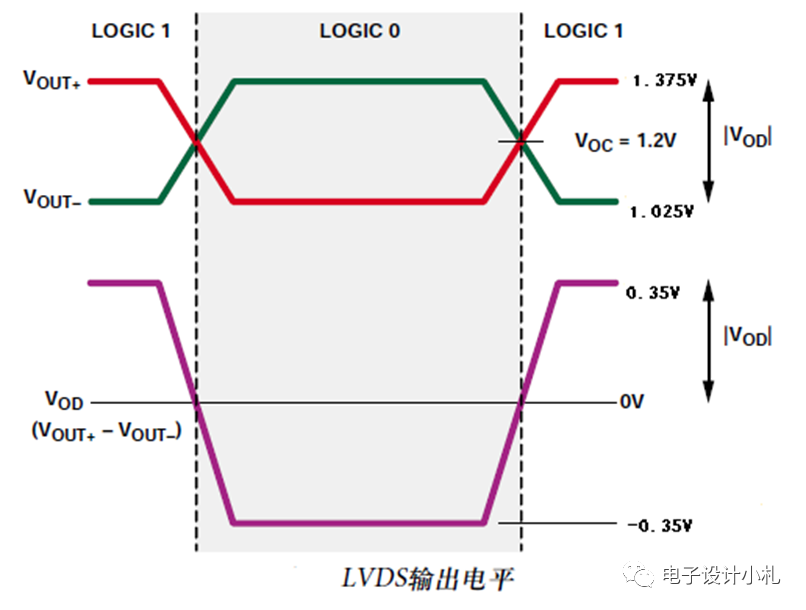

如上图所示,对LVDS而言,正端输出信号VOUT+:逻辑1为高电平,逻辑0为低电平,负端输出信号VOUT-:逻辑1为低电平,逻辑0为高电平。

这里面有两个概念,一个是差分电压,一个是共模电压,其中:

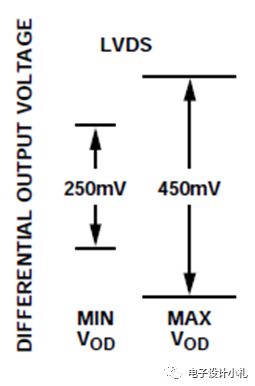

差分电压=“VOUT+”与“VOUT-”之间的电压差,可为正,也可为负,通常以|VOD|表示;VOD按照上文的原理分析,一般电压差为350mV,但是在实际过程中有个范围(如下图),一般在250mV~450mV之间。

共模电压=“VOUT+”与“VOUT-”的中心电压,通常以VOC表示,共模电压在实际不同的芯片中也有不同,通常情况下对于2.5V/3.3V/5V供电的设备,其VOC一般为1.2V,但是对于1.8V供电的设备,其VOC一般可能为0.9V。

2)输入特性(对接收端来说)

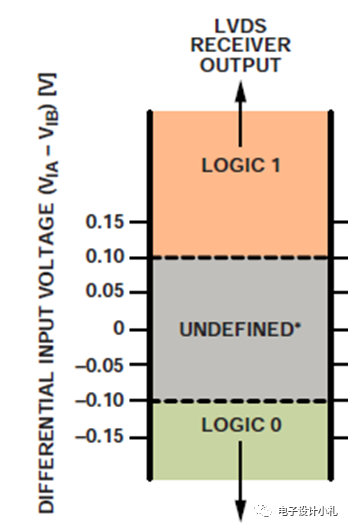

对于接收端来说,也有同样的共模电压VIC和差分电压VID概念,接收端针对这两个特性分别有要求,其中:

差分电压会有个判决门限(如下图所示),正VID >= +100 mV对应于逻辑1,负VID <=−100 mV则对应于逻辑0。

需要特别说明的是,如果差分电压在两个阈值之间,则LVDS接收器输出为未定义态,可能为高电平或低电平。比如说LVDS接收器件输入端短路或者开路时,就会发生这种情况,现在新一代的LVDS接收器通常会避免这样的情况,被称为fail-safe, 具体参照前面的这篇文章。

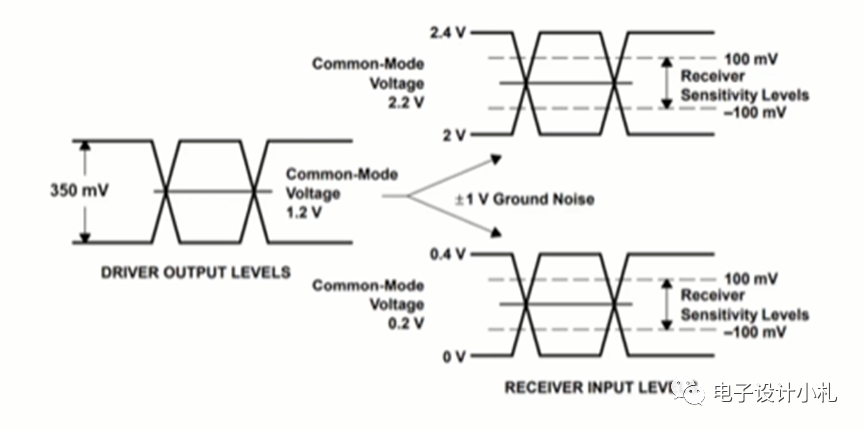

需要重点说的是,由前面的介绍可以知道,LVDS信号为电流驱动型,通常采用直流耦合的方式进行, 因此LVDS的发送端和接收端是需要进行共地处理的,这块尤其注意,只不过对于共地的要求不是特别高,允许两端有一定的地电势差(如下图所示) ,通常允许两端的地电势差在±1V之间。(当然现在也有一些自带隔离型的LVDS器件)

3)传输线

LVDS传输线可以为导线,也可以为PCB走线,其走线长度从几十厘米到10米这样的范围,其传输速率能够达到3.125Gbps这样的速率,当然传输速率与传输距离是成反比的,当100Mbps的时可以达到10米,当3.125Gbps时只能小几十厘米,准确的距离还受传输介质、阻抗匹配等影响,需要通过仿真去评估。

五、应用说明

1) 应用场景:点对点传输、低功耗,LVDS速率最高可>3.125Gbps,传输距离最长可达到10m左右,但需要关注速率、传输介质与传输距离的关系等;

2) 原理图设计时,需要关注接收端并联端接100欧电阻,同时关注LVDS两端的共地情况,有些时候端接电阻会内置在接受端内部;

3) PCB设计时,主要关注差分信号的等长、阻抗匹配,以及端接电阻紧贴着LVDS接收端器件放置(离发送端器件最远处)。

-

驱动器

+关注

关注

52文章

8242浏览量

146419 -

接口

+关注

关注

33文章

8611浏览量

151239 -

电平

+关注

关注

5文章

360浏览量

39907 -

lvds

+关注

关注

2文章

1043浏览量

65821

发布评论请先 登录

相关推荐

请问sn65lvds048a能否接收300MHz的2.5V LVDS电平?

lvds接口与其他接口比较

lvds接口在工业显示中的应用

lvds接口适用于哪些设备 lvds接口兼容性问题解析

lvds接口传输距离限制 lvds接口优势及劣势分析

lvds接口和HDMI的区别 lvds接口电路设计技巧

lvds接口用途与应用 lvds接口连接方法指南

当ADC3663的LVDS输出给到ZYNQ-7000的LVDS接收这两者之间可以直连吗?

edp接口和lvds接口区别 edp接口和lvds接口能混用吗

lvds接口需要驱动吗

电平标准LVDS接口学习笔记

电平标准LVDS接口学习笔记

评论