在前几篇文章中,我们详细讲解了氧化、光刻、刻蚀、沉积等工艺。经过上述工艺,晶圆表面会形成各种半导体元件。SK海力士等半导体制造商会让晶圆表面布满晶体管和电容(Capacitor)1;而代工厂或CPU制造商则会让晶圆底部排列鳍式场效电晶体(FinFET)2等三维晶体管。

1电容(Capacitor):蓄电池等储存电荷(电能)的设备,用于各种电子产品。在本文中,电容指半导体数据的存储设备。

2鳍式场效电晶体(FinFET,Fin Field-Effect Transistor):三维MOSFET的一种,因电晶体形状与鱼鳍相似而得名。

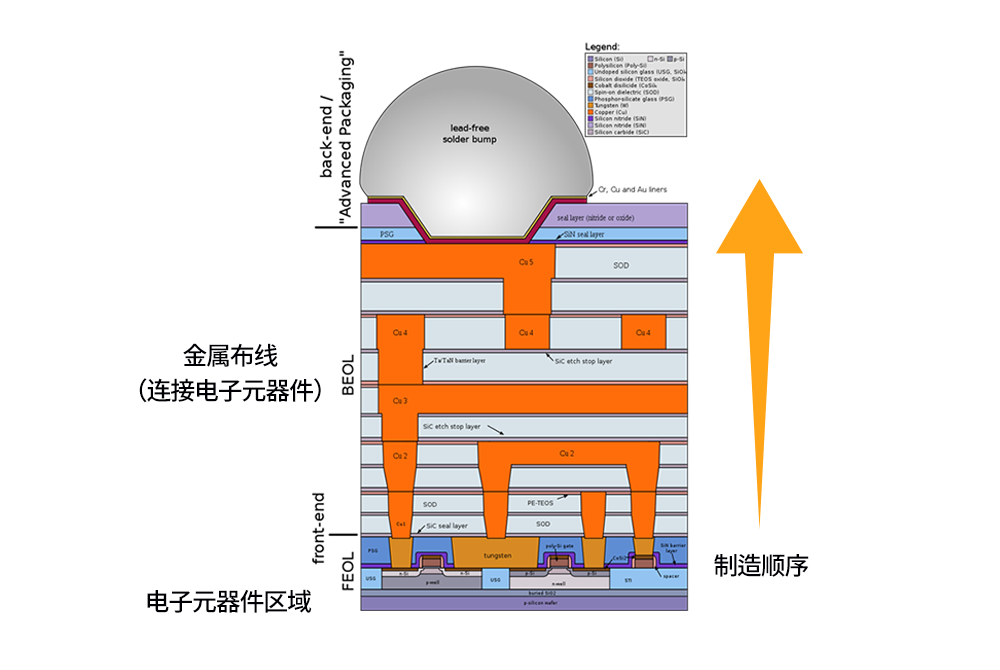

图1: 电子元器件区域与金属布线区域(摘自:Cepheiden,查看原文)

单独的元器件若不经连接,则起不了任何作用。如果不把电子线路板上的元器件焊接起来,它们就无法工作。同样地,晶圆上的晶体管若没有相互连接起来,也起不了任何作用。只有把晶体管与外部电源连接起来,它们才能各司其职,正常执行把已处理过的数据传输到下一个环节等各种工作。可见,晶圆上的元器件与电源以及其他元器件之间的连接是必要的。更何况,半导体本身就是一个“集成电路”,各个元器件之间需要通过电能来“交流”信息。根据半导体电路图连接电路的过程,就是本篇要讲的“金属布线”工艺。

相同的元器件,用不同的方式连接,也能形成不同的半导体(CPU、GPU等)。可以说,金属布线是赋予半导体工艺“目的”的一个过程。

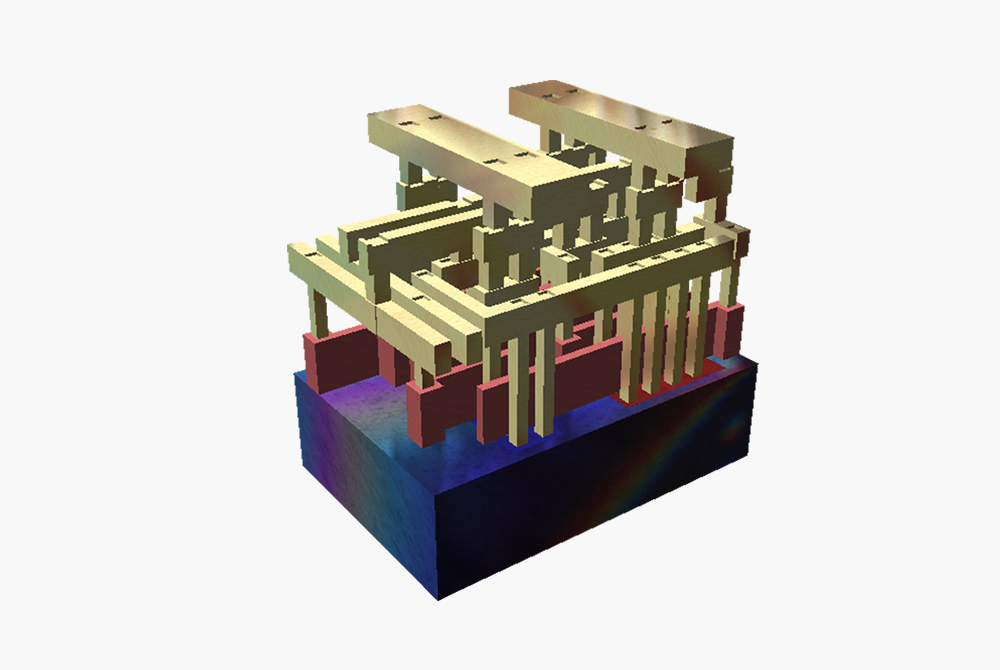

图2:以金属布线(黄色部分)连接电子元器件层(红色部分)(图中省略了部分结构)(摘自:查看原文)

本篇要讲的金属布线工艺,与前面提到的光刻、刻蚀、沉积等独立的工艺不同。在半导体制程中,光刻、刻蚀等工艺,其实是为了金属布线才进行的。在金属布线过程中,会采用很多与之前的电子元器件层性质不同的配线材料(金属)。

换言之,不像刻蚀工艺有专门的“刻蚀设备”,金属布线环节没有其专门的“设备”,而是要综合使用各个工艺环节的设备:如移除残余材料时,使用刻蚀设备;添加新材料时,使用沉积设备;每道工艺之间,则通过光刻设备进行光刻。

导线与元器件的连接:接触孔

连接电子线路板时,要先用电线连接电子线路板上的各个电子元器件后,再进行焊接。但半导体制程需要从下往上一层一层堆叠。因此,要先做好元器件层后,在其上层生成接触孔(Contact,连接元器件与导线),然后再进行金属布线。

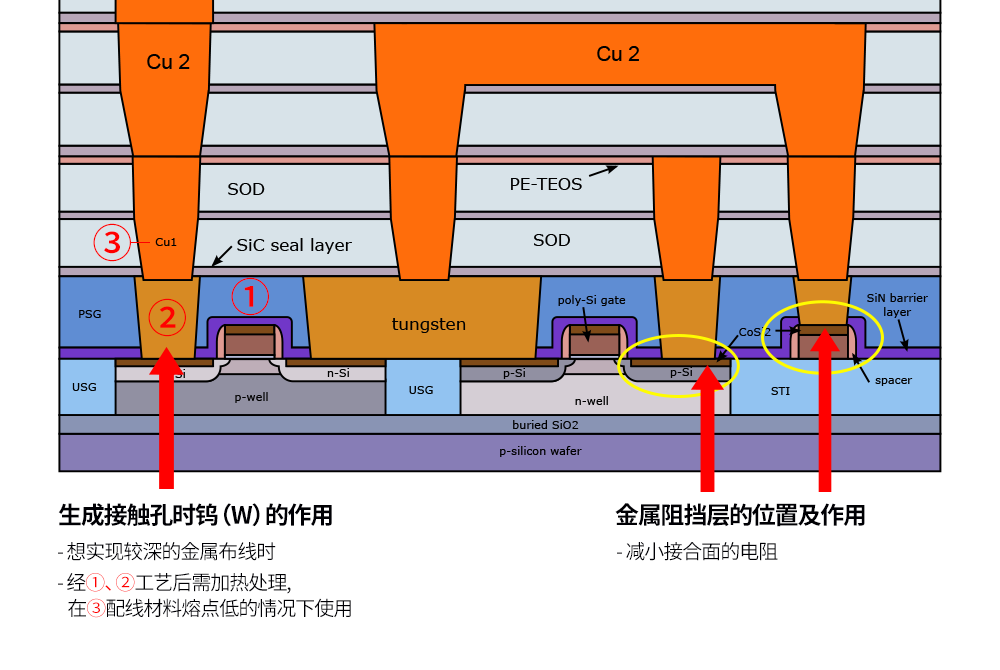

图3:生成接触孔时,钨(W)的作用与金属阻挡层的作用(摘自:Cepheiden,查看原文)

或许有些读者会好奇:为什么不跳过“接触孔”,直接把金属与元器件连接起来?这还要从半导体的微细化说起。在上一篇中,我们提到了衡量沟槽填充程度的沟槽填充(Gap fill)能力。若使用铝等配线材料,一旦穿孔稍深一些,就算“沉积”得再好,也无法把沟槽完全填充好,从而容易生产出一些中间有空隙的不良导线。也就是说,如果想实现较深的金属布线(即元器件层与金属布线层的距离较远时),就需要用钨(W)等沟槽填充能力优秀的配线材料进行沉积,提前把沟槽填充好。或者,生成接触孔后再进行高温处理。如果采用铝等熔点较低的配线材料,需要先用钨形成接合面后,再连接铝导线。

在尺度只有头发直径数千分之一的微观世界里,很多问题是我们难以想象的。为解决这些问题,我们必须比较各种对策,不断寻找最优的方案。前边提到的钨配线似乎只有优点,其实不然。作为半导体配线材料,钨远不如铜或铝。钨的电阻大,如果用它来充当所有配线材料,将大幅提高半导体的功耗。

金属阻挡层:减少金属与金属之间的电阻

元器件与接触孔之间需要能起到阻挡作用的金属层(金属或金属化合物)——金属阻挡层(Barrier metal)。连接不同性质的物质时,接合面的电阻3会变大,令半导体的功耗大幅提高。因此,在半导体制程中,有效连接金属与非金属材料的难度相当大。形成金属阻挡层的目的,便是实现非金属材料与金属材料间的“自然”过渡。要形成金属阻挡层,我们要先在硅表面涂敷钛(Ti)或钴(Co)等材料,使其与硅发生反应生成硅化物接触结构(Contact Silicide)。这一过程被称为硅化工艺(Silicidation) 。

3从物理学讲,由于金属与硅的导带(Conduction band)4 间存在能量间隙,所以会产生电阻。

4导带(Conduction Band):在固体能带结构内,以能级分裂的两个带中,用高带促进固体导电。

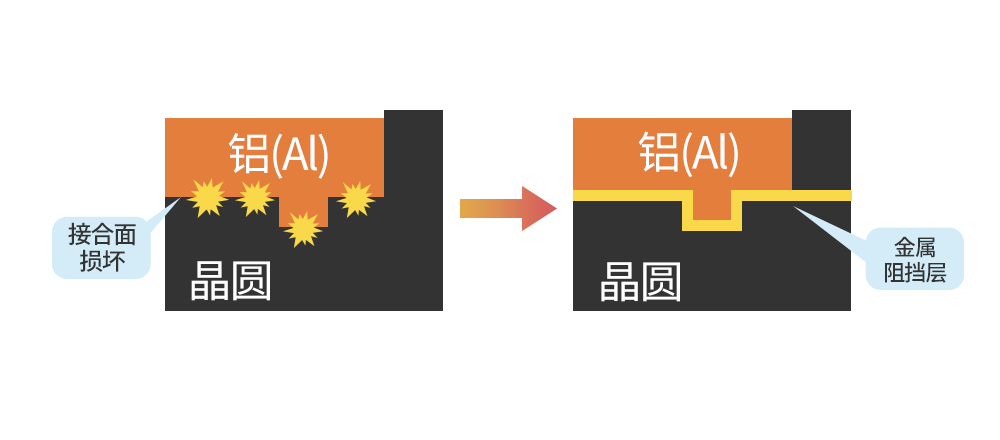

此外,金属阻挡层还可以在各工艺中保护元器件不受损。例如,铝与硅(Si,晶圆的主要成分)相遇时会发生反应,导致接合面被破坏。因此,如果想在元器件层的近处排布铝线,就必须在硅与铝接合面之间形成钛化合物等阻挡层,防止接合面被破坏。

图4:采用铝材料进行金属布线时,金属阻挡层的作用

如果以铜取代铝作为配线材料,金属阻挡层的作用就更多了。铜的反应能力比铝还强,可以与比硅更稳定的二氧化硅(SiO2)发生反应。如果铜扩散到二氧化硅里,铜粒子就会渗入到氧化膜中,造成漏电现象。为防止这种情况的发生,要用钽(Ta)在铜与元器件层接合面形成阻挡层。

导线:元器件与元器件之间的电线

生成接触孔后,下一步就是连接导线。在半导体制程中,连接导线的过程与一般电线的生产过程非常相似,即先制作线的外皮。在一般的电路连接中,直接采用成品电线即可。但在半导体制程中,需要先“制作电线”。

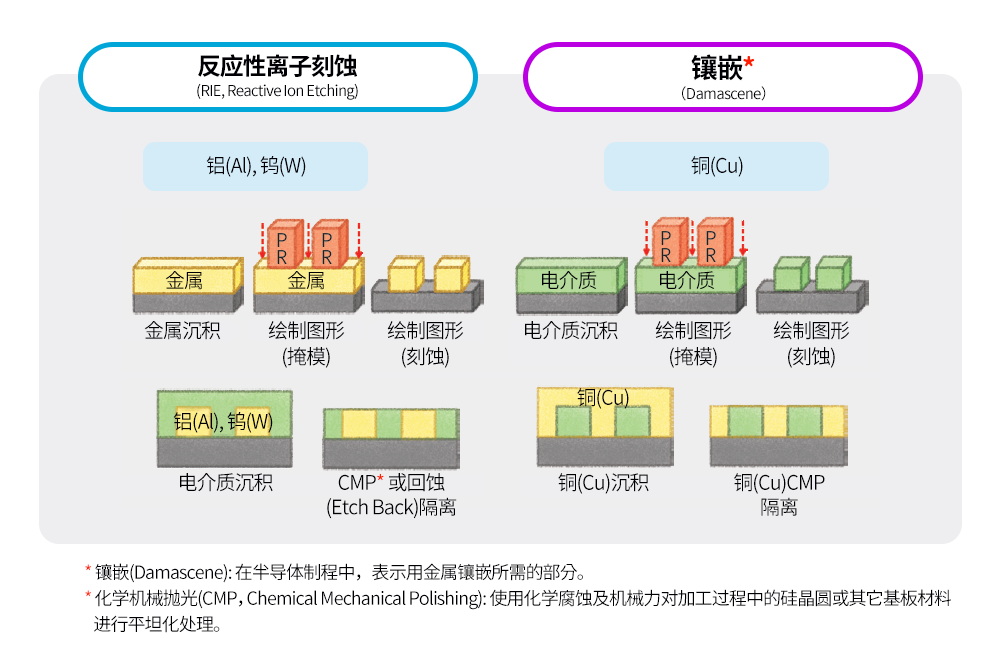

图5:反应性离子刻蚀(RIE)与镶嵌(Damascene)工艺的比较(摘自:(株)图书出版HANOL出版社[半导体制造技术的理解293p])

电线的制作过程因配线材料而异。如果沉积铝配线,可采用在前几篇文章讲述过的刻蚀和沉积工艺制作:先在整张晶圆表面涂敷金属膜,再在涂敷光刻胶后进行曝光,然后移除残余的铝材料,最后在铝周围添加各种绝缘材料。

然而,采用铜作为配线材料时,金属与电介质层的沉积顺序要反过来:即先沉积电介质层,再通过光刻工艺刻蚀电介质层,接着形成铜籽晶层(Seed Layer),在电介质层之间加入铜,最后去除残余铜。

有些读者可能会好奇:只是调换了沉积顺序,为什么这么重要?如前所述,采用铜布线,就必须涂敷铜籽晶层,为此又新加入了沉积和电镀(Electroplating,以铝作为配线材料时不需要电镀过程)等工艺。日后,为攻克铝配线带来的技术难题,除用铜(Cu)来做线材外,我们还需要研发出更多新的工艺。其实,早在100年前,人类就知道铜的导电性要优于铝。那么,当时为什么没有把铜用作配线材料?因为,从半导体制造商的角度来看,要以更低廉的成本令导线用于更多的晶体管,半导体制造工艺也需要同步发展,而当时的工艺并无法解决铜配材带来的新问题。

金属布线越往上越厚。在半导体元器件中,频繁交流庞大数据的元器件之间当然要近一些,反之则可以远些。排列较远的元器件之间,可以通过上层较厚的金属布线来进行连接。

不难看出,位于上层的较厚金属导线无需高难度技术做支撑。半导体制造商在过去制作的有一定厚度的铝导线到如今也可以直接放到上层。也就是说,上层布线无需采用尖端技术,只要沿用以往的工艺即可。这也是半导体制造商节省投资并缩短工艺学习时间的一个有效方法。

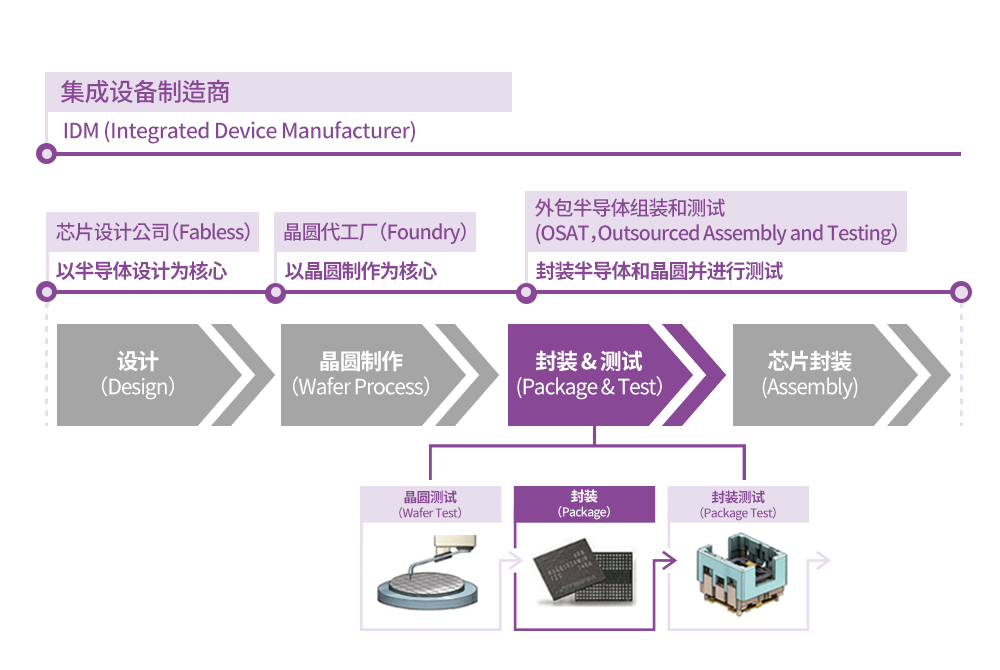

技术的组合

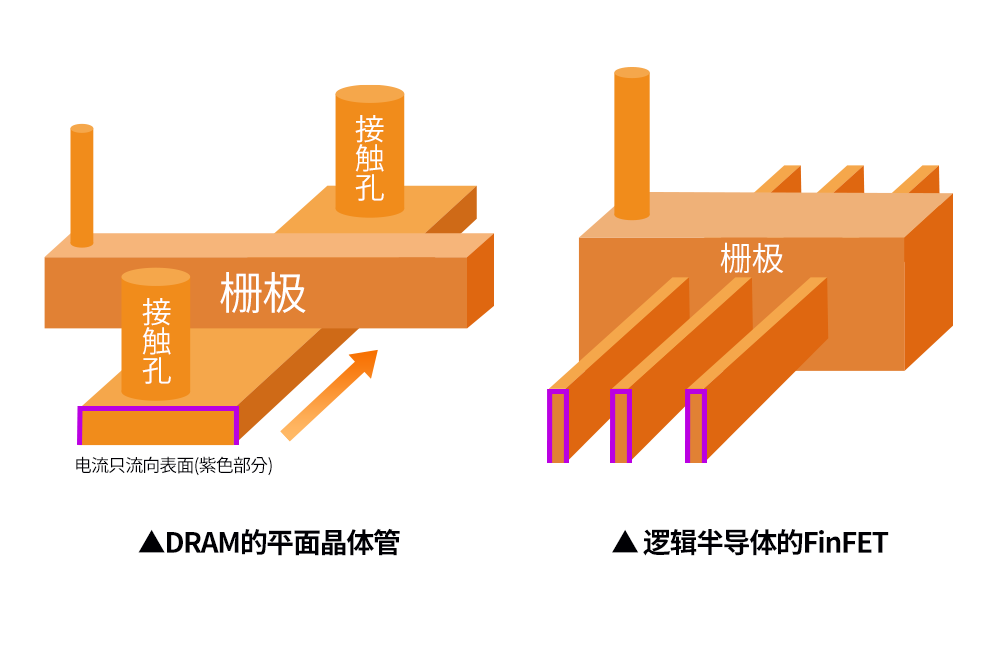

上述技术并非各自独立存在,而是根据各半导体制造商的不同目的,形成各种不同组合,从而生产出厂商希望制造的多种半导体。例如,与SK海力士等芯片制造商不同,台积电(TSMC)、英特尔等逻辑半导体5制造商对晶体管的电流控制能力要求比较高。为此,逻辑半导体制造商采用了FinFET等三维晶体管,实现了三维结构的电流,以增加电流通道的面积。在三维晶体管上生成接触孔,当然要比在DRAM等平面晶体管上难度更大。图6形象地揭示了这两种情况,左图是在平面电流通道生成接触孔,较容易;右图是在三维晶体管上生成接触孔,较难。

5逻辑半导体(logic semiconductors):CPU、GPU等通过处理数字数据来运行电子设备的半导体

图6:在逻辑半导体的FinFET生成接触孔,要远比在DRAM的平面晶体管生成接触孔难。

导线的金属阻挡层也一样,英特尔在其7纳米工艺中,为解决铜的电迁移6现象,试图用钴配线代替铜,却兜了好几年的圈子。2022年,英特尔在4纳米工艺中又重新回到原点,采用铜配线,试图通过用钽(Ta)和钴金属层包裹铜线来攻克技术难关。英特尔将此称为“强化铜(Enhanced Cu)”。

6电迁移(EM,Electromigration):指在金属导线上施加电流时,移动的电荷撞击金属原子,使其发生迁移的现象。

随着半导体的日益微细化,这种新的挑战将不断出现。对英特尔等CPU制造商来说,元器件的高速运行至关重要。正是由于CPU制造商非常重视元器件的速率,连抗电迁移性能出色的铜配线也遇到了瓶颈。英特尔的几番周折正是为了解决铜配线带来的技术难关。而像SK海力士等芯片制造商,虽然不存在电路运行速率上的问题,但却在堆叠电容维持电荷容量上遇到了难题。微细化给处于不同制造环境的制造商提出的技术难题各有不同。但可以肯定的是,SK海力士在金属布线上的难题也终将出现。

结论:“理解”先于“死记硬背”,“多人”先于“个人”

我们一起阅读了六篇文章,说长也长,说短也短。区区六篇文章,或许连半导体产业的1%都无法囊括。尽管如此,笔者仍然义无反顾地写下这六篇文章,希望能向未来将引领半导体产业的栋梁们传达几点核心信息。

半导体制程可以说是一个“集腋成裘”的过程。一张晶圆需经数百道工艺、数万人联手才能完成。尽管每一名作业人员对最终成品的贡献可能都不及1%,但任何一道工艺出现任何差错,都会影响半导体的整体运行。半导体制程中,每一名工作人员的工作都不是孤立的。我们要铭记:半导体制程的所有工艺都有机地交融在一起,牵一发而动全身。

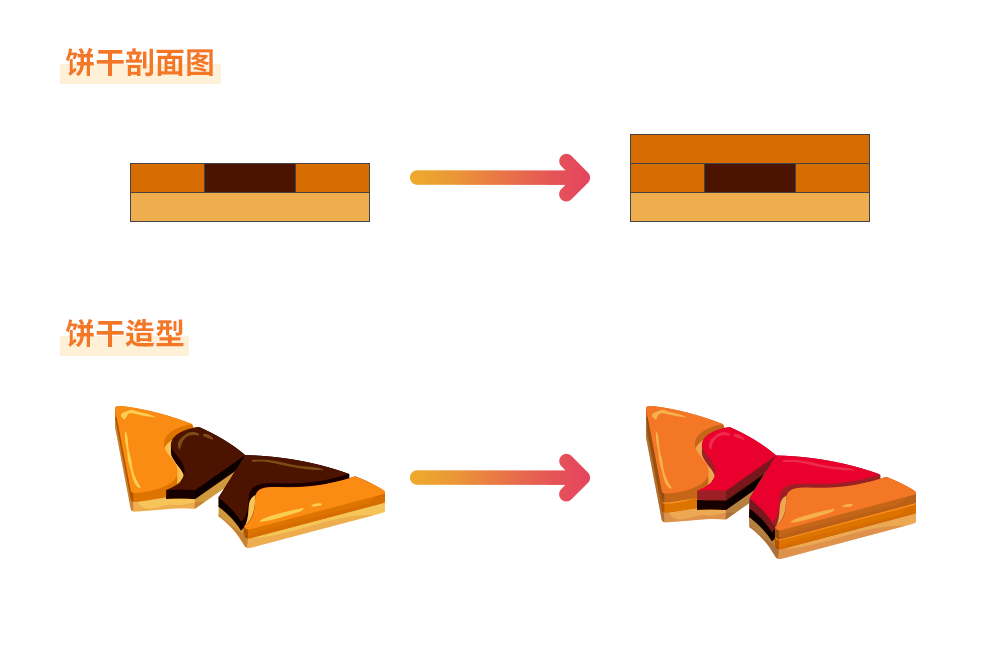

另外,我也希望读者们能通过这六篇文章认识到“理解工艺技术”的重要性。其中,理解技术彼此之间的关系尤为重要。比如,在沉积工艺中,我们要考虑到新添加的材料是否适合进行加热处理和刻蚀;充分刻蚀后,如果在后续的沉积工艺中,材料的沟槽填充能力不佳,会对整个产品产生影响;绘制微细图形时,如果***光刻不充分,就要多重曝光7,即使用掩模多次重复沉积和刻蚀。

7多重曝光(Multi Patterning): 通过重复的曝光和刻蚀工艺,追求更高图形密度和更小工艺节点的技术。

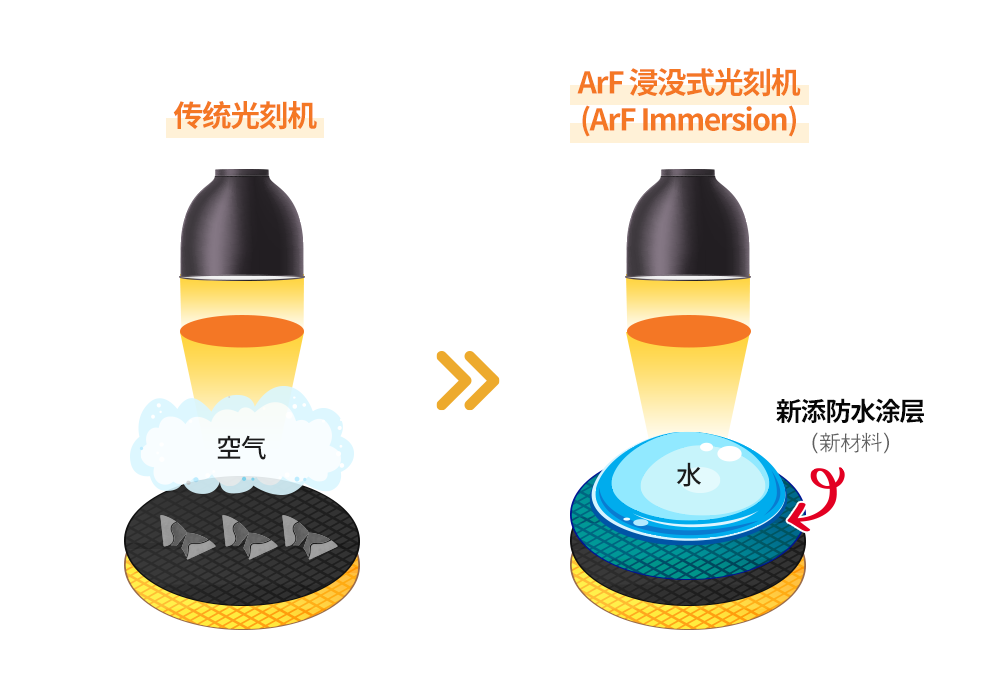

可见,半导体产业不仅是尖端产业,更是需要“可信度”的产业。从业人员需要有较高的沟通和创新能力以及正直的从业态度。在成功研发出新的微细工艺,出现各种技术难关后,要本着正直的态度,将这些新的技术难题与业界分享,然后再联合起来发挥创新能力,一同将难题攻克。半导体技术的发展是不断出现问题、不断解决问题的过程。光刻工艺中,以光刻胶解决浸没式***带来的新问题就是一个典型的案例。

图7:用光刻胶解决***带来的新问题

希望读者们能通过本系列文章对半导体产业的性质有所了解,并通过对技术的不断深耕成就自己的职业生涯,与各相关部门联手,制造出全球最有竞争力的半导体产品。

目前,半导体技术在微细化过程中再一次遇到瓶颈。越往后,半导体制造越要倾听半导体用户的声音,通过沟通实现技术研发的能力也将变得越发重要。

来源:SK海力士

审核编辑 黄宇

-

半导体

+关注

关注

334文章

27693浏览量

222187 -

电容

+关注

关注

100文章

6090浏览量

150904

发布评论请先 登录

相关推荐

有关半导体工艺的问题

半导体工艺讲座

半导体前端工艺:金属布线—为半导体注入生命的连接

半导体前端工艺:第六篇(完结篇):金属布线 —— 为半导体注入生命的连接

半导体前端工艺:第六篇(完结篇):金属布线 —— 为半导体注入生命的连接

![[<b class='flag-5'>半导体</b><b class='flag-5'>前端</b><b class='flag-5'>工艺</b>:第三<b class='flag-5'>篇</b>] 光刻——<b class='flag-5'>半导体</b>电路的绘制](https://file1.elecfans.com/web2/M00/B1/DB/wKgZomVdgPSAWsXlAAH9_6nQJHk959.png)

![[<b class='flag-5'>半导体</b><b class='flag-5'>前端</b><b class='flag-5'>工艺</b>:第一<b class='flag-5'>篇</b>] 计算机、晶体管的问世与<b class='flag-5'>半导体</b>](https://file1.elecfans.com/web2/M00/B1/DD/wKgZomVdhWOAKTH4AADK6nwzAYk943.png)

评论