作者:Paul McLellan,Cadence楷登PCB及封装资源中心

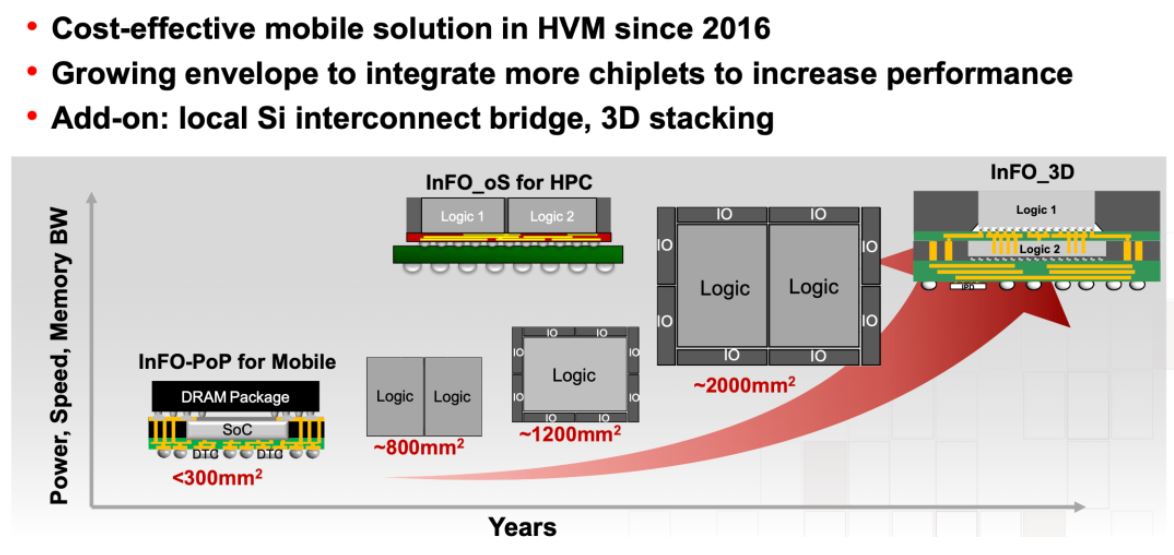

在2022年底举办的 TSMC OIP 研讨会上,Cadence 资深半导体封装管理总监 John Park 先生展示了面向TSMC InFO 技术的高级自动布线功能。InFO 的全称为“集成式扇出型封装(integrated fanout)”,是一种适用于高级封装的低性能、低复杂度的技术。下图是 TSMC 演示文稿中一张介绍 InFO 的幻灯片,不难发现,InFO 有许多不同的类型。

InFO 的首个应用实例出现在 2016 年,是用于移动应用的 InFO-PoP,在应用处理器晶粒上添加了一个 DRAM 封装。然后是面向 HPC 的 InFO_oS,允许将多个晶粒置于越来越大的封装中。最新的技术是 InFO_3D,允许逻辑和逻辑之间垂直堆叠,并在下方布线,以便分配电源分配网络和信号。

在本文中,我们不打算重申使用高级封装的优势,而是进行扩展,假设以采用最先进的节点为前提来进行设计。

如前文所述,高级封装和异构集成如今已成为所有半导体设计的热门话题。

1、布线已成为高级封装技术的主要瓶颈

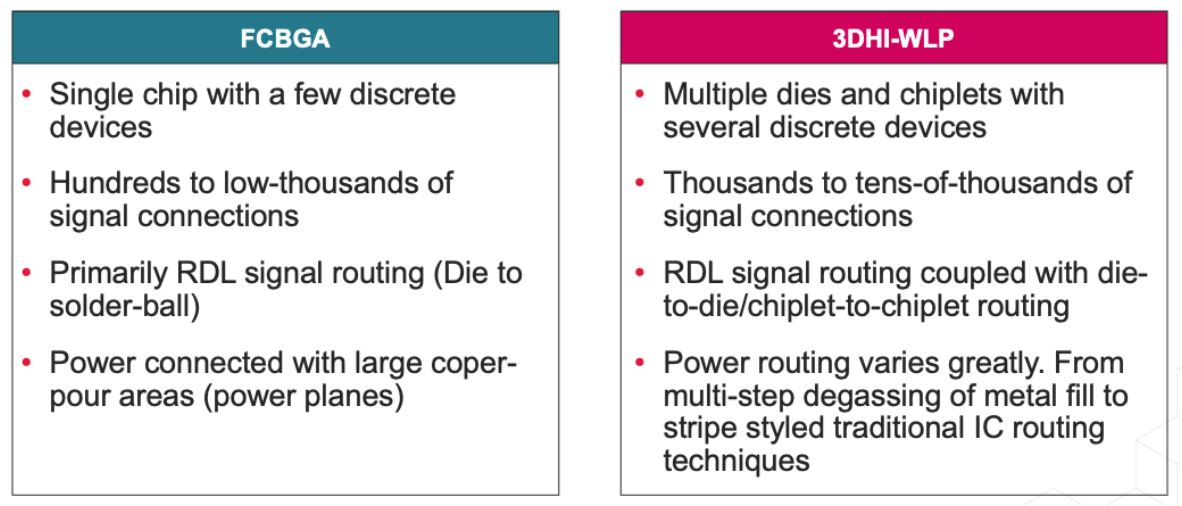

从上表中可以看出,如今的布线难度越来越大。左侧是倒装芯片球栅阵列 (FCBGA) 的要求,其中最多有几千个连接。RDL 信号布线将信号从相对较小的单个晶粒分散到焊球上。

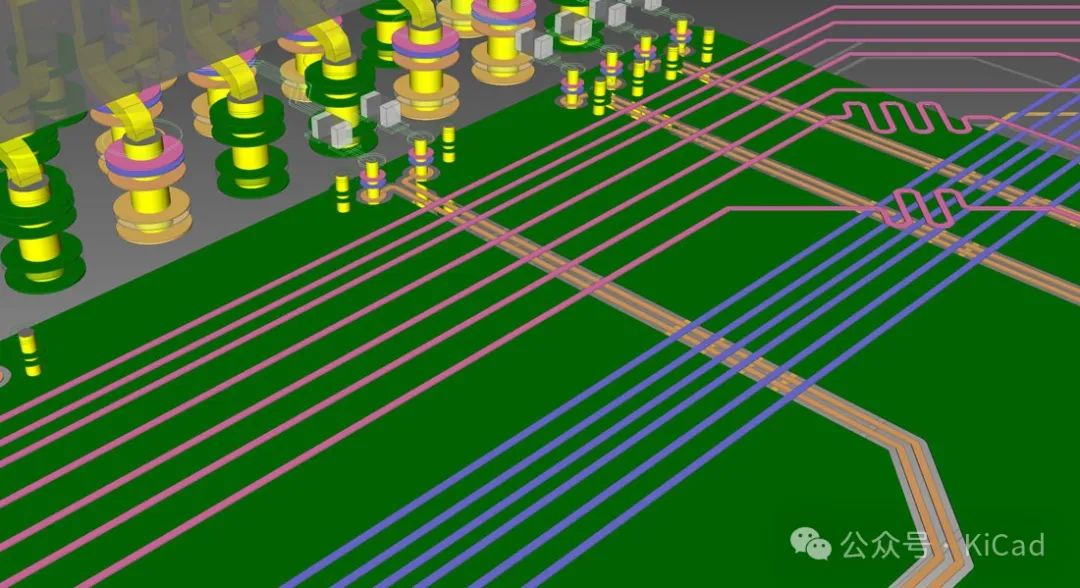

右侧是本文将要讨论的技术——3D 异构集成晶圆级封装(3D heterogeneous integration wafer-level packaging,),简称 3DHI-WLP。这种封装通常包含多个chiplets小芯片,并可能存在数万个信号连接,因此 RDL 信号布线不仅是分配信号,同时也要处理从小芯片到小芯片(chiplet-to-chiplet)的布线。电源布线同样错综复杂,多种方法均可实现。

在细节层次上,业界面临的挑战有:

小芯片到小芯片和扇出 RDL 布线要求

高效的引脚逃逸模式

布线通道密度

复杂过孔堆叠

提高良率的互连倒圆角

将信号和电源网络放在一起进行布线,以达到最佳密度

重用重复的模式

电源/接地过孔放置

为了应对这些挑战,Cadence 和 TSMC 通力合作,为 InFO 技术开发新一代——

自动信号布线解决方案

支持高容量设计的多线程自动布线引擎

支持TSMC电气、物理和良率规则的布线

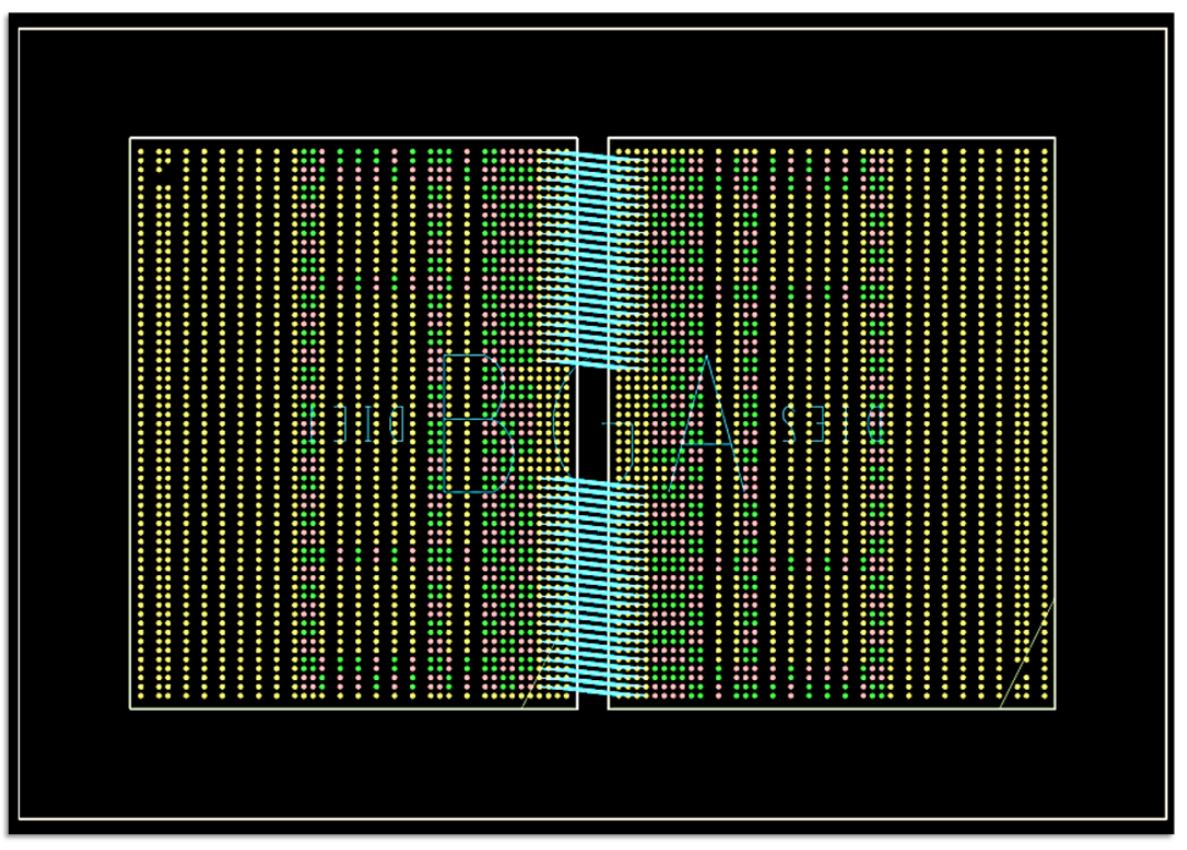

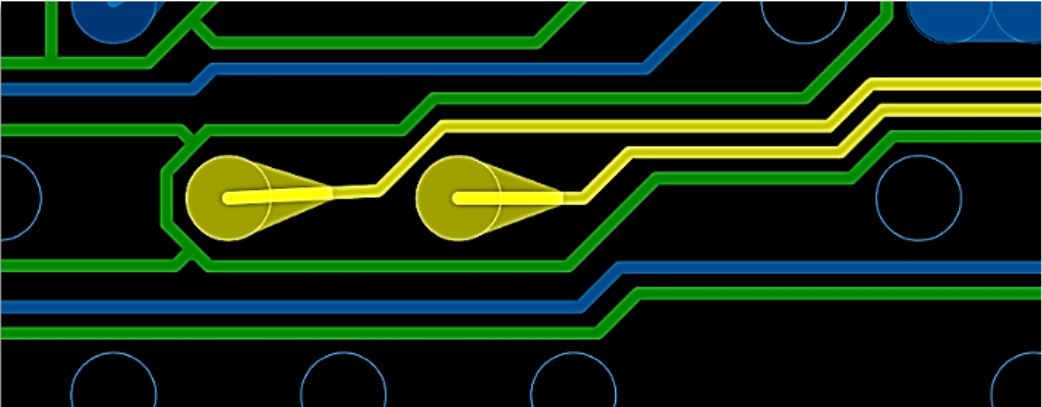

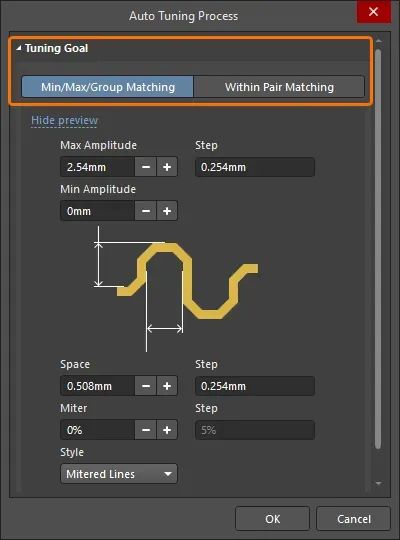

支持屏蔽、差分信号和倒圆角/泪滴插入(见上图)

带有重用结构的预先逃逸布线

基于分片的布线,支持复制

自动电源布线解决方案

混合和匹配 IC 样式及 BGA 样式的电源布线(条纹/轨道和平面)

锁定结构,防止在相邻区域工作时发生变更

可保存的配置,可用于后续设计

根据电源引脚的分组,自动定义形状边界样式(拼图)

综上所述完整流程如下

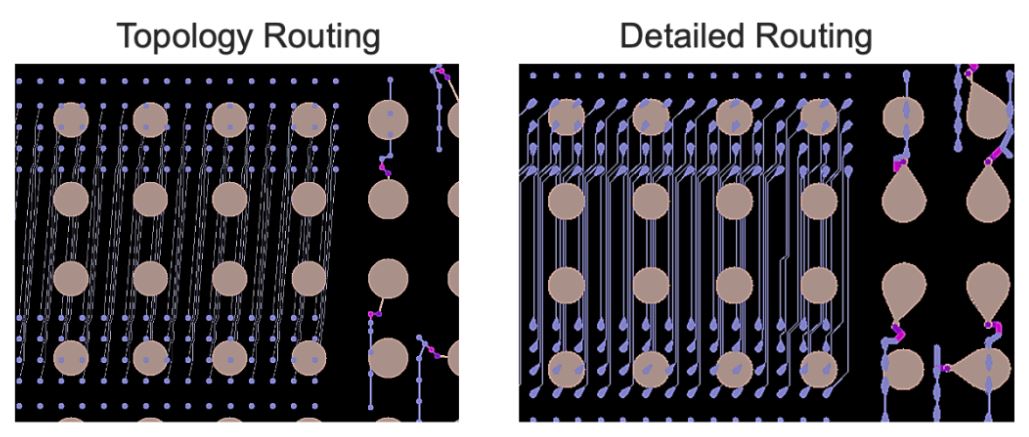

拓扑结构布线

逃逸布线

电源布线

详细布线

模式复制

倒圆角插入

最终 DRC

2、设计结果:大幅提升

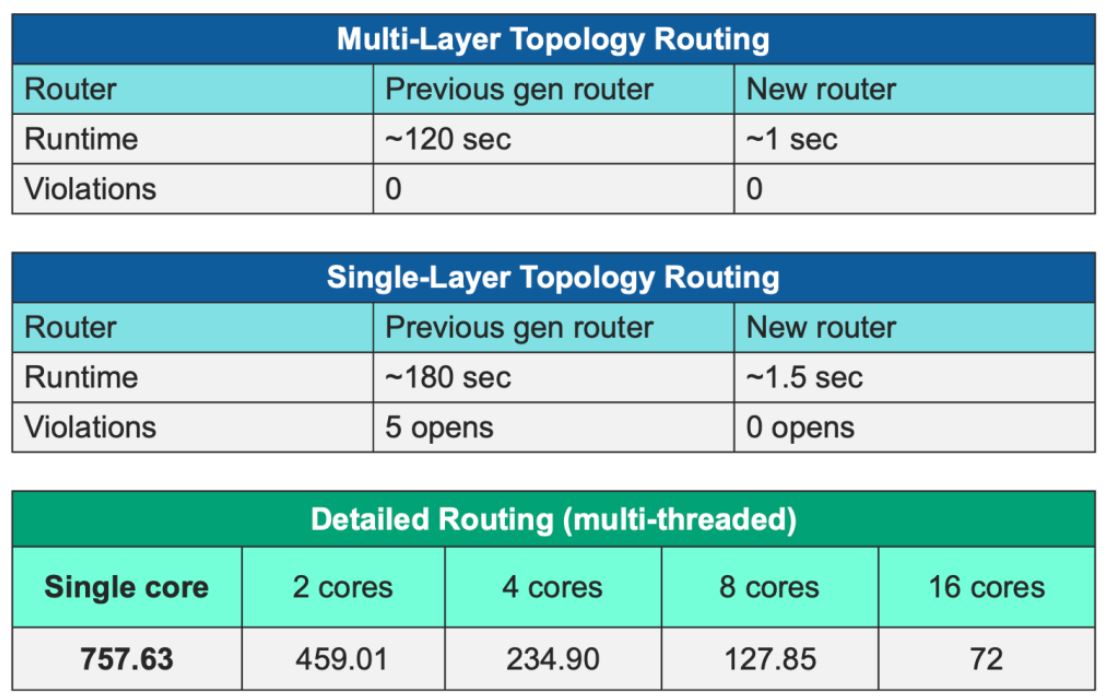

如上表所示,布线速度大大提升(100 倍)。使用多核心多线程详细布线也能使速度提高 10 倍以上。

总结

1.当下普及高级封装技术的主要瓶颈在于布线

2.信号布线(RDL/D2D)和电源布线也是如此

3.需要新一代的解决方案来减少瓶颈并支持大型设计

4.Cadence 和TSMC已经合作开发了用于 InFO 封装技术的新一代信号和电源自动布线工具

原生大规模并行化

结合多种布线技术

便捷的多层布线引擎——Cadence Allegro 工具

支持复制

支持TSMC布线约束和 DRC 规则

审核编辑 黄宇

-

TSMC

+关注

关注

3文章

177浏览量

84494 -

info

+关注

关注

0文章

11浏览量

10175 -

自动布线

+关注

关注

1文章

30浏览量

11570

发布评论请先 登录

相关推荐

ChatGPT新增实时搜索与高级语音功能

如何通过智能布线提升新建筑的功能性?

面向功能安全应用的汽车开源操作系统解决方案

国内市场上一些主流EDA软件功能与性能综合对比

谷歌Tensor G5芯片转投台积电3nm与InFO封装

微软PowerToys修复"高级粘贴"功能BUG,优化设置页面体验

Momenta联合高通基于最新一代Snapdragon Ride平台发布面向先进驾驶辅助和自动驾驶功能的全新智能驾驶解决方案

自动驾驶已成现实?赛思时间同步服务器赋能北京市高级别自动驾驶示范区,为自动驾驶提供中国方案

TSMC-SoIC,InFO,CoWoS之间的关系?

面向 TSMC InFO 技术的高级自动布线功能

面向 TSMC InFO 技术的高级自动布线功能

评论