半导体制程工艺概览

在第一篇的最后,我们说到金属氧化物半导体场效应晶体管(MOSFET)的平面式结构让人们可以在晶圆上同时制造出好几个MOSFET。且与第一代晶体管BJT¹不同,MOSFET无需焊接过程。本期内容就让我们来详细了解一下具体的制程工艺。

为方便讲解,我们先来看一下普通电子零件是怎么制成的。只要拆解身边的任何一件电子产品,我们便不难发现:其基本结构都是把晶体管、干电池、蓄电池和电感线圈等各种单位电子元器件固定在PCB²上,制程工艺可简单概括为“电子元器件的制造 → 电子元器件的固定”。

¹BJT:双极结型晶体管(Bipolar Junction Transistor),即通过一定的工艺将半导体内的P型半导体和N型半导体结合在一起(PN结合)制成的晶体管。

²PCB:印刷电路板(Printed Circuit Board),大部分电子产品采用的一种半导体基板,将电路布置在一个基板上,在其表面上焊接各种电子零件。

图1: 基板上焊接了各种电子元器件。过去,计算机的CPU也采用这种制作方法。(摘自:查看原文)

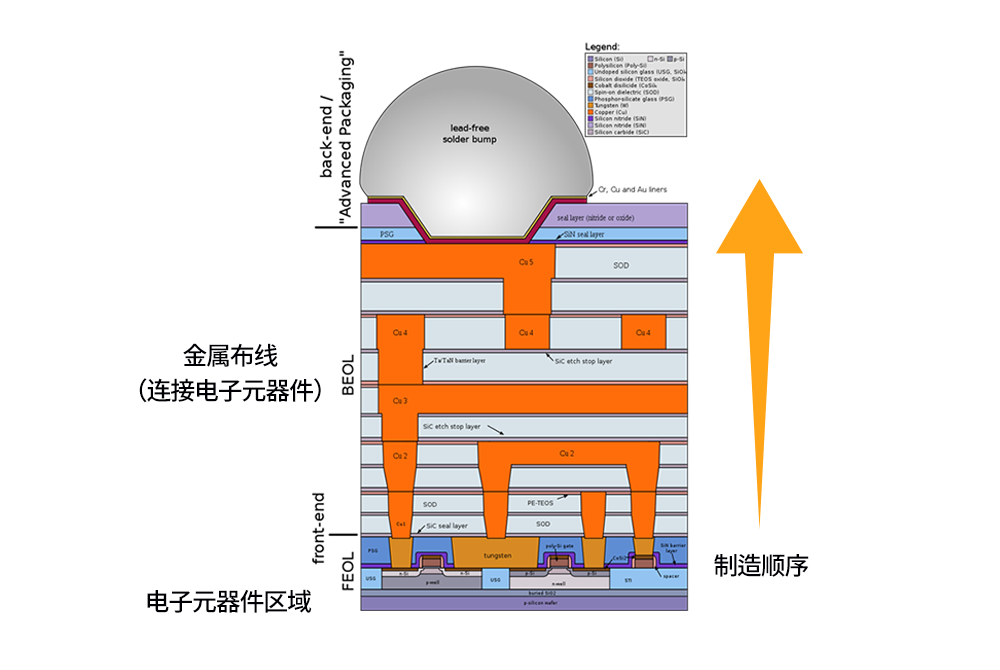

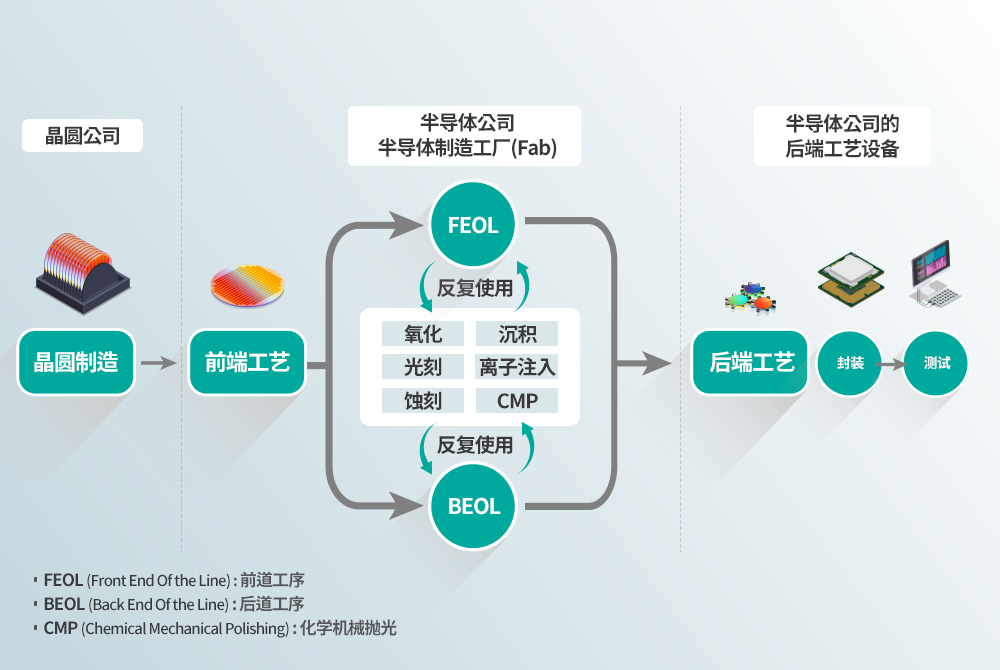

同样,在晶圆上制作 MOSFET时也采用这种顺序。晶圆加工的第一道工艺就是“制造”各种电子元器件。说是“制造”,其实就是通过在晶圆上的各种处理,绘制所需的电子元器件。这一过程我们称之为晶圆加工的前端工艺(FEOL,Front End Of the Line)。随后,我们需要“固定”这些电子元器件。当然,对于这么小的电子元器件,无法使用直接焊接的方式,而是需要采用与FEOL相似的技术,通过金属布线在多达数十亿个电子元器件之间形成连接。这一过程我们称之为晶圆加工的后端工艺(BEOL,Back End Of the Line)。FEOL与BEOL加起来,统称为半导体制造的“前端工艺”。

图2:实际工艺顺序;在FEOL阶段制作MOSFET,然后再以金属布线代替焊接过程,连接FEOL的各种电子元器件。(摘自:查看原文)

接下来我们要逐一讲解的氧化、光刻、刻蚀等都是FEOL和BEOL中的工艺,各工艺的目的不同,使用特定设备的频率和次数也各不相同,但根本目的都是为了绘制繁多而精细的电路。

图3: 半导体制程工艺概览及其相关制造公司

一般来说,我们所知道的半导体制造的八大工艺分别为:晶圆制造、氧化、光刻、刻蚀、沉积、金属布线、测试和封装。但这八大工艺不能一概而论,如上图所示,严格来说,其实晶圆制造并不是在半导体制造工厂内完成的。此外,金属布线、封装和测试,与光刻、刻蚀、沉积等只有单一步骤的工艺不同,是对某个有特定目的的作业流程的统称。

玻璃膜覆盖:氧化

从图2中可以看出,半导体的制程工艺是从下至上的。这一过程并非像堆积木一样简单地把均匀的物质堆积起来就可以。为了把形状各异的物质在半导体内变成均匀的物质,需要经过多道处理工艺,如不需要的部分就要削减掉,需要的部分还要裹上特定物质等。在这一过程中,还会使用各种反应性很强的化学物质,如果化学物质接触到不应接触的部分,就会影响到半导体制造的顺利进行。而且,半导体内还有一些物质,一旦相互接触就会产生短路。氧化工艺的目的,就是通过生成隔离膜防止短路的发生。

氧化工艺就是在硅晶圆上生成一层保护膜。硅(Si)和氧气反应就会形成玻璃(SiO₂)。在我们的日常生活中也能体会到玻璃具有较高的化学稳定性,常用作各种饮料甚至盐酸、硫酸等各种化学药品的容器。在半导体制作过程中,通过氧化工艺形成的氧化膜也同样具有稳定性。它可以防止其他物质的穿透,因此在离子注入3工艺中非常实用。

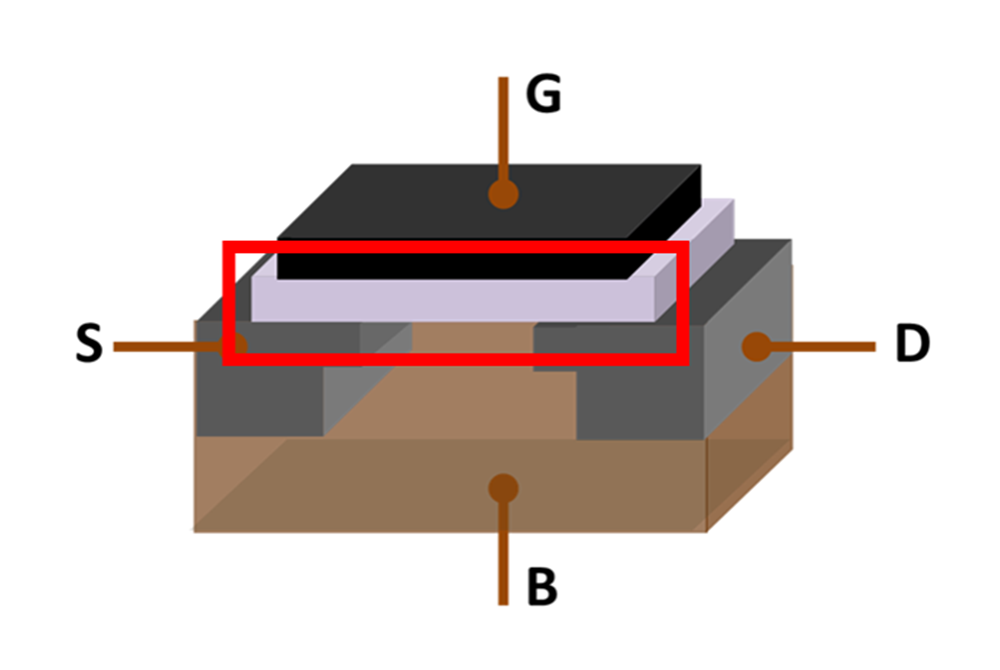

氧化膜还可以用于阻止电路间电流的流动。MOSFET结构的核心就是栅极(Gate)。MOSFET与BJT晶体管不同,栅极不与电流沟道(S与D的中间部分)直接接触,只是“间接”发挥作用。这也是MOSFET不运作时,电力消耗小的原因。MOSFET通过氧化膜隔绝栅极与电流沟道,这种氧化膜被称为栅氧化层(Gate Oxide)。随着最近推出的先进半导体产品体积逐渐变小,它们也会采用 HKMG4等各种栅极绝缘层来取代氧化膜。

3离子注入(Ion Implant):在半导体制造过程中,为把纯净的晶圆变成半导体状态,将三族或五族元素以一定的方式掺入到半导体基片规定的区域内。

4HKMG(High-K Metal Gate): 可有效减少电流泄露的新一代MOSFET栅极;是一种以金属代替传统的多晶矽(Polysilicon) 栅极,以高介电(High-K)取代氧化硅绝缘膜的晶体管。

图4: 栅极(G)与电流沟道(S-D中间)的隔绝物质(红框部分)。过去使用二氧化硅(SiO₂)作为绝缘膜。(摘自:查看原文)

可用作保护膜的并非只有二氧化硅(SiO₂)一种物质。我们还可通过沉积方式覆盖保护膜,或者使用部分已形成的电路作为保护。

氧化工艺使用的是晶圆的组成物质,即通过氧化晶圆的大量硅原子形成保护膜。需要提前说明的是,这一点与后面要说到的“沉积”工艺有所不同。

氧化工艺的种类

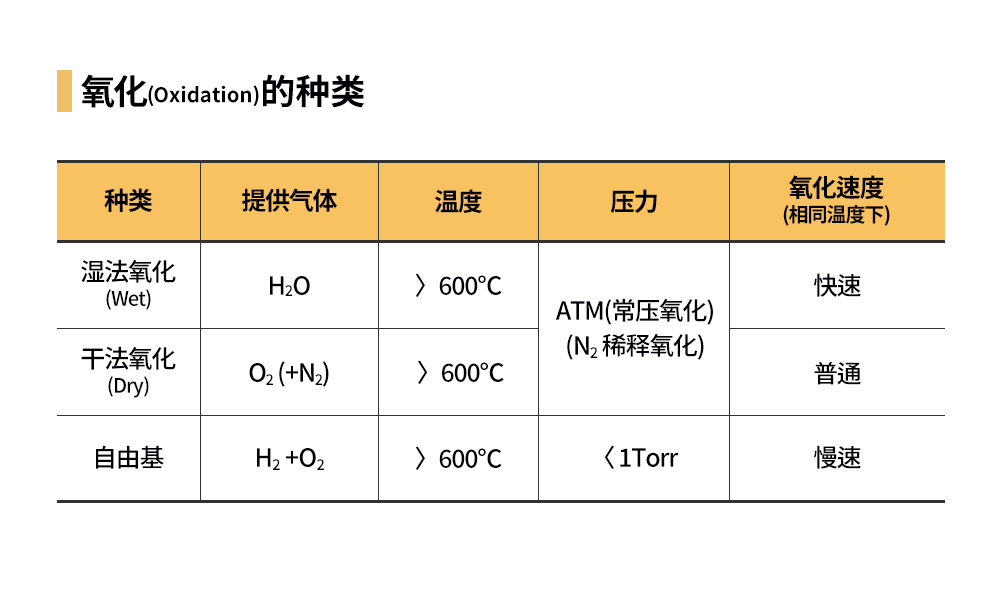

氧化工艺可分为干法氧化(Dry Oxidation)、湿法氧化(Wet Oxidation)和自由基氧化(Radical Oxidation)三大类。

氧化的种类(摘自:(株)图书出版HANOL出版社[半导体制造技术的理解143p])

湿法氧化采用晶圆与高温水蒸气(水)反应的方式生成氧化膜,化学方程式如下。

Si (固体) + 2H₂O (气体) →SiO₂ (固体) + 2H₂ (气体)

这一化学方程式可以简单理解为用高温水让晶圆表面生锈。湿法氧化,虽然氧化膜生长速度快, 但其氧化层整体的均匀度和密度较低。而且,反应过程中还会产生氢气等副产物。由于湿法氧化过程的特性难以控制,在对半导体性能而言至关重要的核心领域中无法使用该方法。

干法氧化则采用高温纯氧与晶圆直接反应的方式。氧分子比水分子重(32 vs 18)5,渗入晶圆内部的速度相对较慢。因此,相比湿法氧化,干法氧化的氧化膜生长速度更慢。但干法氧化的优点在于不会产生副产物(H₂),且氧化膜的均匀度和密度均较高。正是考虑到这种优点,我们在生成对半导体性能影响重大的栅极氧化膜时,会选用干法氧化的方式。

自由基氧化与前两种不同:湿法与干法氧化都是通过提高自然气体的温度来提升其能量,从而促使气体与晶圆表面发生反应。自由基氧化则多一道工艺,即在高温条件下把氧原子和氢分子混合在一起,形成化学反应活性极强的自由基气体,再使自由基气体与晶圆进行反应。由于自由基的化学活性极强,自由基氧化不完全反应的可能性极小。因此,相比干法氧化,该方法可以形成更好的氧化膜。

5假设氢(H)原子的重量为1,氧(O)原子的重量为16,氧(O2)分子的重量就是32, 水(H2O)分子的重量就是18,因此,氧分子比水分子更重。

自由基氧化的特点 [摘自: (株)图书出版HANOL出版社《半导体制造技术的理解149p》]

此外,自由基氧化还可以生成在立体结构上厚度均匀的氧化膜。半导体公司使用的都是单结晶体晶圆,结晶方向相同。

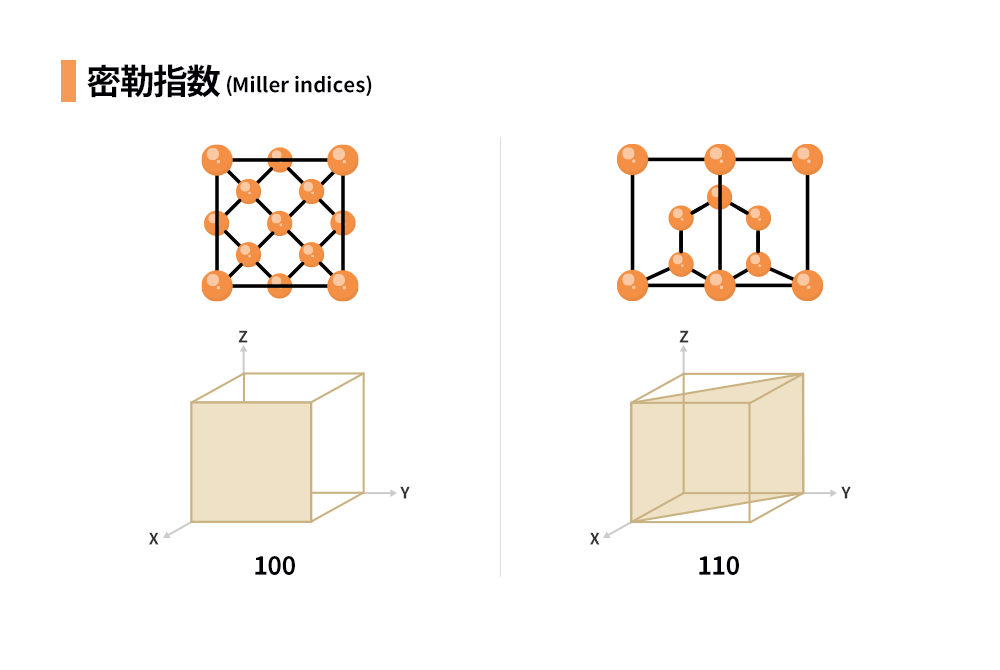

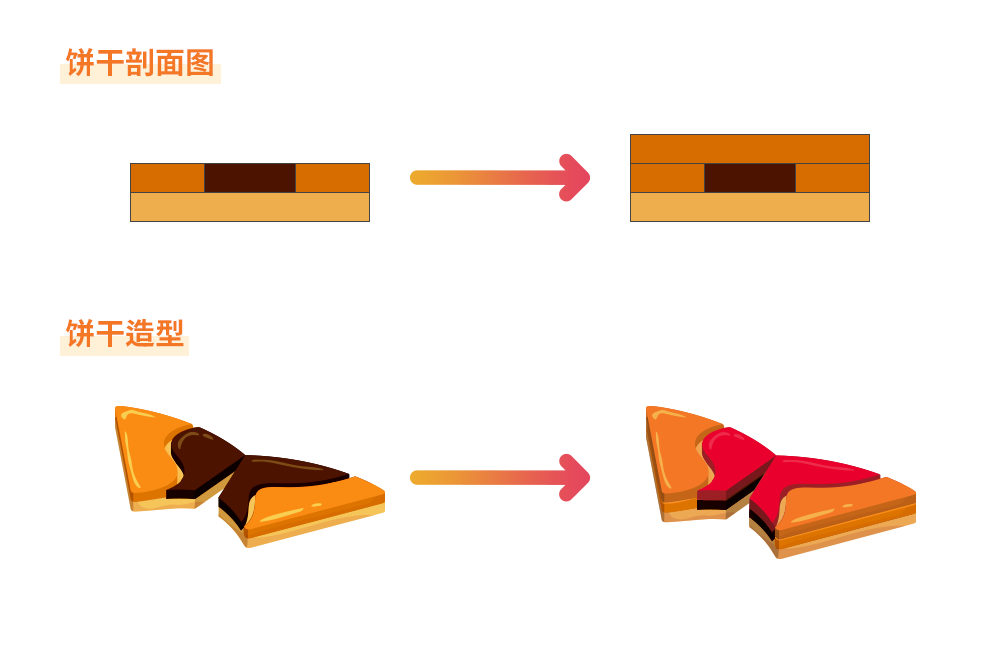

上图中的数字100和110表示硅的结晶方向,下方的两幅图是硅原子的解析图。从图中可以看出,采用湿法和干法氧化时,晶圆上侧(100)方向的氧化膜生长速度相对较慢,而侧面(110)方向的氧化速度较快。由于100方向的硅原子排列更稠密,干法或湿法氧化时,氧化气体很难穿透结晶与硅发生反应,而自由基氧化在这方面则相对容易。

图5:密勒指数(Miller indices)描述的硅原子排列

此外,采用自由基氧化可以在很难形成氧化膜的圆化顶角上形成均匀的氧化膜,在反应活性较弱的氮化硅(Si₃N₄)6中也能“夺取”硅原子,发生氧化反应。

随着半导体微细化难度的增加,半导体公司纷纷开始在半导体内引进三维式结构。因此,能否生成厚度均匀的高品质保护膜变得越来越关键,氧化工艺也更加重要。

6氮化硅(Si₃N₄):氮化硅是保护膜的一种,在半导体电子元器件的制造过程中以沉积方式覆盖在电子表面。

氧化设备的简化结构图

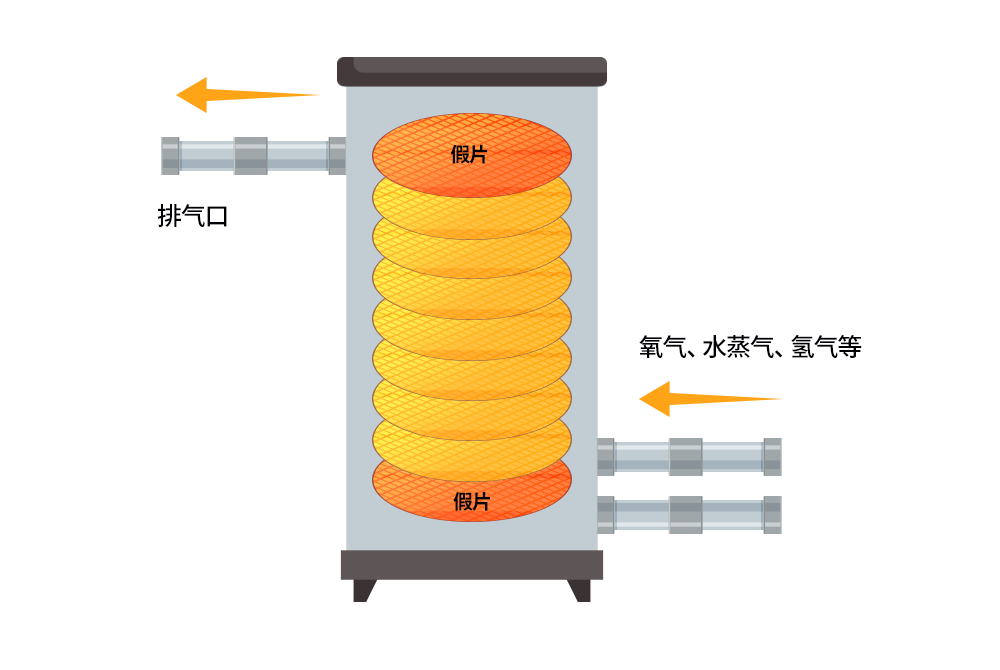

图6是氧化设备的简化结构图,实际的氧化设备要比本图复杂得多。

图6:晶圆氧化设备的结构

通过气体注入口进入氧化设备的反应气体,在被加热后,与晶圆发生氧化反应。为了减少正面接触气体的部分与稍后接触气体的部分间的氧化程度差异,晶圆中掺杂着假片(Dummy Wafer),以利用它们作为牺牲晶片来调整气体的均匀度。从图6中也可以看出,氧化工艺是把数十张晶圆同时放入进行氧化,可见氧化速度是非常之快的。

本期内容我们主要讲了前端工艺的概览和氧化工艺。为帮助大家理解,我们主要采用了大家非常熟悉的八大工艺的结构。但实际上,这些过程也属于半导体扩散(Diffusion)工艺领域,如果按温度划分,还可归类为高温工艺。下一期,我们就一起来了解一下光刻技术,看看如何利用光在晶圆上绘制电路吧。

※本文为外部专家对半导体/ICT的见解,并不代表SK海力士的立场。

文章来源:SK海力士

审核编辑 黄宇

-

半导体

+关注

关注

334文章

27305浏览量

218168 -

制程工艺

+关注

关注

0文章

43浏览量

9434

发布评论请先 登录

相关推荐

半导体工艺讲座

半导体制程简介

半导体制程

半导体制造的难点汇总

半导体工艺几种工艺制程介绍

从7nm到5nm,半导体制程 精选资料分享

半导体前端工艺之沉积工艺

[半导体前端工艺:第二篇] 半导体制程工艺概览与氧化

[半导体前端工艺:第二篇] 半导体制程工艺概览与氧化

![[<b class='flag-5'>半导体</b><b class='flag-5'>前端</b><b class='flag-5'>工艺</b>:第三<b class='flag-5'>篇</b>] 光刻——<b class='flag-5'>半导体</b>电路的绘制](https://file1.elecfans.com/web2/M00/B1/DB/wKgZomVdgPSAWsXlAAH9_6nQJHk959.png)

评论