电路实解

1. 鉴相器

鉴相器是锁相环路的关键部件。在频率合成器中所采用的鉴相器主要有正弦波相位检波器与脉冲取样保持相位比较器两种。

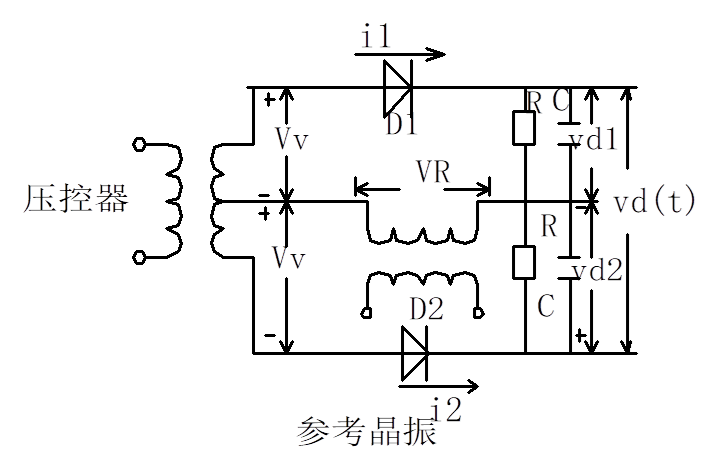

1) 正弦波相位检波器这种鉴相器实际上是一个平衡混频器,它的原理图如下:

但是,它是一种要求平衡度比较高的检波电路,平衡对称性很重要。它容易形成纹波输出,这对数字锁相环路特别不利,因为它将使锁相环路输出混有杂散信号,所以数字式频率合成器常采用下面的脉冲抽样保持鉴相器。

2) 脉冲抽样保持相位比较器

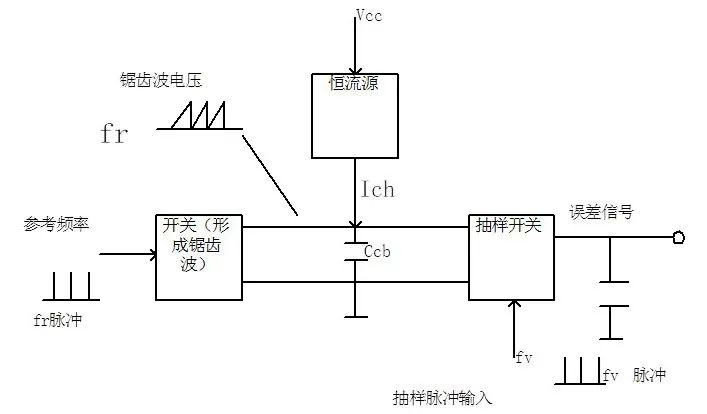

下图为这种相位比较器的基本方框图:

它有以下两个优点:

输出纹波电压小

相位比较可在360°范围内进行

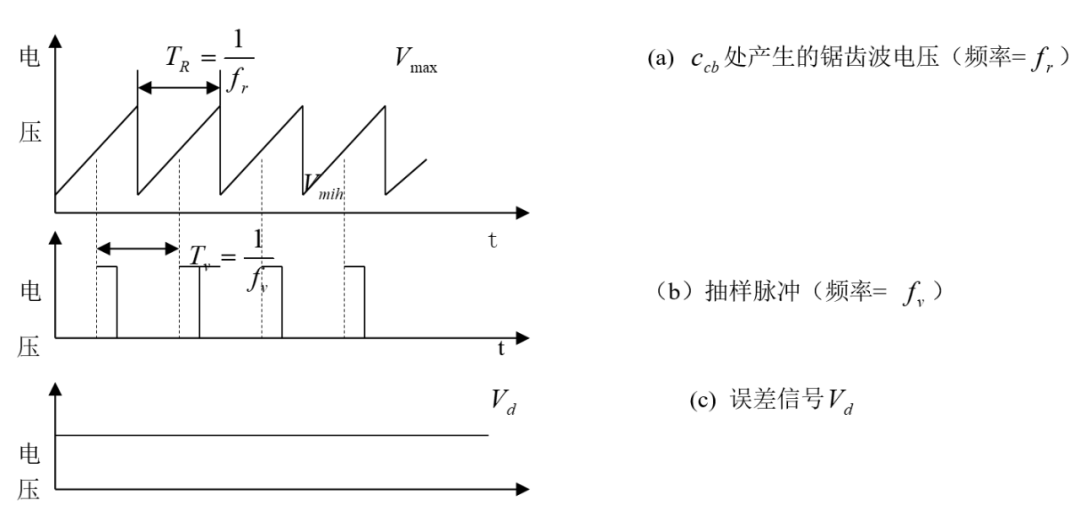

首先,将参考标准频率ƒr和VCO的频率ƒv的电压都形成脉冲。频率为ƒr的脉冲用来控制一个开关电路,使电容Ccb产生周期性的充、放电,形成如下图 (a) 的锯齿形波电压:

由于ƒv=ƒr,显然,抽样脉冲周期Tv与锯齿波电压的周期Tr是相等的。抽样脉冲的作用是控制抽样开关,使它在脉冲存在时接通,因而记忆电容Cd上所获得的电压即等于这一瞬间的锯齿波电压Vd。当抽样脉冲为零时,抽样开关断路,Cd上既保持原充电电压Vd,如图(c)所示。如果VCO频率略有变化(亦即失步时),即相当于抽样脉冲在中心位置略有摆动,这就引起误差电压值Vd的变化,从而控制VCO的频率,使之恢复到准确的数值(即恢复同步)。Vd最大的变动范围可从Vmin到Vmax,相当于抽样脉冲位置变动360°。实际上,锯齿波电压不是如图 (a) 的理想情况(Ccb的放电时间等于零),而是有一定的放电时间的,因而锁相范围小于360°。

2. 电荷泵 (Charge Pump)

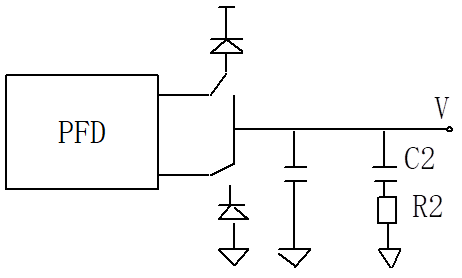

如下图所示电荷泵 (Charge Pump) 示意图:

电荷泵的的作用主要是:给锁相环路提供理想恒定的电流源,保持良好的线性关系,使得频率范围易于控制。图中电容Cp的作用主要是降低杂讯干扰。增加R2主要是保证电荷泵的稳定性。

3. 低通滤波器

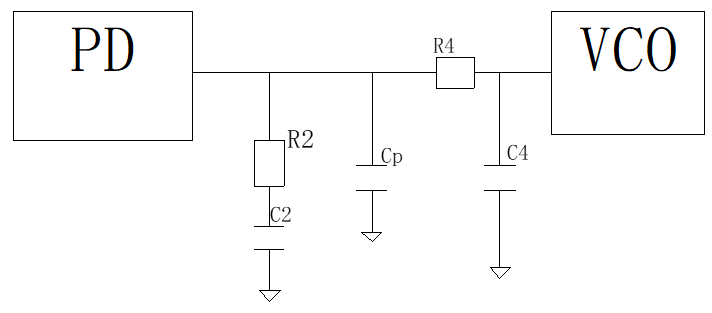

下图是低通滤波器示意图:

图中C4这一阶的作用是进一步降低电荷泵的相位噪声。Cp是保证瞬时特性,使得环路更好得跟踪输入频率的变化。

对VCO的要求:具有高的频谱精度;电压频率具有线性传输特性;频率稳定;低功耗。

4. 闭环传输函数的计算

不同的厂家会提供不同的计算方法,下边是一个经验计算式。

三阶:F1(s) = (1+C2R2)/ s(C2R2Cps+C2Cp)

四阶:F(s) = F1/(1+C4R4s)

设Kv为VCO的增益,Kp为鉴相器的增益,α, β均取经验值3-4。

可由下式计算:

ωc=KvKp/N.(R2C2)/(C2+Cp) 且Cp< 计算得出R2=Nωc/KvCv, C2=α/R2ωc, Cp=1/βR2ωc.

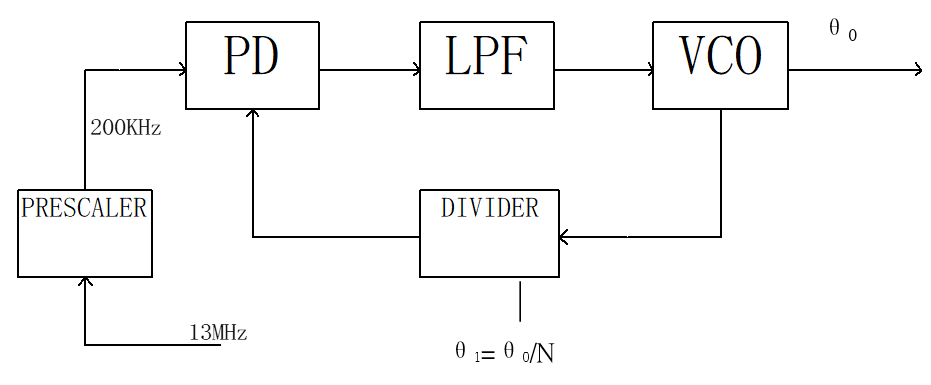

5. 下图为锁相环路的分频

6. LBW及噪声计算

LBW是锁相环的的开环带宽,一般来讲,它是进入鉴相器参考频率的十分之一。由上图可知,13MHz除频后为200KHz,计算得出LBW为20KHz,锁相时间小于577µs。

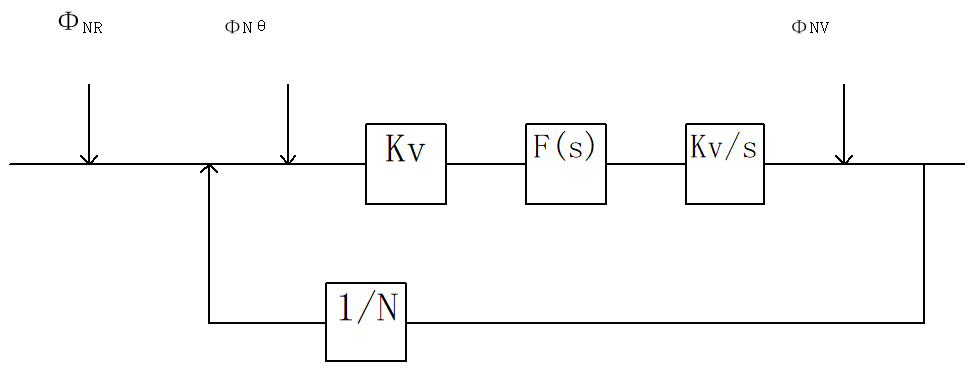

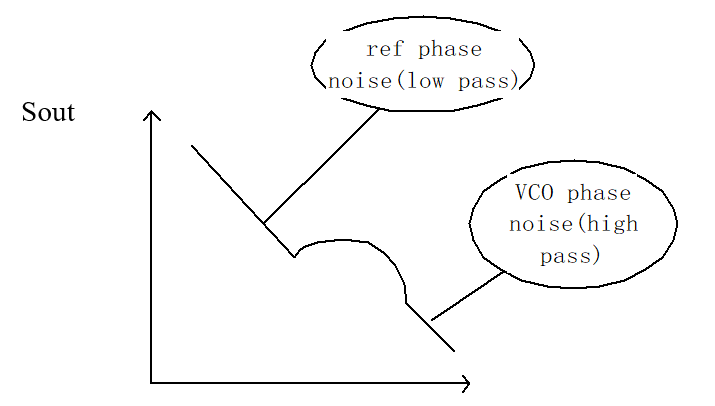

噪声计算如下图:

ΦNr是参考信号的噪声,φNθ是鉴相器带来的噪声,φNv是VCO带来的噪声

φ=KvF(s)(φNr+φNθ)/ s(1+KvF(s)/Ns) + φNθ/(1+KvF(s)/Ns)

= G(z)(φNr+φNθ) + Gr(z)φNθ

G(z)是低通传输函数,Gr(z)是高通传输函数。

典型方案介绍

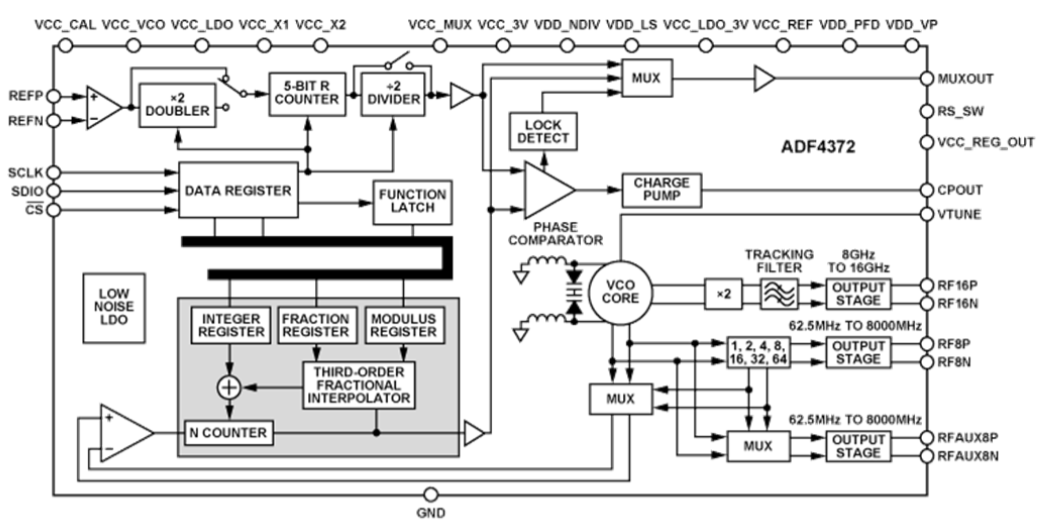

ADF4372 结合外部环路滤波器和外部基准频率使用时,可实现小数 N 分频或整数 N 分频锁相环 (PLL) 频率合成器。宽带微波压控振荡器 (VCO) 设计允许产生 62.5 MHz 至 16 GHz 的频率。ADF4372 具有一个集成 VCO,其基本输出频率范围为 4000 MHz 至 8000 MHz。

此外,VCO 频率连接至 1、2、4、8、16、32 或 64 分频电路,因此用户可以在 RF8x 上生成低至 62.5 MHz 的射频 (RF) 输出频率。RF16x 上的倍频器可生成 8 GHz 至 16 GHz 的频率。RFAUX8x 复制 RF8x 的频率范围,或允许直接访问 VCO 输出。为了抑制不需要的倍频产物,在倍频器和 RF16x 的输出级之间使用了一个谐波滤波器。

片内寄存器均通过三线式接口进行控制。ADF4372 由 3.15 V 至 3.45 V 的模拟和数字电源供电,对于 VCO 电源为 5 V。ADF4372 还包含硬件和软件关断模式。

优势及特点:

RF 输出频率范围:62.5 MHz 至 16,000 MHz,同时支持小数 N 频率合成器和整数 N 频率合成器

高分辨率,39 位小数模数

典型杂散 fPFD:−90 dBc

集成 RMS 抖动:38 fs(1 kHz 至 100 MHz)

归一化本底相位噪声:−234 dBc/Hz

fPFD 工作频率达 250 MHz,基准输入频率达 600 MHz

可编程的 1、2、4、8、16、32 或 64 分频输出

RF8x 和 RFAUX8x 具有 62.5 MHz 至 8,000 MHz 的输出,RF16x 具有 8,000 MHz 至 16,000 MHz 的输出

锁定时间大约为 3 ms 并进行自动校准,锁定时间 <30 μs 并绕过自动校准(典型值)

模拟和数字电源:3.3 V(典型值),VCO 电源电压:3.3 V 和 5 V

RF 输出静音功能

7 mm × 7 mm 48 端子 LGA 封装

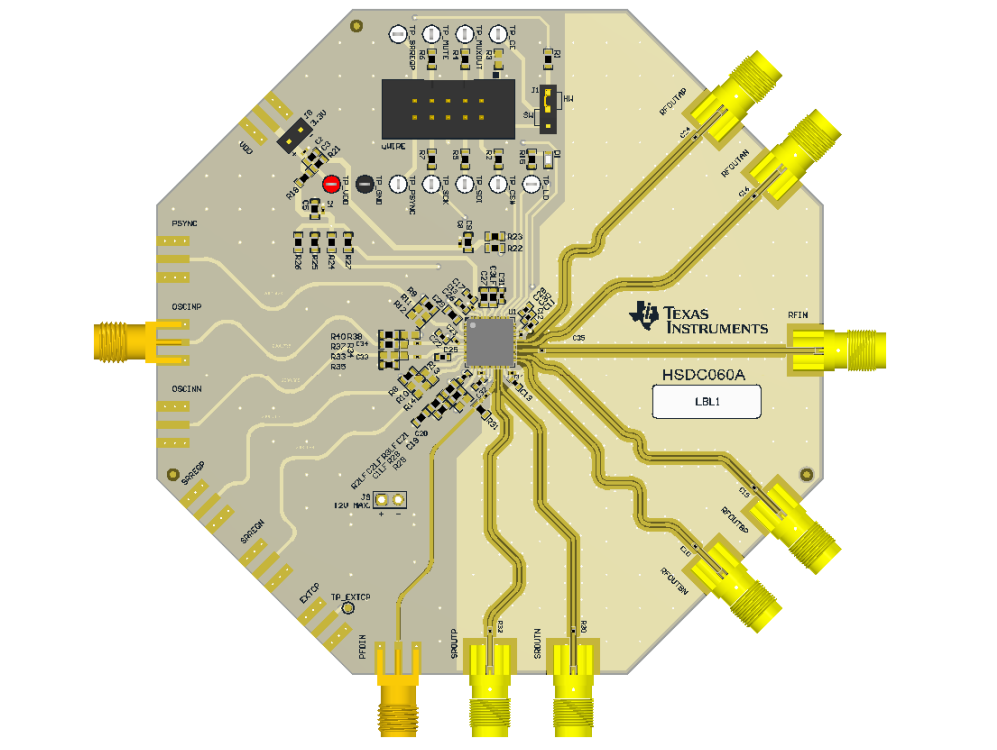

2. TI公司研制的LMX2820方案

LMX2820 是一款高性能宽带合成器,可生成 45MHz 至 22.6GHz 范围内的任何频率。高性能 PLL 具有-236dBc/Hz 的品质因数和较高的相位检测器频率,可实现极低的带内噪声和集成抖动。高速 N 分频器没有预分频器,从而显著减少了杂散的振幅和数量。还有一个可编程输入乘法器,用于减轻整数边界杂散。

LMX2820 允许用户同步多个器件的输出,还支持在输入和输出之间需要确定性延迟的应用。快速校准算法大大减少了 VCO 校准时间,支持需要快速跳频的系统。LMX2820 可以生成或重复符合 JESD204B 标准的 SYSREF,使其可以作为高速数据转换器的低噪声时钟源使用。

该合成器可搭配外部 VCO 使用,此外,还提供直接 PFD 输入引脚,以支持偏移混合,实现低杂散传输。该器件由单个 3.3V 电源供电,并具有集成的LDO,无需板载低噪声 LDO。

以上方案ARROW均有代理,被广泛应用于多载波全球移动通信系统 (MC-GSM)、5G和毫米波无线基础设施 、 微波回程连线 、测试和测量设备、高速数据转换器计时、卫星通信等领域的频率合成、时钟产生和相位管理。同时ARROW可提供配套的底噪声、高可靠性电源方案, 以及配套的高Q值感阻容器件,主要品牌有TI、ADI、NXP、ON、ST等。

审核编辑 黄宇

-

锁相环

+关注

关注

35文章

590浏览量

88050

发布评论请先 登录

相关推荐

锁相环是什么意思

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

锁相环PLL与频率合成器的区别

锁相环PLL的工作原理 锁相环PLL应用领域

数字锁相环固有的相位抖动是怎样产生的,如何解决

简述锁相环的基本结构

锁相环频率合成器的特点和应用

锁相环和锁相放大器的区别

锁相环相位噪声的影响因素

锁相环的工作原理和应用场景

锁相环技术解析(下)

锁相环技术解析(下)

评论