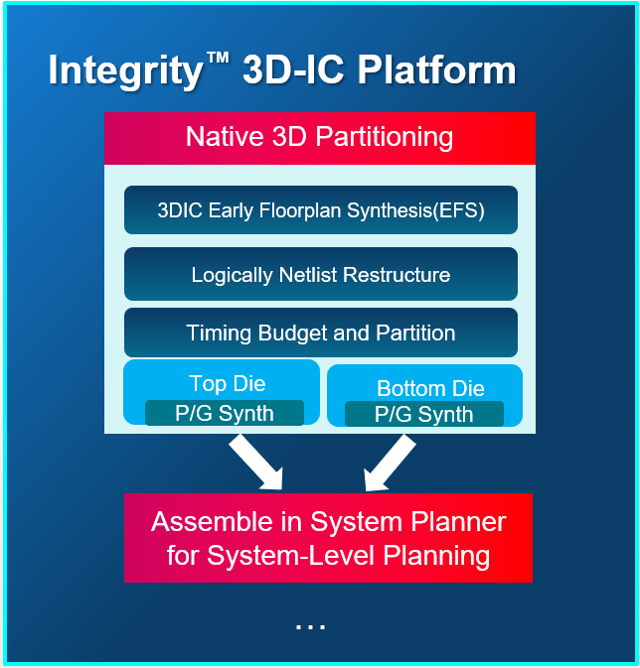

1. Integrity 3D-IC 早期三维布图综合

• 早期布图综合(Early Floorplan Synthesis,EFS)

• 三维布图综合

• 线网长度与芯片间互连信号数目的折中

• 异构芯片的堆叠

早期布图综合(Early Floorplan Synthesis,EFS)

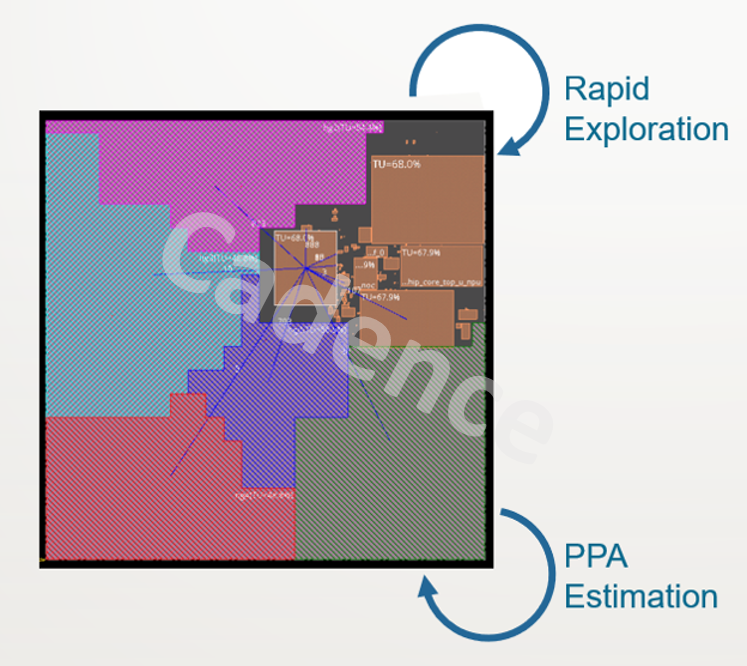

对于大规模的芯片设计,各个模块的布局布线会在 RTL 开始了一段时间之后进行,而芯片顶层的设计规划需要在网表成熟之前就开始,这个阶段的顶层规划往往很难创建,尤其是这个时候各个模块还在不断地优化。所以我们提供了早期布图综合这样一个功能,去自动且快速地进行模块布局,帮助用户在有完整网表、部分网表、甚至还没有网表的时候,对布局进行一系列的探索。

使用 EFS,工具可以做时序驱动的模块布局,优化模块的形状,在满足模块的利用率的前提下,尽量压缩减小芯片面积。同时 EFS 也支持其他约束,包括模块的宽长比、利用率、是否允许直通(feedthrough),以及布线通道的宽度等。

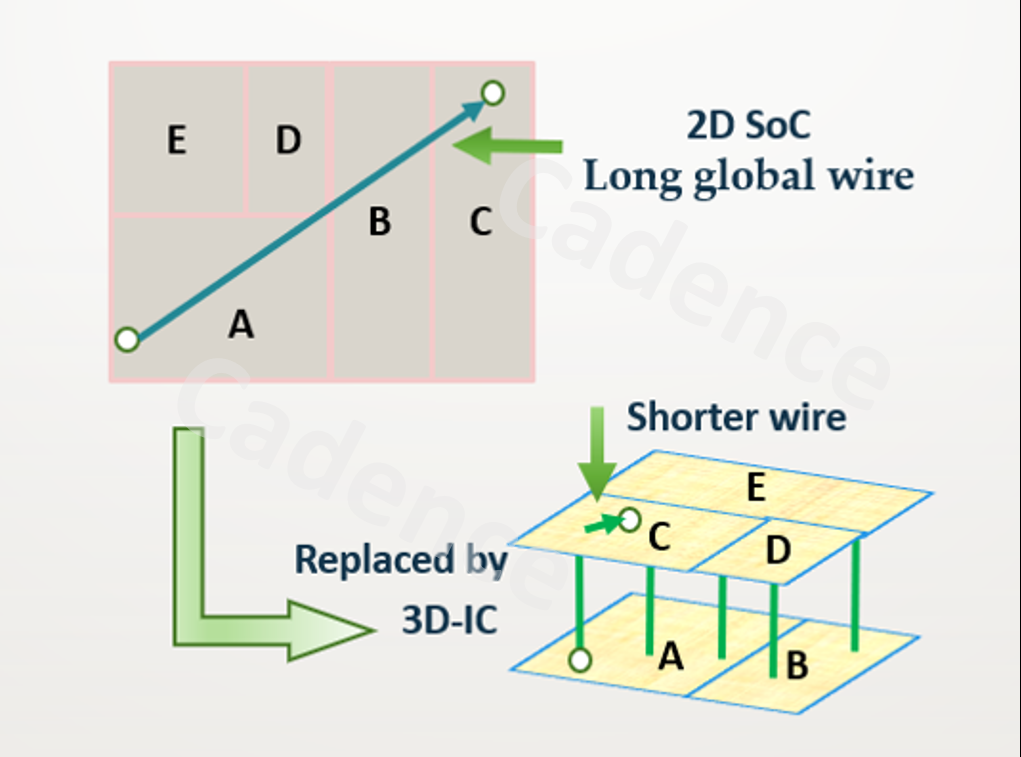

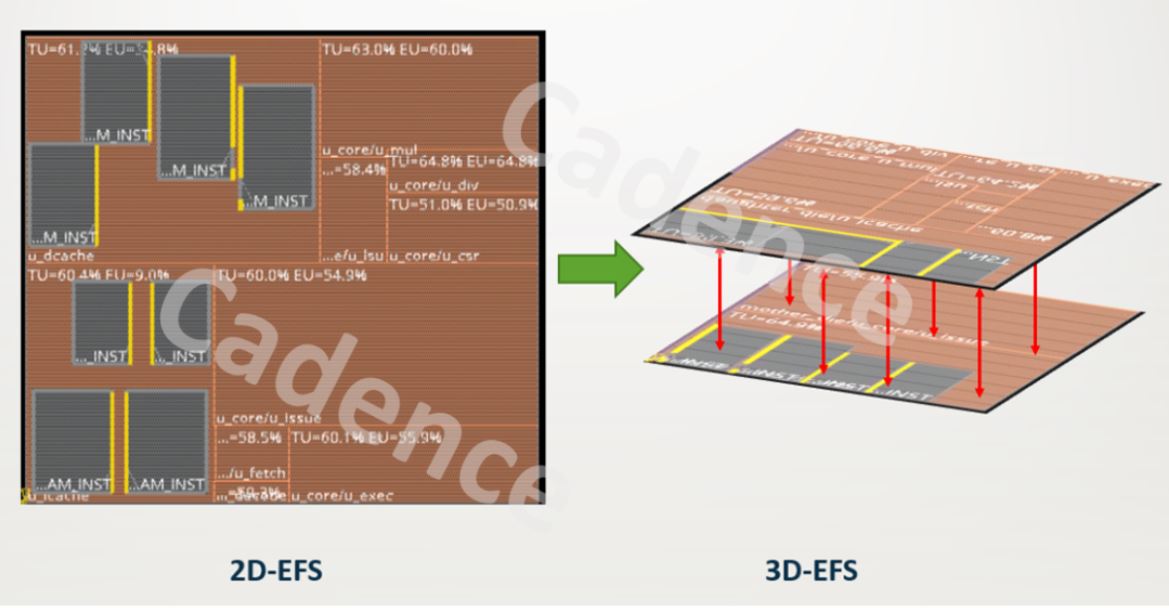

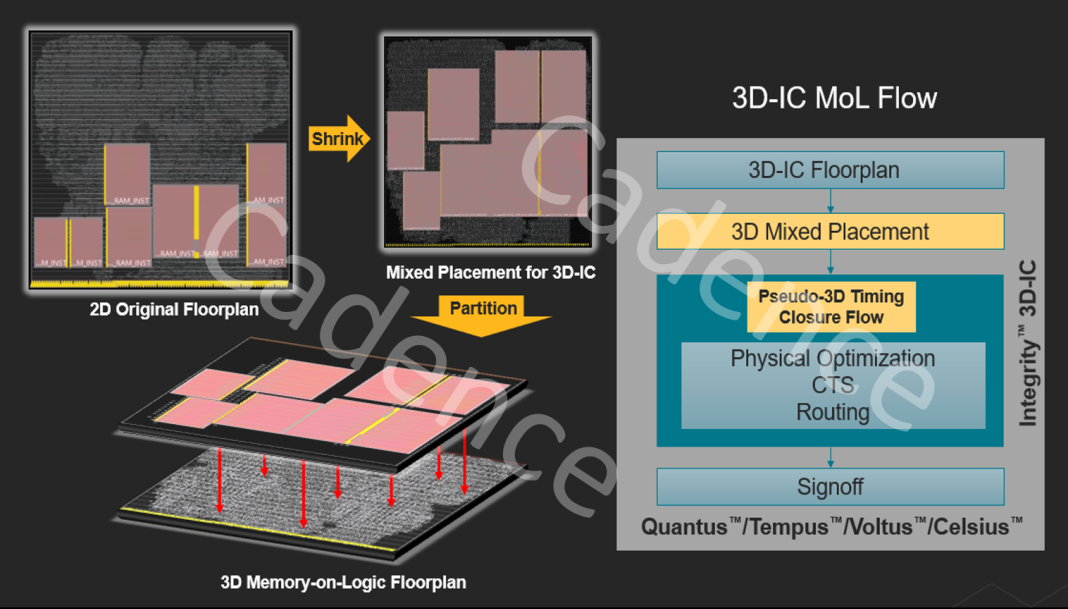

三维布图综合

芯片层数的增加扩大了解空间,使得三维集成电路布图规划更加困难。

基于 EFS,Integrity 3D-IC 进一步增强并推出了三维布图综合功能,在三维空间内对模块进行自动布局,并且进行各模块的形状调整,从而优化芯片面积,线网长度和层间过孔数据。另外,Integrity 3D-IC 还支持用户预分配模块到某层芯片或者预摆放到某个位置。

线网长度与芯片间互连信号数目的折中

减小系统线网长度会不可避免地增加芯片间的互连信号数目。而由于 Bump / TSV 间距以及面积的限制,在做三维布图综合时需要控制芯片之间互连信号的数目。Integrity 3D-IC 可以很好地权衡二者,通过参数调整,帮助用户快速地预览结果并进行三维布局以及分割的探索。

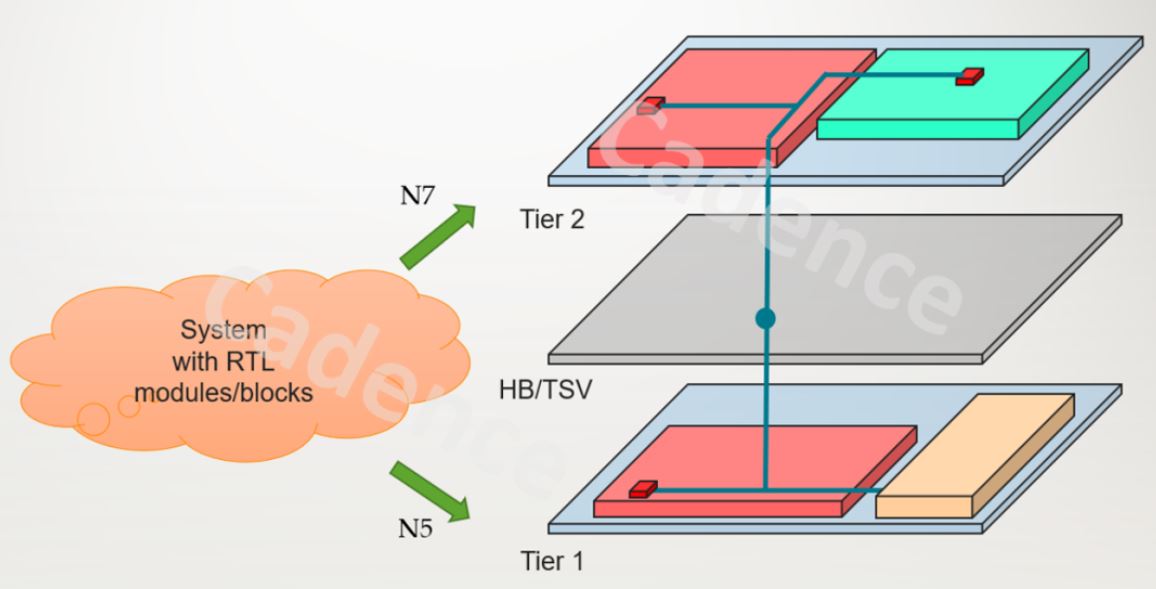

异构芯片的堆叠

把不同制程的逻辑芯片堆叠在一起,既可以满足性能需求,也能有更好的良率及更低的制造成本。Integrity 3D-IC 同样支持异构三维集成电路的布图综合,给不同的模块分配合适的工艺制程。

2. 层次化设计方法

• 层次化结构重建

• 基于逻辑深度的时序预算

层次化结构重建

基于三维空间模块布局的结果,Integrity 3D-IC 会将原来二维的网表进行层次化结构的重建,在系统顶层产生 Top Die 和 Bottom Die 两个层次化结构,把各个模块分配给上层芯片和下层芯片,得到新的三维集成电路的网表。在此过程中,Integrity 3D-IC 可以自动创建上层芯片与封装 PKG 相连所需要的 Feed Through,并且更新系列相关的时序约束信息、翻转计数格式文件等。

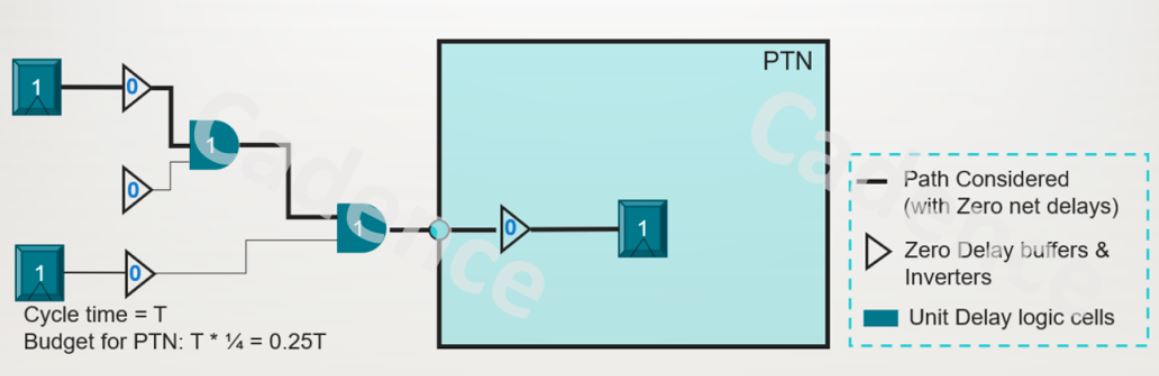

基于逻辑深度的时序预算

在层次化设计流程中,系统的时序约束需要正确地映射到相对应的各层芯片中。在早期,可以通过基于时钟周期的方法做快速的时序预算,给上下层芯片按指定比例分配合适的时序约束文件。为了得到更加准确的时序预算,可以在 Integrity 3D-IC 使用基于逻辑深度的时序预算。基于逻辑深度的时序预算会根据最长的逻辑路径给芯片做好时序的裕量的分配,并且允许用户灵活地对逻辑路径上的组合逻辑单元、时序逻辑单元等设置权重,另外扇出也会被考虑在内。

从设计初始就充分考虑三维实现的自由度能提供最佳系统性能。Integrity 3D-IC 助力架构和布图规划设计师从全局考虑不同模块在三维空间多层级上的逻辑物理分布。通过 Cadence 强大的的层次化早期布图规划算法实现不同单元、模块、IP 在不同层次晶粒的最优分配,将 3D-IC 优势发挥到极致。

- 审核编辑 黄宇

-

集成电路

+关注

关注

5388文章

11544浏览量

361783 -

IC

+关注

关注

36文章

5948浏览量

175578 -

3D

+关注

关注

9文章

2878浏览量

107524 -

芯片设计

+关注

关注

15文章

1019浏览量

54893

发布评论请先 登录

相关推荐

3D-IC设计之系统级版图原理图一致性检查

SMARTSCAN三维扫描仪电子产品配件三维扫描服务

三维可视化的应用和优势

Cadence 凭借突破性的 Integrity 3D-IC 平台加速系统创新

3D园区可视化建模三维有哪些类型,都有哪些功能

3D智慧城市三维可视化的特点

智慧园区可视化三维大屏展示综合管理平台的价值

工业工厂3D沉浸式三维数字化管理系统

Integrity 3D-IC早期三维布图综合功能

3D-IC未来已来

产品资讯 | 3D-IC 设计之自底向上实现流程与高效数据管理

3D-IC 设计之早期三维布图综合以及层次化设计方法

3D-IC 设计之早期三维布图综合以及层次化设计方法

评论